对于 DSP、CPU、GPU、FPGA等高性能处理器而言,确保其各模块所需电源的上电顺序对实现其可靠运行、提高效率并保障整体系统健康至关重要。

2025-07-16 13:49:20 3076

3076

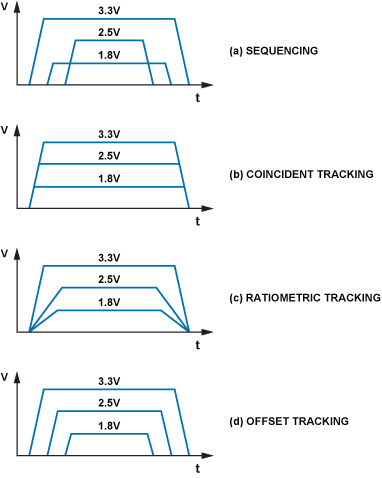

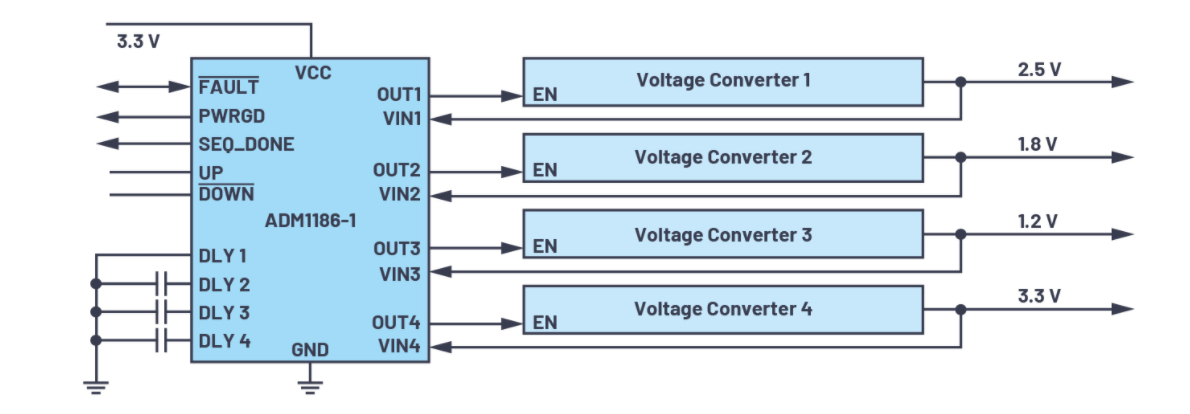

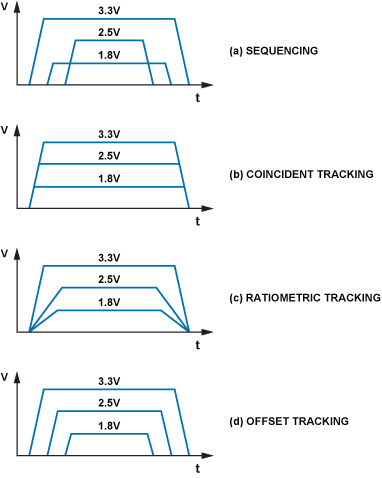

本文讨论如何针对FPGA或微处理器配置各种电压输出跟踪和时序控制选项,来帮助实现灵敏多电源轨系统的正确启动和关断。

2015-07-22 17:30:27 1570

1570

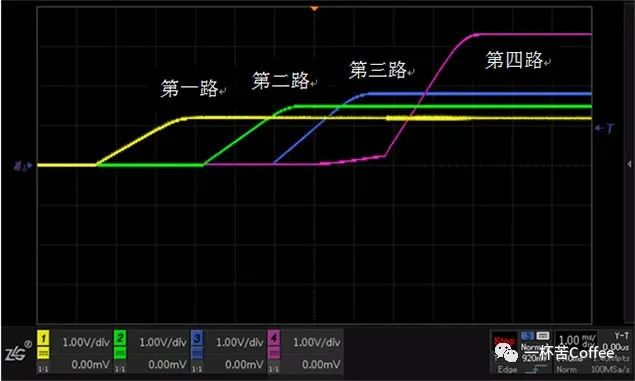

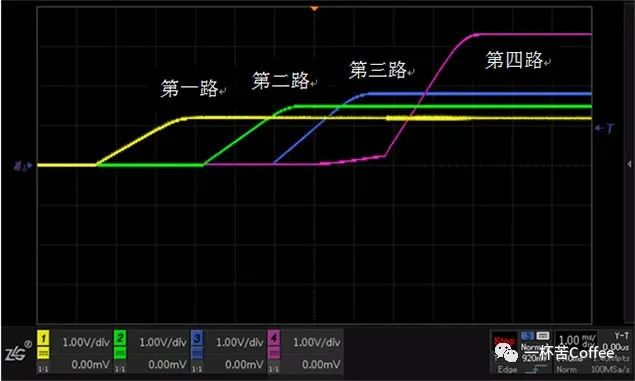

为什么电源纹波不能直接一键捕获呢?为什么多路上电时序前后分析对比这么麻烦呢?

2017-04-19 10:42:54 8098

8098

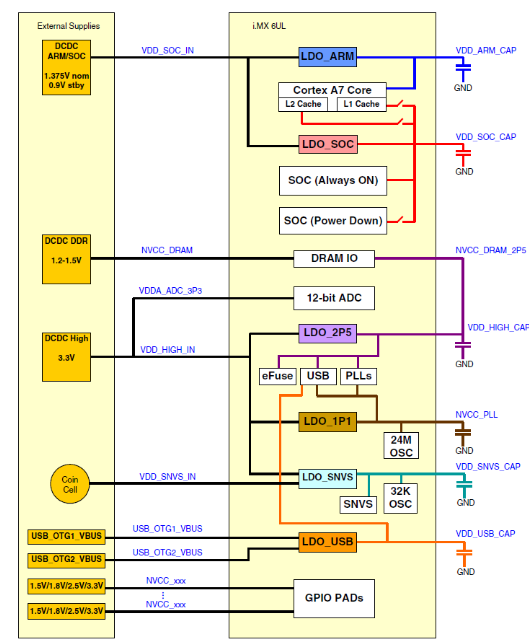

为确保芯片能可靠的工作,应用处理器的上下电通常都要遵循一定时序, 本文以i.MX6UL应用处理器为例,设计中就必须要满足芯片手册的上电时序、掉电时序,否则在产品使用时可能会出现以下情况,第一,上电

2018-05-16 18:03:32 8364

8364

大多数FPGA芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常的运行。

2019-07-01 17:16:45 17573

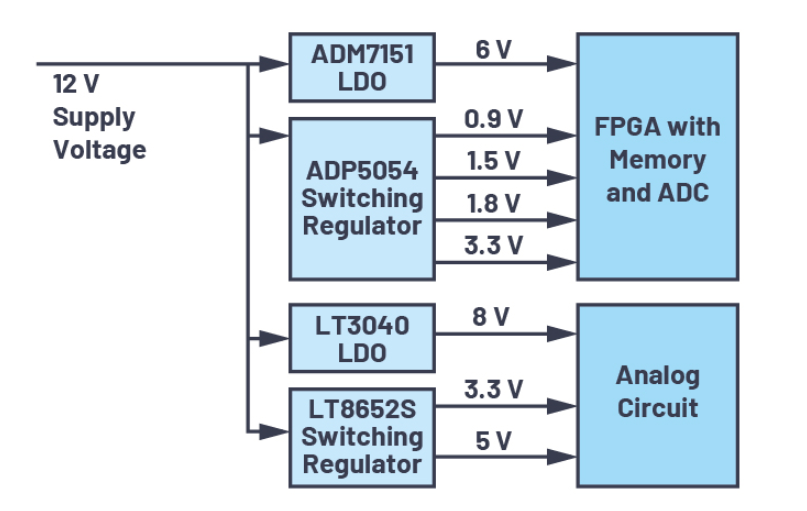

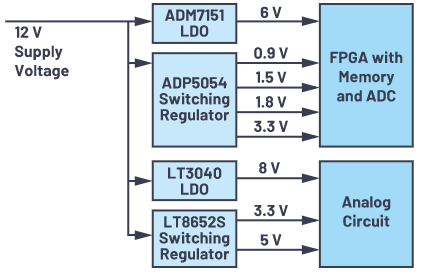

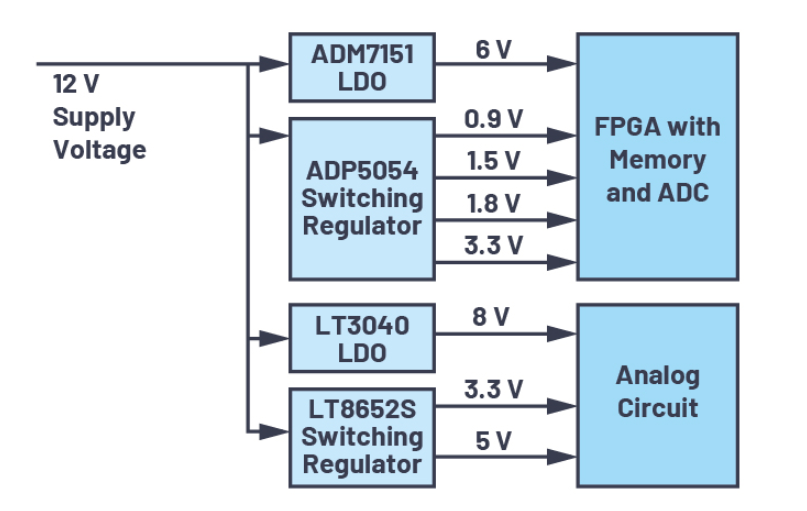

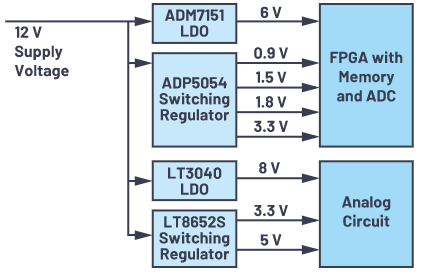

17573 微处理器、FPGA、DSP、模数转换器 (ADC) 和片上系统 (SoC) 器件一般需要多个电压轨才能运行。为防止出现锁定、总线争用问题和高涌流,设计人员需要按特定顺序启动和关断这些电源轨

2019-08-26 10:33:10 8692

8692 专题文章:了解蓝牙技术的可靠性。在这篇深入探讨蓝牙可靠性的文章中,Woolley解释了蓝牙技术如何在无线电的基础上建立可靠的连接。 在无线的基础上创造可靠性 蓝牙设备的通信效果非常好,原因在于蓝牙通信系统所使用的无线电及其协议等设计的诸多方

2021-04-01 16:12:02 5243

5243

对于每个转换器,各电压上电的延迟也会不同。这导致不同电压域中的电压爬升不受控制,有可能引起功能问题并损坏系统。

2021-03-24 10:34:46 3264

3264

目前,大多数FPGA芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常的运行。

2022-10-24 14:52:00 1224

1224 目前,大多数 FPGA 芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常

2022-12-26 18:10:00 3584

3584 RK3588-MIPI屏幕调试笔记:RK3588-MIPI-DSI之LCD上电初始化时序

2023-06-10 10:32:54 7913

7913 上电时序(Power-up Sequeence)是指各电源轨上电的先后关系。 与之对应的是下电时序,但是在电路设计过程中,一般不会去考虑下电时序(特殊的场景除外)。今天,我们主要了解一下上电时序控制相关内容。

2023-12-11 18:17:05 5626

5626

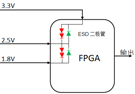

之前上电,不过有些设计可能要求采用其他序列。正确的上电和关断时序控制可以防止闩锁引起的即刻损坏和静电放电(ESD)引起的长期损坏。另外,对电源实施时序控制还可在上电

2024-06-26 08:24:10 1861

1861

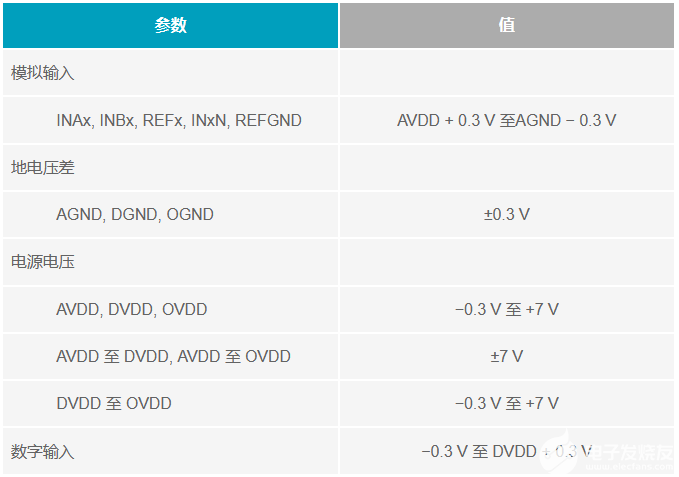

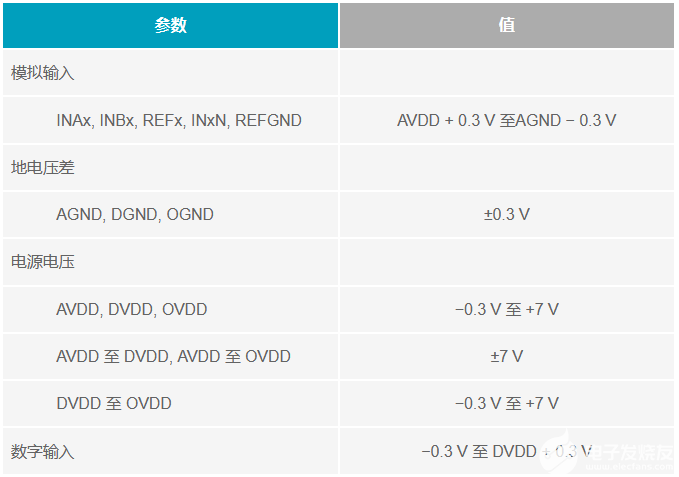

1、关于ADS8698有上电时序要求吗?AVDD和DVDD 以及软件配置引脚间的顺序有时序要求吗?

2、触发内部基准电压的条件有哪些?AVDD?还是有别的触发源,如果内部基准触发不了,会有什么现象

2024-11-19 06:12:49

相对于其他上电模式,这种上电模式对处理器的性能是否有限制,如工作频率的限制。2. 图示中VDD_CORE和VDD_MPU都是1.1V的,若两者电压不同该如何上电。3. 上电时序的间隔时间是否有严格要求,Datasheet中未给出相关数据。

2018-06-04 06:24:11

请问能提供C6678上电芯片时序控制,以及配置端口电平和时序的Verilog代码吗?

2018-06-21 04:32:03

入任何时序操作时(注:NC管脚悬空),上电后Vout没有模拟输出,与预想上电默认输出值3.3v不同。

以上为现象描述。

在此想确认DAC161S055在上电后不加任何时序操作,Vout是否输出上电值引脚(MZB)所接的电平值?

请尽快回复,谢谢。

2025-02-08 08:01:57

入任何时序操作时(注:NC管脚悬空),上电后Vout没有模拟输出,与预想上电默认输出值3.3v不同。

以上为现象描述。

在此想确认DAC161S055在上电后不加任何时序操作,Vout是否输出上电值引脚(MZB)所接的电平值?

请尽快回复,谢谢。

2025-02-10 08:31:44

为什么有不同的上电时序

2023-11-02 08:13:09

如果要求输出是vdd=3.3v,我是不是可以这样设计上电顺序:首先设置Vgg=-2V,再VCtrl=1V,再Vdd=3.3V,然后调节Vgg,使Igg=140mA,那么它们之间的上电时序是如何控制的。

2023-11-22 07:14:57

上运载一个时钟频率 fPP 时,这个插入的卡必须要正确地复位(重置)。如果这个热插入特性是在主机内实现的,则该主机要经得起 VDD 和 VSS 之间短路而不损坏。上电时序如图:(SPI模式不支持CMD15,详见SD/MMC card 命令)

2012-01-12 11:06:39

按照TAS5711的datasheet中的上电时序进行上电,芯片正常工作,但是无法编辑寄存器,是时序有问题吗?我是按照这个上电时序来上电的:AVDD/DVDD上电(3.3V),上电之前A_SEL

2019-08-07 10:02:22

电路,并解决了TPS65105的上电时序问题。实践表明,该方案是一个稳定可靠的TFT液晶的电源设计方案。 0 引言 TPS65105 是一个混合式DC/DC变换器集成电路芯片。它专门为薄膜式晶体管

2018-09-29 17:01:44

0-50ms,我特意测试了一下DEMO板上的5个电压上电时序,根据截图可见实际并非如手册上讲的那么严格,截图是两两比较的,前级为黄色,后级为红色。截图在附件似乎只要前面4个满足要求,0.9V都不是很重要,看

2018-05-25 04:36:15

使用TPS65218给ZYNQ7010供电时官方给出的方案是DCDC1和DCDC2给ZYNQ供1.0V,DCDC3供1.5V,DCDC4供1.8V,但是ZYNQ电压启动时序中要求1.0V上电时序最早

2016-07-08 16:29:24

ZL6205是如何保障MCU可靠上电的

2021-03-11 06:45:33

1.问下aurix的TC397的上电时序要求是怎样的呢?

2.有看视频说TC3XX系列没有上电时序的要求,但是在Errata手册里看到,又有VDDM和VDD上电时间要求,否则会导致lock,能帮忙确认下AURIX TC397系列的上电时序要求吗?

2024-06-04 09:39:55

称为电源时序控制或电源定序,目前有许多解决方案可以有效实现定序。对于需要电压定序的复杂器件,其内核和模拟模块的电压轨可能需要在数字 I/O 电压轨之前上电。有些设计可能会要求不同的顺序,但是

2019-07-30 10:43:06

情况下的行为表现(参见表2),分析可能的问题及原因,并提出一些建议。上电时序问题多种多样上电时序问题可能出现于多种不同情况。例如,在一个客户应用中,AD8616配置为缓冲器,在电源建立之前输入为0 V(图

2018-05-09 16:32:40

使用软件iic通讯测试过,写的软件通讯协议没问题,寄存器驱动也按照手册写好了,但是读取中断状态寄存器的电源就绪位置,一直为零,我不知道这个上电顺序到底是什么

2024-08-09 18:06:48

本帖最后由 buhuile 于 2017-6-12 23:17 编辑

用安捷伦示波器测量上电时序或者掉电时序时,触发电平和时间怎么设置?时间设得不对,抓到的波形是不对的

2017-06-12 23:16:14

用安捷伦示波器测量上电时序或者掉电时序时,触发电平和时间怎么设置?时间设得不对,抓到的波形是不对的.

2017-06-17 14:41:18

电路被关断或电源被关断,系统中只有值守电路在工作。因此,静态运行下的系统不存在软件的可靠性问题,其可靠性主要表现在值守电路的抗干扰能力、系统中器件的静态参数余度,如直流特性参数余度、工作电压、工作稳定

2021-01-11 09:34:49

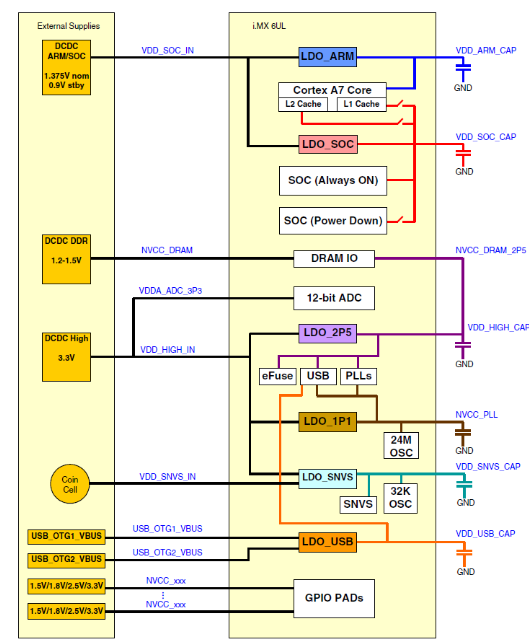

为确保芯片能可靠的工作,应用处理器的上下电通常都要遵循一定时序, 本文以i.MX6UL应用处理器为例,设计中就必须要满足芯片手册的上电时序、掉电时序,否则在产品使用时可能会出现以下情况,第一,上电

2019-10-18 07:53:02

。无论如何,正确的上电和关断时序控制可以防止闩锁引发的即时损坏和ESD造成的长期损害。此外,电源时序控制可以错开上电过程中的浪涌电流,这种技术对于采用限流电源供电的应用十分有用。 本文讨论使用分立器件

2018-09-30 16:01:35

LM3881芯片的在上电后不启用,在电路某个点的电压输入后再启用,可以通过控制EN引脚还是别的脚来实现?该如何实现芯片的关断和打开功能?假如有个引脚可以控制芯片使能,假如拉低是使芯片无法使用,那上电后还是低,等电路某部分连接后,让它启用时序,改变状态。

2019-07-31 11:17:18

如何实现对DTS中mipi屏幕上电时序的获取及其发送呢?其程序代码该怎样去实现呢?

2022-02-16 07:35:45

按照TAS5711的datasheet中的上电时序进行上电,芯片正常工作,但是无法编辑寄存器,是时序有问题吗?

我是按照这个上电时序来上电的:AVDD/DVDD上电(3.3V),上电之前A_SEL

2024-10-22 06:58:25

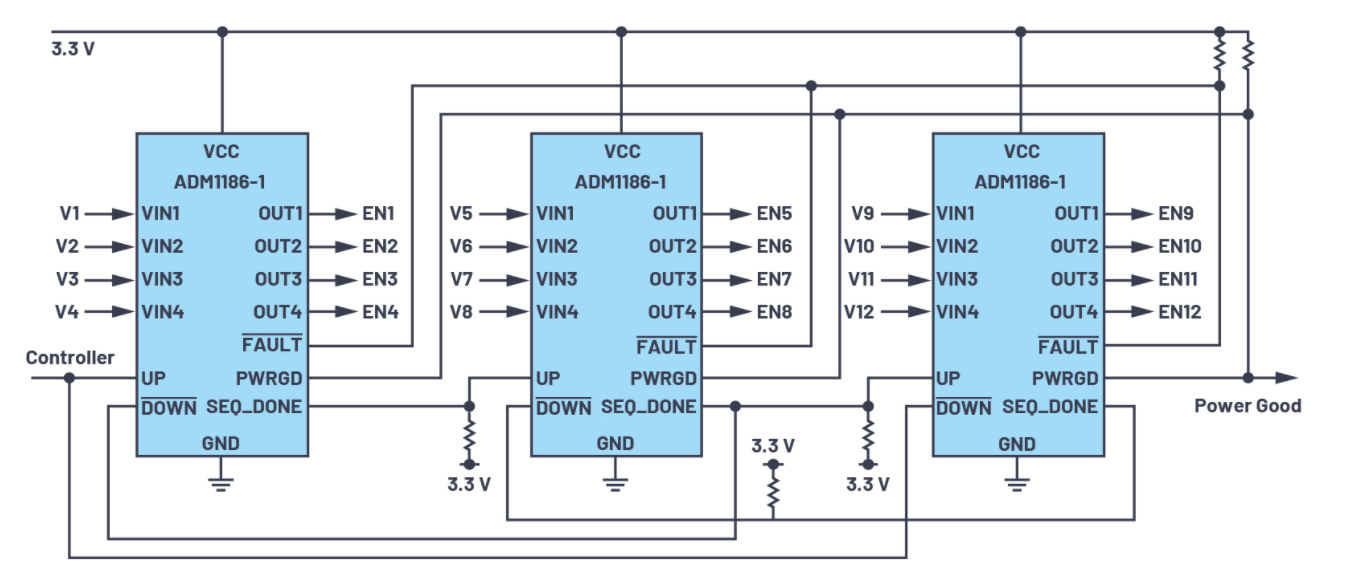

IC的可能性,但它们仅支持各个电压的受控斜坡上升,而不支持这种菊花链星座中的受控关断时序(即电压关断)。图3.多个ADM1186-1器件链接在一起,可控制12个电压的上电和关断时序可靠且受控的上电

2021-04-12 07:00:00

Hi,你好,想请问下关于AD2S1210的上电初始化时序问题,

1、硬件复位引脚RESET引脚如果在VDD达到规定电压之前没有存在低电平的时间,会出现什么问题?

2、硬件复位引脚RESET引脚在

2023-12-06 06:55:32

输出电压正常。现在想配置上电时序,1V>1.8V>3.3V,按照器件手册的图33设计的电路原理图,设计原理图如下

使用电压跟踪功能后,1.8V电压输出为1.6V,3.3V输出2.85V。请问这是什么原因导致的

2025-04-18 06:22:54

有一个项目中用到OPA192这个放大器,有两个问题:

1.V+是+12V供电的,V-是-12V供电的,想问下+12V和-12V这两个电有没有什么必须的上电时序需要控制?

2.还有就是我的项目

2024-07-29 08:30:16

现在的FPGA还严格要求上电时序吗?想请教一下大家

2017-09-26 15:39:07

工程师以为是软件的问题,花费了很大的时间和精力来找BUG,问题仍然没有很好的得到解决。后来查翻手册发现,发现该系列的MCU对于上电时间是有一定要求的(其实几乎所有品牌的MCU都有上下电时序要求)。图1

2019-09-01 07:00:00

启动和关断这些电源轨。此过程称为电源时序控制或电源定序,目前有许多解决方案可以有效实现定序。对于需要电压定序的复杂器件,其内核和模拟模块的电压轨可能需要在数字 I/O 电压轨之前上电。有些设计可能会要求...

2021-11-12 06:01:50

。无论如何,正确的上电和关断时序控制可以防止闩锁引发的即时损坏和ESD造成的长期损害。此外,电源时序控制可以错开上电过程中的浪涌电流,这种技术对于采用限流电源供电的应用十分有用。 本文讨论使用分立器件进行

2019-07-03 08:15:19

钩:和上电时序有一定关系... 3. 上电回沟的问题,如果你认为你的上电时序设计的没问题,那么还要考察一下芯片自己的问题,打个比方,芯片有3.3V和1.5V的输入,1.5V先上电, 3.3V后上电,现象是 3.3V...

2021-12-31 06:59:38

你好,AD7982的VREF与VDD/VIO之间是否有时序要求?手册里没查到。在目前我们的设计中,VREF(5V)先于VDD(2.5V)和VIO(2.5V)上电,不知是否会有问题。谢谢。

2019-01-08 13:56:41

。2、测量±13V电源的上电时序,发现-13V上电略早于+13V几十ms,调整-13V上电到略晚于+13V几十ms后,运放初次上电后也输出为0V左右。综合以上现象,初步判断ADA4522-2对电源的上电时序比较敏感,请问这个现象是正常的吗?之前同样电路用过几种其他的运放,都没有出现过这样的问题。

2018-08-14 07:20:54

本帖最后由 一只耳朵怪 于 2018-6-21 11:05 编辑

你好:AM5718上电时序不对,会烧AM57188吗?

2018-06-21 06:39:46

F28377D需要3.3V和1.2V, controlsuite里用 TPS64240为芯片供电,请问这两个电压有没有上电先后时序?

2018-11-23 09:42:13

请问fx3有上电时序要求吗

2025-05-09 07:29:38

有哪位大神能帮我看看着上电时序怎么看啊,都看不懂

2018-09-04 22:07:05

我用ucc27324这片驱动芯片给驱动,分别给低边的MOS和高边的MOS驱动。高边的MOS和驱动芯片之间已加隔离变压器和隔直电容,但是占空比很小,所以关断时候负压很小,总是会被误触发。低边的MOS关断时候是零电压,也不可靠。有没有什么办法在改动很少的情况下加上可靠的负压关断(至少-2V)?

2019-06-27 09:12:37

为什么电源纹波不能直接一键捕获呢?为什么多路上电时序前后分析对比这么麻烦呢?为什么分析调制信号时波形对比度这么差呢?事实上,用户的每一次体验感,都是产品隐形的提升空间。以上这三个麻烦,现在也许有了

2018-12-03 11:17:59

些设计可能需要采用其他序列。无论如何,正确的上电和关断时序控制可以防止闩锁引发的即时损坏和 ESD 造成的长期损害。此外,电源时序控制可以错开上电过程中的浪涌电流,这种技术对于采用限流电源供电的应用十分

2018-10-23 14:30:34

的行为表现(参见表2),分析可能的问题及原因,并提出一些建议。上电时序问题多种多样上电时序问题可能出现于多种不同情况。例如,在一个客户应用中,AD8616配置为缓冲器,在电源建立之前输入为0 V(图1

2019-06-18 08:30:00

ADM108x简单时序控制器可在上电期间对两个电压轨进行简单的时序控制,时间延迟可通过电容进行编程。利用该系列的两个器件可构成一个简单的电路,从而以各自可编程的时间延迟对两

2011-09-01 15:57:19 34

34 Power on Sequence:主板上的供电,从最开始的电压适配器电压输入,到最后CPU供电的产生,都有严格的开启顺序控制,这个先后顺序,就是上电时序。

2016-09-01 15:44:10 0

0 主板开机原理与上电时序图

2016-12-17 21:30:39 0

0 基于时序模拟的并网型微网可靠性分析_王玉梅

2017-01-08 10:30:29 0

0 为什么电源纹波不能直接一键捕获呢?为什么多路上电时序前后分析对比这么麻烦呢?为什么分析调制信号时波形对比度这么差呢?事实上,用户的每一次体验感,都是产品隐形的提升空间。以上这三个麻烦,现在也许有了新的解决方式。

2017-04-18 14:03:16 12

12 在这里以ASUS的915主板来描述一下 INTEL主板的上电及工作时序:

2017-09-20 14:23:27 20

20 时序以及各阶段I/O 管脚状态,说明了FPGA上电配置对电路功能的严重影响,最后针对不同功能需求的FPGA外围电路提出了有效的设计建议。

2017-11-22 07:18:34 8500

8500

时序图在有些教材上,又被翻译为顺序图,两者在表述上虽然有一些差别,但是大体都是准确的,可能称之为时序图会更加书面语话,听起来高大上的感觉。其实是一样的,重在理解,个人偏向于时序图,也就是时间顺序的意思。

2017-12-11 19:31:03 172768

172768

由上电时序可知,VDD_SOC_IN上电时序要迟于VDD_HIGH_IN,因此在电路设计中,可使用VDD_HIGH_IN电源芯片的控制信号使能VDD_SOC_IN的电源,如下图所示为使用VDD_HIGH_IN供电芯片的PG信号使能VDD_SOC_IN供电芯片的使能管脚。

2018-04-28 09:57:02 22709

22709

了解高精度MAX16050/MAX16051多路电压排序器/监测器的能力。利用MAX16050EVKIT,Ahmad和Andrew演示如何配置四路通道的上电和关断顺序,并介绍如何以菊链方式将器件连接在一起。

2018-10-09 03:13:00 5006

5006 幅度。既定的电源系统设计可能包括电源时序控制、电源跟踪、电源电压/电流监控和控制。有各种各样的电源管理IC可以执行时序控制、跟踪、上电和关断监控等功能。

2019-04-09 08:14:00 4459

4459

微处理器、FPGA、DSP、模数转换器 (ADC) 和片上系统 (SoC) 器件一般需要多个电压轨才能运行。为防止出现锁定、总线争用问题和高涌流,设计人员需要按特定顺序启动和关断这些电源轨。此过程称为电源时序控制或电源定序,目前有许多解决方案可以有效实现定序。

2019-09-15 09:22:00 1219

1219

Air机器的适配器电压为14.5V,经过一个电源小板到底主板的电源接口J7000,虽然电源小板集合了很多功能,但是买一个没多少钱,我再次就不熬赘了,只会分析主板的上电时序。

2019-11-15 08:00:00 92

92 一:供电电源时序 EMMC 的供电有两种模式,且分两路工作,有 VCC 和 VccQ。在规范上,上电时序是有要求的,如下图所示。 EMMC 上电时序 开始上电时,VCC 或 VccQ 可以第一个倾斜

2020-10-30 21:29:17 3909

3909 EMMC 的供电有两种模式,且分两路工作,有 VCC 和 VccQ。在规范上,上电时序是有要求的,如下图所示。

2020-12-02 23:13:00 23

23 本文档的主要内容详细介绍的是英业达上电时序的详细资料说明。

2020-12-04 08:00:00 63

63 本文档的主要内容详细介绍的是电源模块的上下电时序介绍免费下载。

2020-12-10 08:00:00 12

12 ,但有些设计可能需要采用其他序列。无论如何,正确的上电和关断时序控制可以防止闩锁引发的即时损坏和 ESD 造成的长期损害。此外,电源时序控制可以错开上电过程中的浪涌电流,...

2021-01-20 16:13:39 8

8 AN-1080: 利用简单时序控制器ADM108x进行上电和关断时序控制

2021-03-21 00:41:43 6

6 启动和关断这些电源轨。此过程称为电源时序控制或电源定序,目前有许多解决方案可以有效实现定序。对于需要电压定序的复杂器件,其内核和模拟模块的电压轨可能需要在数字 I/O 电压轨之前上电。有些设计可能会要求...

2021-11-07 18:37:03 10

10 钩:和上电时序有一定关系... 3. 上电回沟的问题,如果你认为你的上电时序设计的没问题,那么还要考察一下芯片自己的问题,打个比方,芯片有3.3V和1.5V的输入,1.5V先上电, 3.3V后上电,现象是 3.3V...

2022-01-11 12:02:39 13

13 丰富的应用特性。这些设备向电源系统提供不同的数字负载,要求使用不同功率等级的多种电压轨,每一种都具有高度个性化的电压轨容差。同样,正确的电源开启和关断时序也很重要。随着时间推移,电路板上电压轨的数量成倍增加,使得电源系统的时序设计和调试变得更加复杂。

2022-01-21 10:51:46 2624

2624

Class-D 功放TAS5731M 上电时序分析

2022-10-31 08:24:00 1

1 此外,每个转换器各个电压的延迟将不同。这会导致不同电压域中不受控制的斜坡上升,从而导致功能问题和系统损坏。

2022-12-16 15:50:07 1819

1819

进行时序控制和管理的需求。 ADI公司的数据手册通常会提供足够的信息,指导设计工程师针对各IC设计正确的上电序列。然而,某些IC明确要求定义恰当的上电序列。对于ADI公司的许多IC,情况都是如此。在使用多个电源的IC中,如转换器(包括模数

2022-12-19 20:32:18 2392

2392

电子发烧友网站提供《IC上电复位和关断功能建议.pdf》资料免费下载

2023-11-23 14:36:33 5

5 笔记本上电时序

2024-01-09 10:26:36 1

1 电子发烧友网站提供《利用关断保护信号开关消除电源时序.pdf》资料免费下载

2024-09-23 12:24:26 0

0

电子发烧友App

电子发烧友App

评论