在亚微米以下的电路设计中,需要对电路进行全芯片的ESD保护结构的设计。如何使全芯片有效面积尽可能小、ESD性能可靠性满足要求且不需要增加额外的工艺步骤成为全芯片设计者的主

2012-04-23 10:17:42 4709

4709

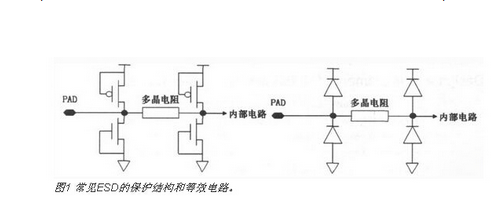

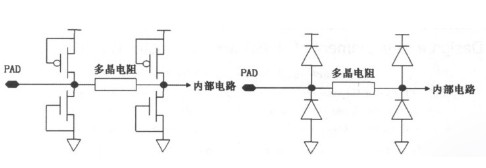

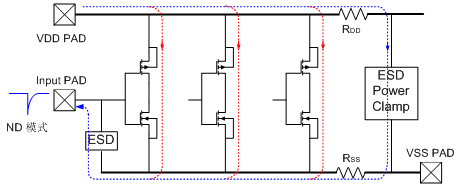

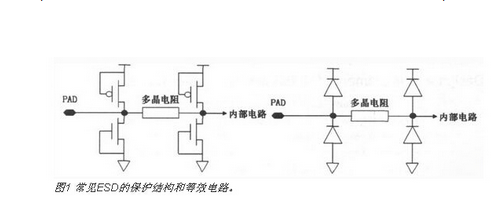

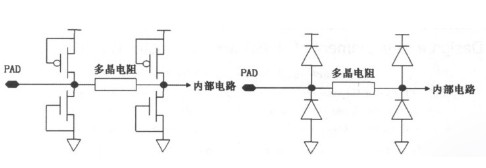

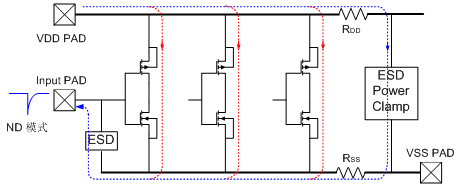

大部分的ESD电流来自电路外部,因此ESD保护电路一般设计在PAD旁,I/O电路内部。典型的I/O电路由输出驱动和输入接收器两部分组成。ESD 通过PAD导入芯片内部,因此I/O里所有与PAD直接

2014-12-24 11:05:47 3291

3291

要求,重点讨论了在I/O电路中ESD保护结构的设计要求。 1 引言 静电放电会给电子器件带来破坏性的后果,它是造成集成电路失效的主要原因之一。随着集成电路工艺不断发展,CMOS电路的特征尺寸不断缩小,管子的栅氧厚度越来越薄,芯片的面积规模越来越大,MOS管能

2017-12-05 09:03:40 13455

13455

近年来,有关将CMOS工艺在射频(RF)技术中应用的可能性的研究大量增多。深亚微米技术允许CMOS电路的工作频率超过1GHz,这无疑推动了集成CMOS射频电路的发展。目前,几个研究组已利用标准

2021-07-29 07:00:00

, EOS等各项指标的要求。随着IC先进制程技术的应用, 芯片功能的增多和尺寸的减小, 对于半导体厂和设计公司来说, 不断面临着产品对静电保护ESD提出的越来越高的要求。这次授课老师为Bart Keppens

2015-04-22 22:19:54

。 IC制造商已经将ESD损伤确定为互补式金属氧化物半导体(CMOS)元件现场可靠性的一项主要威胁,它可能损害品牌形象并妨碍市场接受新技术。为避免此情况,业界积极努力用后续新制程世代来最佳化整合ESD

2011-11-24 15:00:58

UM5051/5052的重要参数ESD保护器件的种类ESD应用举例

2021-04-02 07:37:30

能够承受ESD的冲击,并继续正常工作。ESD保护方法为了给电子系统提供ESD保护,可以从不同的角度来着手。一种方法是在半导体芯片内建ESD保护架构。不过,日趋缩小的CMOS芯片已经越来越不足以承受进行

2011-07-05 14:19:03

取舍,实际上会使系统整体性能在某种程度上受损。对于设计能够同时符合更高数据率和更好ESD保护新需求的芯片的制造商来说,要实现这个目标极具挑战性。ESD保护领域的变化 由于采用更小的制造几何尺寸、片上保护

2011-01-27 10:35:10

水平,以便使那些采用了对ESD越来越敏感的IC的终端产品保持高可靠性。 ESD波形 以系统级的方法来定义典型的ESD事件所采用的最常见的波形,是以其亚纳秒上升时间和高电流电平(参见图1)为显著特征

2010-08-18 19:44:07

径,把异常电压箝制在一个安全的水平,从而保护被保护IC或线路。ESD二极管凭借体积小、封装多样化、响应速度快(小于1ns)、电容值低、漏电流低(小于1uA)、超低箝位电压、电压值低等独有优势,广泛应用

2018-10-17 16:04:52

如何正确保护IC?ESD传递模式有哪几种?ESD保护和应用电路如何提高ESD保护?

2021-04-23 06:23:47

告诉《中国电子报》记者,据统计,超过60%的IC失效都源于ESD。 随着超大规模集成电路工艺的高速发展,特征尺寸已经到深亚微米阶段,大大提高了集成电路的性能及运算速度,但随着器件尺寸的减小,对可靠性

2013-02-21 10:54:18

对电子器件来说,一次我们无法察觉的轻微静电放电就可能对其造成严重的损伤。泰科电子瑞侃电路保护产品应用工程经理董告诉《中国电子报》记者,据统计,超过60%的IC失效都源于ESD。 随着

2013-08-16 10:22:02

[table][tr][td]随着现代社会的飞速发展,我们对电子设备的依靠与日俱增.现代电脑越来越多的采用低功率逻辑芯片,由于MOS的电介质击穿和双极反向结电流的限制,使这些逻辑芯片对ESD非常敏感

2013-11-20 15:43:19

`随着半导体工艺尺寸从微米量级向纳米量级缩小,静电放电(ESD)对于半导体器件与系统的影响仍在持续。本书从全芯片ESD设计综合的角度,对EOS、ESD以及Latchup进行了探讨。针对ESD保护

2013-09-04 09:17:26

因为要求高集成度、快速度和小体积,如今的新兴电子产品都使用基于先进深次微米制程的芯片。但制程越先进,芯片对 ESD 耐受度也就越差。当这些电子产品在实际环境下受到 ESD冲击时,IC 内部更容易受到

2013-06-14 16:42:50

(螺丝起子)靠近有相反电势的集成电路(IC)时,电荷“跨接”,引起静电放电(ESD)。 ESD以极高的强度很迅速地发生,通常将产生足够的热量熔化半导体芯片的内部电路,在电子显微镜下外表象向外吹出的小?弹孔

2018-10-11 16:10:23

。不过,日趋缩小的CMOS芯片已经越来越不足以承受进行内部2 kV等级的ESD保护所需要的面积。安森美半导体标准产品部亚太区市场营销副总裁麦满权指出:真正有效的ESD保护是不能完全集成到CMOS芯片之中

2013-01-04 14:58:24

为了给电子系统提供ESD保护,可以从不同的角度来着手。一种方法是在半导体芯片内建ESD保护架构。不过,日趋缩小的CMOS芯片已经越来越不足以承受进行内部2KV等级的ESD保护所需要的面积。真正有效

2014-02-14 10:30:16

的安全保护伞的所有部分都应该“硬化”或者屏蔽攻击,包括加密密钥、验证码和固件。深联华 基于硬件的安全性可在很小的空间内通过简单且高成本效益的方式实现这一目标。几乎没有任何方法可以下载已锁定在芯片中的秘密

2013-12-30 16:04:47

摘 要:EDA技术是现代电子设计技术的核心,它在现代集成电路设计中占据重要地位。随着深亚微米与超深亚微米技术的迅速发展,FPGA设计越来越多地采用基于VHDL的设计方法及先进的EDA工具。本文详细

2019-06-18 07:33:04

摘 要:EDA技术是现代电子设计技术的核心,它在现代集成电路设计中占据重要地位。随着深亚微米与超深亚微米技术的迅速发展,FPGA设计越来越多地采用基于VHDL的设计方法及先进的EDA工具。本文详细

2019-06-27 08:01:28

HDMI接收器和发射器的IC芯片全部采用深亚微米工艺制造。亚微米CMOS制程十分敏感,通常设有ESD保护限制(最高2kV),必须符合人体放电模式(HBM)标准。另外,LCD电视和机顶盒(STB)等

2013-11-21 09:57:59

和发射器IC芯片采用的是亚微米CMOS工艺制造而成的,而亚微米CMOS十分地敏感,为此需要借助ESD静电保护器件和ESD静电保护解决方案为其保驾护航。机顶盒STB、电视LCD等终端应用极其容易受到ESD

2020-12-31 15:57:17

已经过第三方实验室验证。 产品特点及其优点l CMOS霍尔IC技术l 强大的抗RF噪声技术l 工作电压1.8至6V,适用于电池供电的应用l 低至1.65V的工作电压,全极霍尔开关微功耗l 高灵敏度可替换

2019-11-07 10:34:36

)的冲击经由NFC天线对整个NFC的沟通功能所造成的错误动作。移动电话这些电子产品由于频繁地与人体接触,很容易受到静电放电(ESD)的冲击。此外,这些电子产品所采用的IC大多是使用最先进的半导体制程技术,所

2019-06-13 08:18:01

TVS的ESD保护原理ESD TVS器件采用的技术汇总

2021-04-02 06:19:56

的应用很容易受到静电放电的影响。一些采用了深亚微米工艺和甚精细线宽布线的复杂半导体功能电路,对电路瞬变过程的影响更加敏感,将导致上述的问题更加激化。电路保护元件存在几种技术,当选择电路保护元件时,若

2019-07-29 17:50:09

的电路板空间以及被保护电路的电特性来决定。因为利用先进工艺技术**的IC电路里氧化层比较薄,栅极氧化层更易受到损害。而且一些采用深亚微米工艺和甚精细线宽布线的复杂半导体功能电路,对电路瞬变过程的影响更加

2018-11-20 14:09:05

如今的电子系统中越来越多地采用以CMOS工艺制造的低功率逻辑芯片。这些芯片如果遭遇足够高的静电放电(ESD)电压,芯片内部的电介质上就会产生电弧,并在门氧化物层烧出显微镜可见的孔洞,造成芯片的永久

2013-12-27 16:21:39

...............................................................................1ESD (Electrostatic Discharge) Protection in CMOS Integrated Circuits ..........................1目录

2011-02-24 09:55:18

)靠近有相反电势的集成电路(IC)时,电荷“跨接”,引起静电放电(ESD)。ESD以极高的强度很迅速地发生,通常将产生足够的热量熔化半导体芯片的内部电路,在电子显微镜下外表象向外吹出的小?弹孔,引起即时

2016-07-22 11:26:49

随着半导体工艺的飞速发展和芯片工作频率的提高,芯片的功耗迅速增加,而功耗增加又将导致芯片发热量的增大和可靠性的下降。因此,功耗已经成为深亚微米集成电路设计中的一个重要考虑因素。为了使产品更具竞争力

2019-10-14 07:48:14

深亚微米的CMOS工艺制造高速分频器。由于CMOS器件的价格低廉,因而高速CMOS分频器有着广阔的市场前景。那分频电路由什么构成?你们知道2.4GHz动态CMOS分频器设计难吗?

2021-04-07 06:17:39

ESD(静电放电)是CMOS电路中最为严重的失效机理之一,严重的会造成电路自我烧毁。论述了CMOS集成电路ESD保护的必要性,研究了在CMOS电路中ESD保护结构的设计原理,分析了该结构对版图的相关要求,重点讨论了在I/O电路中ESD保护结构的设计要求。

2021-04-02 06:35:57

,提高了芯片的运算速度。 但是,随着工艺的进步和尺寸的减小,静电释放(ESD),Elecyro Static Discharge)问题变得日益严峻。据统计,在集成电路设计中大约40%的失效电路是ESD问题造成的。如何设计ESD保护电路?这个问题急需解决。

2019-08-07 06:24:17

关键芯片组外部ESD保护要求硅ESD保护技术与无源ESD保护技术比较消除信号完整性问题的PicoGuard XS ESD保护技术智能手机等便携及消费产品电路保护及滤波应用示例

2021-04-09 06:55:32

首创。集成式固态ESD保护是专有的ADI技术,可实现非常高的ESD保护同时对MEMS开关RF性能影响最小。图3显示了采用SMD QFN封装的ESD保护元件。其中,芯片安放在MEMS芯片上,通过焊线连接

2018-11-01 11:02:56

本文选择了SoC芯片广泛使用的深亚微米CMOS工艺,实现了一个10位的高速DAC。该DAC可作为SoC设计中的IP硬核,在多种不同应用领域的系统设计中实现复用。

2021-04-14 06:22:33

近年来,有关将CMOS工艺在射频(RF)技术中应用的可能性的研究大量增多。深亚微米技术允许CMOS电路的工作频率超过1GHz,这无疑推动了集成CMOS射频电路的发展。目前,几个研究组已利用标准

2019-08-22 06:24:40

和低功耗设计、设计验证、芯片测试和可测性设计等主题,着重探讨了深亚微米数字集成电路设计面临的挑战和启示。本书可作为高等院校电子科学与技术(包括微电子与光电子)、电子与信息工程、计算机科学与技术、自动化等

2009-02-12 09:51:07

深亚微米CMOS工艺中,I/O单元的实现可以从235微米减小到160微米和138微米。 这种新的设计方法在ESD防护性能和效率上都很大程度提高,并且在实现防静电保护避免IC损坏,进一步提高晶圆使用的效率方面发挥了积极作用。参考资料:防静电资讯网

2012-12-11 13:39:47

新型互补电容耦合ESD保护电路的设计提出了一种改进型的基于亚微米工艺中ESD 保护电路, 它由互补式电容实现, 结构与工艺简单。电路采用0.6μm1P2MCMOS 工艺进行了验证, 结果表明

2009-12-23 16:33:58

。从成本效益比的角度来看,这已经被证明是件很难做到的事。从图1可以看出,随著制造技术转向90nm以下,将ESD保护水平维持在2,000V的成本,已开始以指数级上升。因此,现在新的目标是降低芯片上

2019-05-22 05:01:12

我在LM386的技术文档中看到了该芯片的内部电路图,发现电路中有两个二极管连接了VSS和VDD,应该是构成了ESD保护电路,请问这个保护电路是只对输出引脚Vout进行保护,还是被所有引脚所共享,即

2024-09-30 06:22:18

IC。在一个新的模块快速连接该器件和ESD测试开始获得好的结果,因为SZESD9101成功保护了GPS通过所需的8kV存在等级。有了推荐的ESD保护器件、TLP的结果以及向上层管理报告8kV通过结果

2018-10-25 09:02:26

【作者】:张科营;郭红霞;罗尹虹;何宝平;姚志斌;张凤祁;王园明;【来源】:《原子能科学技术》2010年02期【摘要】:采用TCAD工艺模拟工具按照等比例缩小规则构建了从亚微米到超深亚微米级7种

2010-04-22 11:50:00

,不普通数字电路更容易遭到损坏,因为用于ESD保护的传输入保护结构会增加输入泄露,因此不能使用。所有ESD敏感器件均采用保护性封装。IC通常装在导电泡沫中或者防静电包装套管中,而后将容器密封在一个静电

2018-01-16 14:21:19

解读ESD静电抑制器 因为要求高集成度、快速度和小体积,如今的新兴电子产品都使用基于先进深次微米制程的芯片。但制程越先进,芯片对 ESD 耐受度也就越差。当这些电子产品在实际环境下受到 ESD冲击

2013-12-11 15:58:03

使用液晶电视等HDMI终端设备支持的音频/视频格式。 HDMI接收器和发射器的IC芯片全部采用深亚微米工艺制造。亚微米CMOS制程十分敏感,通常设有ESD保护限制(最高2kV),必须符合人体放电模式

2019-06-17 05:00:06

摩尔定律对先进CMOS IC的ESD保护的影响 持续不断的特征尺寸小型化趋势,已经使半导体制造商能够在过去几十年中通过把几十亿三极管集成到单一芯片之中来提高芯片性能、降低功耗及驱动成本的下降。尽管

2018-12-05 10:39:44

随着现代社会的飞速发展,我们对电子设备的依赖与日俱增.现代电脑越来越多的采用低功率逻辑芯片,由于MOS的电介质击穿和双极反向结电流的限制,使这些逻辑芯片对ESD非常敏感。大多数USB集成电路都是

2019-08-02 17:43:22

本文介绍了以超深亚微米技术为支撑的 SOC 的定义以及芯片设计方法,并阐述了软硬件协同设计理论、IP 核生成及复用技术、超深亚微米IC 设计面对的难题以及SOC 测试与验证技术。

2009-06-19 09:28:12 35

35

随着工艺的发展,器件阈值电压的降低,导致静态功耗呈指数形式增长。进入深亚微

米工艺后,静态功耗开始和动态功耗相抗衡,已成为低功耗设计一个不可忽视的因素

2009-09-15 10:18:10 18

18 随着工艺的发展,器件阈值电压的降低,导致静态功耗呈指数形式增长。进入深亚微米工艺后,静态功耗开始和动态功耗相抗衡,已成为低功耗设计一个不可忽视的因素。针对近

2009-09-15 10:18:10 26

26 CMOS工艺中GG2NMOS结构ESD保护电路设计:采用GG2NMOS 结构的ESD 保护电路的工作原理和对其进行的ESD 实验,提出了一种保护电路的栅耦合技术方案,并达到了预期效果. 通过实验可以看出其性

2009-11-20 14:48:43 41

41 本文研究了在CMOS 工艺中I/O 电路的 ESD 保护结构设计以及相关版图的要求,其中重点讨论了PAD 到VSS 电流通路的建立。关键词:ESD 保护电路,ESD 设计窗口,ESD 电流通路Constru

2009-12-14 10:45:54 55

55 本文采用 MEDICI 作为集成电路ESD 保护常用器件—栅极接地N 型MOS 管(GGNMOS)ESD 性能分析的仿真工具,综合分析了各种对GGNMOS 的ESD 性能有影响的因素,如衬底掺杂、栅长、接触

2009-12-14 10:59:02 22

22 本文通过对传统大规模集成电路设计流程的优化,得到了更适合于深亚微米工艺集成电路的后端设计流程,详细介绍了包括初步综合、自定义负载线的生成、版图规划、时钟树综合

2009-12-14 11:03:09 15

15 和舰科技自主创新研发的0.16 微米硅片制造工艺技术在原有比较成熟的0.18 微米工艺技术基础上,将半导体器件及相关绕线尺寸进行10%微缩(实际尺寸为0.162 微米),大大降低了芯

2009-12-14 11:23:36 25

25 基于深亚微米MOS 器件沟道的热噪声浅析曾献芳摘要: 随着 MOS 器件工艺尺寸的不断减小,其不断增高的单位增益截止频率足以满足射频/模拟电路的工作要求。然而,随着沟

2009-12-15 14:31:04 10

10 超深亚微米IC设计中的天线效应李蜀霞 刘辉华 赵建明 何春(电子科技大学电子电子科学技术研究院 成都 610054)【摘要】本文主要分析了超深亚微米集成电路设计中天线效应

2009-12-19 14:54:53 45

45 摘要:就超深亚微米集成电路中高K栅介质、金属栅、cU/低K互连等相关可靠性热点问题展开讨论.针对超深亚微米集成 电路可靠性问题.提出可靠性设计、生产过程的质量控制、可

2010-04-27 14:13:33 19

19 摘要:增强测试质量和抑制测试代价是超深亚微米集成电路测试及可测性设计领域的两个研究主题。本文介绍了一个基于Mentor公司可测性设计工具的面向多种故障模型的超深亚微

2010-06-07 11:01:17 10

10 分析了在超深亚微米阶段,串扰对高性能芯片设计的影响,介绍了消除串扰影响的方法。 关键词:串扰,布线,关键路径,

2009-05-05 20:59:16 1434

1434

一种全新的深亚微米IC设计方法

本文分析了传统IC设计流程存在的一些缺陷,并且提出了一种基于Logical Effort理论的全新IC设计方法。

众所周知,传统的IC设计流

2009-12-27 13:28:50 896

896

TSMC推出最新深亚微米互通式EDA格式

TSMC 7日宣布针对65纳米、40纳米及28纳米工艺推出已统合且可交互操作的多项电子设计自动化(Electronic Design Automatio

2010-04-09 10:36:49 939

939 新型深亚微米电流灵敏放大器技术设计

随着便携式电子设备(PDA、射频卡、GPS等)的广泛应用,半导体存储器得到了长足的发展。半导体存储器的性能

2010-04-27 17:37:46 873

873

目前几乎所有的芯片组都有片上ESD保护。ESD电路放在芯片的外围和邻近I/O焊垫处,它用于在晶圆制造和后端装配流程中保护芯片组。在这些环境中,ESD可通过设备或工厂的生产线工作人员引入到芯片组上

2011-02-18 10:29:07 1260

1260

模拟/混合信号Ic设计一直是困扰很多中国Ic设计工程师的难题。与数字电路设计相比,模拟/混合电路设计要求更为严苛,而且需要严格的环境控制工艺。而对于深亚微米级的SOC设计还必

2011-03-31 16:16:10 0

0 下一代的实体设计系统IC Compiler,为Synopsys Galaxy Design Platform 2005的核心,其设计概念就在解决这些浮现的挑战,提供从RTL到芯片的一贯解决方案

2011-04-19 11:14:51 1312

1312 研究了深亚微米pMOS 器件的热载流子注入(hot2carrier injection ,HCI) 和负偏压温度不稳定效应(negative bias temperature instability ,NBTI) 的耦合效应和物理机制.

2012-04-23 15:35:39 34

34 近年来,有关将CMOS工艺在射频(RF)技术中应用的可能性的研究大量增多。深亚微米技术允许CMOS电路的工作频率超过1GHz,这无疑推动了集成CMOS射频电路的发展。目前,几个研究组已利

2012-05-21 10:06:19 2373

2373

BiCMOS[B]的 Twin-Well[1]与P-Well[2]或 N-Well[3] 的制造技术有很大的不同。主要是 CMOS 特征尺寸为亚微米级,使制造技术发生了重要的变化。

由于器件

2017-12-18 14:30:18 7653

7653 1 深亚微米 BiCMOS[B] 技术

器件进入深亚微米特征尺寸,为了抑制 MOS 穿通电流和减小短沟道效应,深亚微米制造工艺提出如下严格的要求:

(1)高质量栅氧化膜。栅氧化膜厚度

2018-03-16 10:29:54 8670

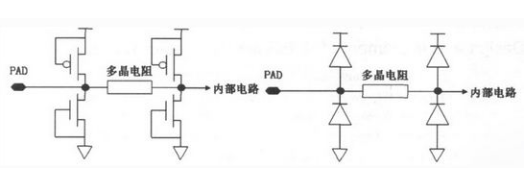

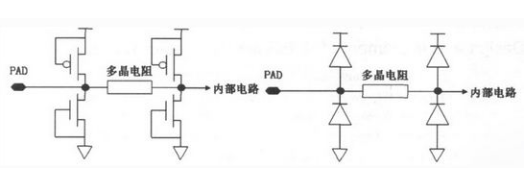

8670 ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。这个低阻旁路不但要能吸收ESD电流,还要能箝位工作电路的电压,防止工作电路由于电压过载而受损。

2019-03-04 14:24:01 5070

5070

ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。这个低阻旁路不但要能吸收ESD电流,还要能箝位工作电路的电压,防止工作电路由于电压过载而受损。

2019-04-08 15:26:11 2997

2997

随着CMOS集成电路产业的高速发展,越来越多的CMOS芯片应用在各种电子产品中,但在电子产品系统的设计过程中,随着CMOS工艺尺寸越求越小,单位面积上集成的晶体管越来越多,极大地降低了芯片的成本

2020-12-30 10:28:00 2

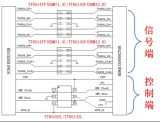

2 ESD保护设计随着CMOS工艺的演进而越来越困难,迄今已有六百多件ESD相关的美国专利。而且,ESD更应当从芯片全局考虑,而不只是Input PAD,Output PAD,或Power PAD的问题。

2021-03-17 22:28:55 25

25 采用基于物理的指数MOSFET模型与低功耗传输域MOSFET模型,推导了新的超深亚微米无负载四管与六管SRAM存储单元静态噪声容限的解析模型.对比分析了由沟道掺杂原子本征涨落引起的相邻MOSFET的阈值电压失配对无负载四管和六管SRAM单元静态噪声容限的影响。

2021-03-26 15:17:54 6

6 数字集成电路分析与设计:深亚微米工艺免费下载。

2021-05-12 14:52:40 180

180 电子发烧友网站提供《ESD保护芯片CH412技术手册.pdf》资料免费下载

2022-09-09 11:29:03 3

3 点击上方“蓝字”关注我们!IC片上保护设计对EOS的影响全面的方法可以减少与EOS相关的故障通常理解的是,芯片上ESD保护是必不可少的,以满足人体模型(HBM)和充电装置模型产品合格(CDM)ESD

2021-12-31 16:08:02 3499

3499

静电放电(ESD)是电子设备中一种常见的危害,它可能导致集成电路(IC)的损坏。对于CMOS IC来说,经受过严重ESD电击的可靠性会降低。

2023-12-15 15:32:09 1548

1548 据江阴发布的信息透露,此次发布的亚微米互联技术依托本土设备技术实力,运用大视场光刻技术达到了0.8um/0.8um的线宽线距技术水准,所生产的硅穿孔转接板产品达到3倍光罩尺寸,这标志着盛合晶微在先进封装技术领域迈入亚微米时代

2024-05-20 11:47:57 1632

1632 据统计,静电放电(Electro-Static Discharge, ESD)造成的芯片失效占到集成电路产品失效总数的38%。完好的全芯片ESD防护设计,一方面取决于满足ESD设计窗口要求的优质ESD器件结构,另一方面全芯片ESD防护网络的考量也格外重要。

2024-06-22 00:31:59 2157

2157

如下图1所示为HDMI接口与ESD保护芯片连接示意图,其中HDMI CONNECTOR指的是HDMI接口,HDMI RECEVIER指的是各种器件所配置的HDMI连接端口,ESD保护芯片主要

2024-12-29 13:56:10 2044

2044

电子发烧友App

电子发烧友App

评论