手机中ESD和EMI干扰

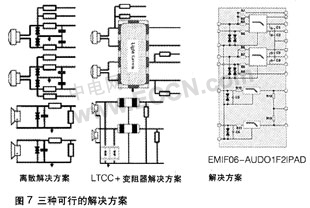

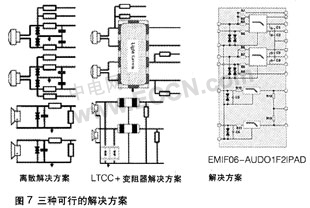

这篇文章简要地探讨了手机音频系统中ESD及EMI的起因及结果。接着研讨了ESD干扰抑制器和EMI滤波器的使用,以避免这些威胁。最后,比较了当前三种

2009-11-20 08:32:40 1222

1222

ESD中的电容问题

如果电子模块有不用的引脚,那么我们如何去处理呢?我们在处理时,可以考虑直接连接到地平面上去。(参考福特公司的处理

2009-11-20 08:37:29 2538

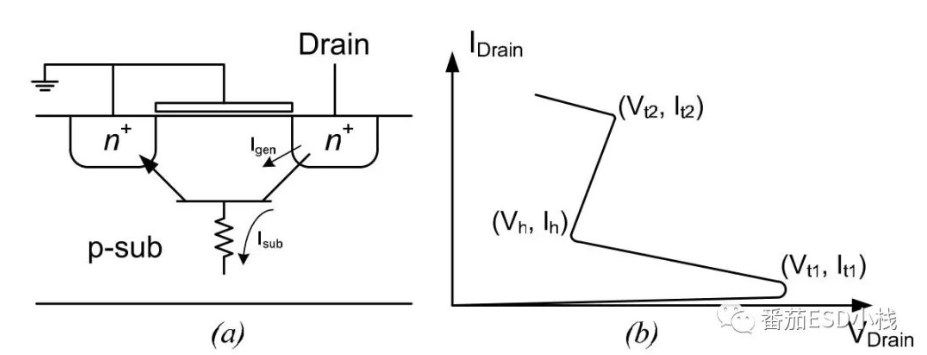

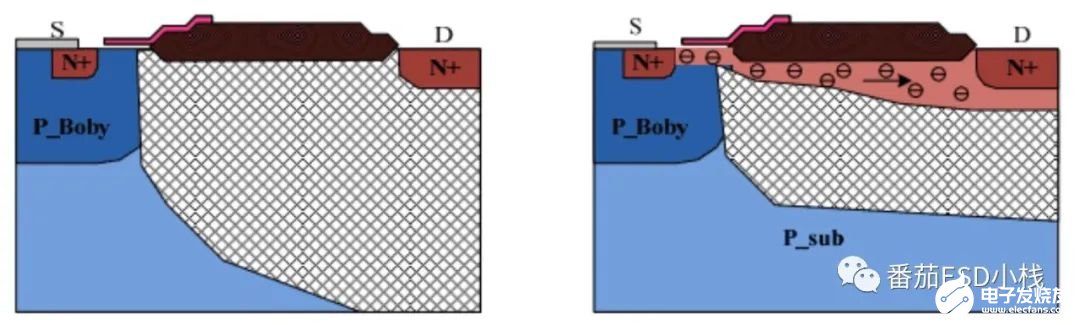

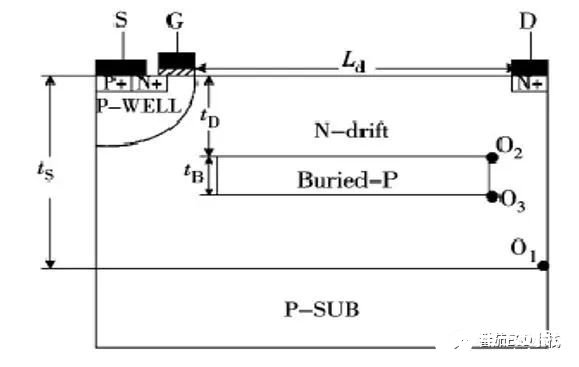

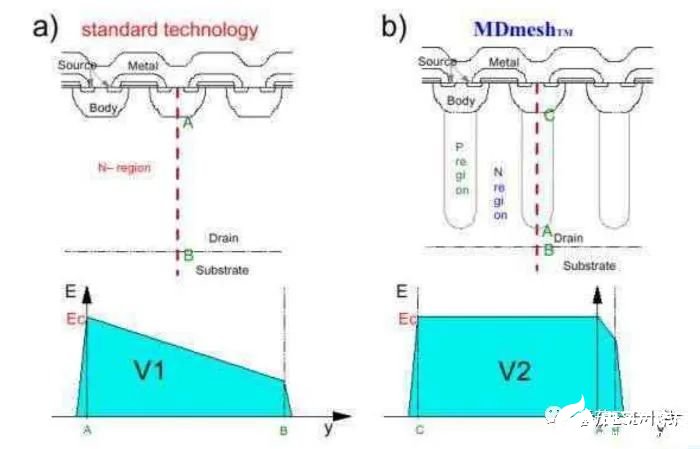

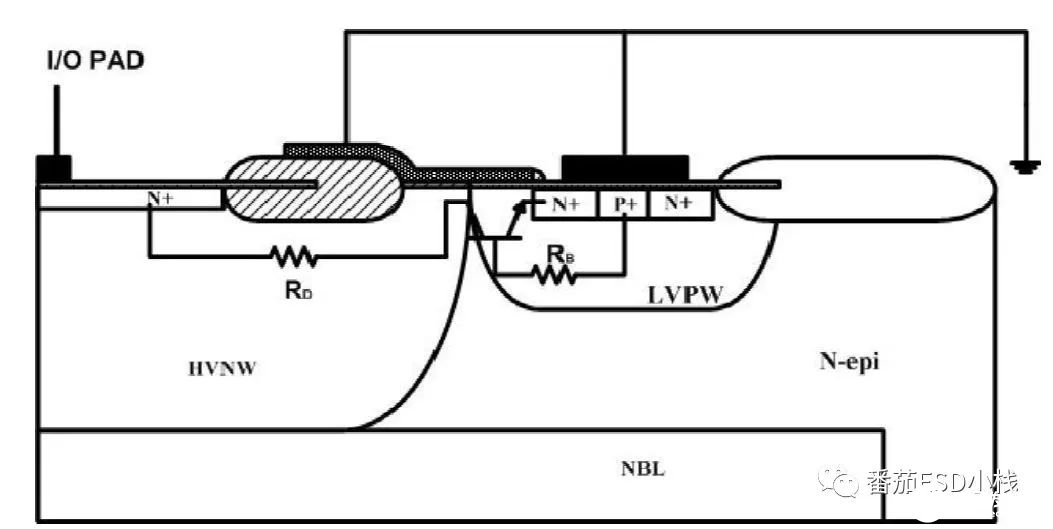

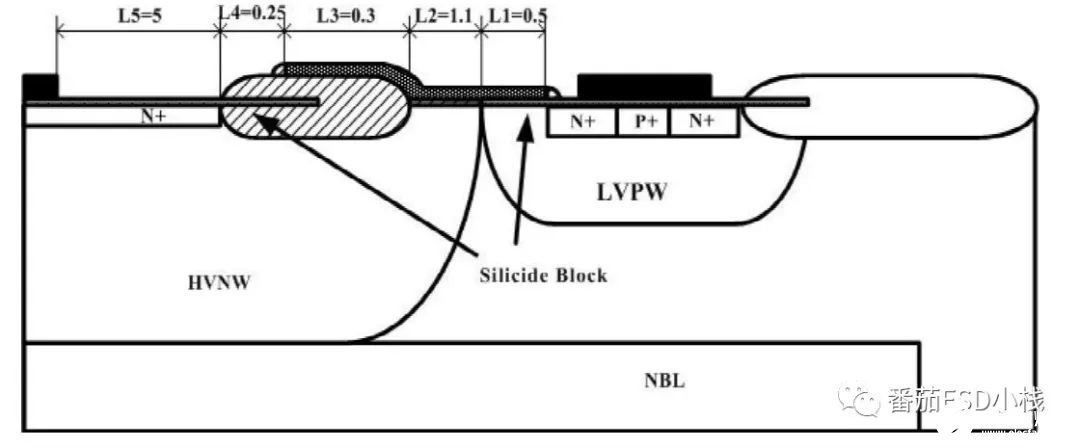

2538 通过对不同器件结构LDMOS的静电放电防护性能的分析对比,指出带埋层的深漏极注入双RESURF结构LDMOS器件在静电防护方面的优势。

2011-12-01 11:00:55 12329

12329

,需要用到低电容ESD静电保护器件为便携式电子产品保驾护航。那么,针对便携式电子产品的静电防护,该选用什么样的ESD静电保护二极管呢?1)结电容要低:在通讯端口静电防护方案设计中,尤其要关注ESD

2021-07-16 15:53:51

涵盖:在DRAM、SRAM、CMOS图像处理芯片、微处理器、模拟产品、射频模块中如何集成核心电路、电源总线以及信号引脚,以及这些整合将如何影响ESD的设计与集成。混合电压、混合信号的架构设计,以便于RF

2013-09-04 09:17:26

静电保护二极管、瞬态抑制TVS二极管、压敏电阻等。其中过压保护器件ESD保护管和TVS管同样值得关注,要知道,在汽车电子中,所有的电子设备都面临静电释放和汽车抛负载的威胁,故,在汽车电子中,过压保护不可

2018-10-23 17:15:03

损害,因此电子产品中的 ESD 保护越来越重要。为帮助读者清晰了解电子系统的 ESD 保护设计思路和解决方案,针对触摸屏和指纹识别人机界面、HDMI等高速接口电路等热点应用的 ESD 保护策略,深圳旭

2013-06-14 16:42:50

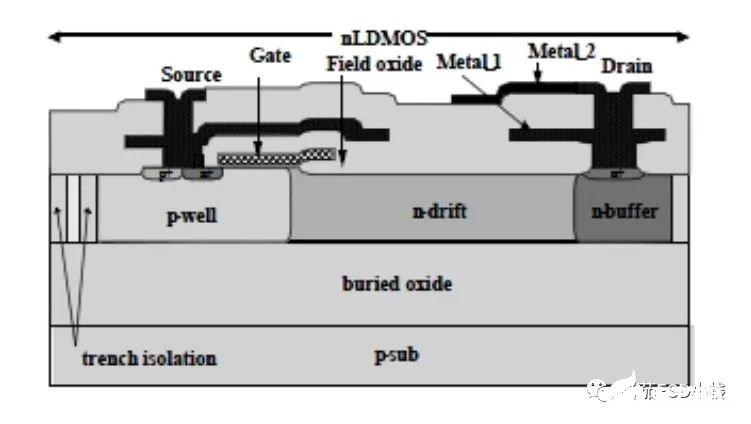

LDMOS L DMOS (横向扩散金属氧化物半导体) 结构见图。 在高压功率集成电路中常采用高压LDMOS满足耐高压、实现功率控制等方面的要求,常用于射频功率电路。 与晶体管相比,在关键

2020-05-24 01:19:16

GaN为5G sub-6GHz大规模MIMO基站应用提供的优势LDMOS的优势是什么如何选择正确的晶体管技术

2021-03-09 07:52:21

与双极型晶体管相比,LDMOS管的增益更高,LDMOS管的增益可达14dB以上,而双极型晶体管在5~6dB,采用LDMOS管的PA模块的增益可达60dB左右。这表明对于相同的输出功率需要更少的器件,从而增大功放的可靠性。

2020-04-07 09:00:33

LDMOS晶体管的应用,也使得LDMOS的技术不断成熟,成本不断降低,因此今后在多数情况下它将取代双极型晶体管技术。与双极型晶体管相比,LDMOS管的增益更高,LDMOS管的增益可达14dB以上,而双极型

2019-06-26 07:33:30

我在 AWR 中模拟 LDMOS MRFE6VS25N 时遇到问题。我使用 12 和 13 版本 64 位,但模型只有 32 位。我如何使用我的 AWR 软件模拟这个晶体管?

2023-04-23 09:07:17

。由于数据传送速度这么高,要求电路板的电容小,确保信号的素质很好,这给电路板的设计带来了新的挑战。在解决这个问题,实现可靠的静电放电(ESD)保护时,这点尤其重要。在HDMI系统设计中增加ESD保护

2019-06-19 05:00:08

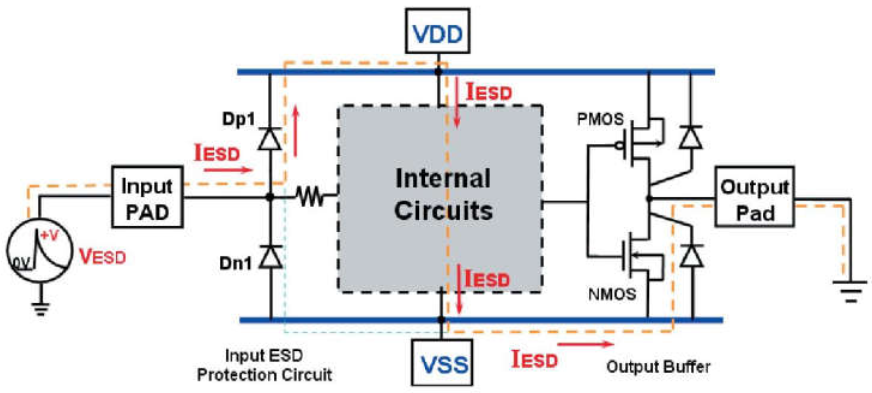

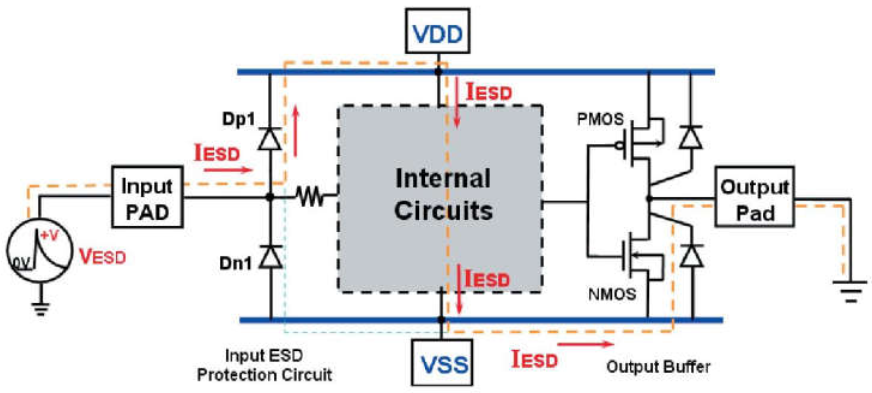

ESD(静电放电)是CMOS电路中最为严重的失效机理之一,严重的会造成电路自我烧毁。论述了CMOS集成电路ESD保护的必要性,研究了在CMOS电路中ESD保护结构的设计原理,分析了该结构对版图的相关要求,重点讨论了在I/O电路中ESD保护结构的设计要求。

2021-04-02 06:35:57

的抗ESD设计。在设计过程中,通过预测可以将绝大多数设计修改仅限于增减元器件。通过调整PCB布局布线,能够很好地防范ESD。以下是一些常见的防范措施。 *尽可能使用多层PCB,相对于双面PCB而言

2018-09-11 16:05:37

Infineon的LDMOS功放管凭优良的产品质量性能已广泛应用在移动通信设备中,在国内外不少知名通信设备生产商的设备中Infineon的功放管都占有一定的份额。 其中,Infineon专门

2019-07-08 08:10:02

用于无线基础设施的半导体技术正在经历一场重大的变革,特别是功率放大器(PA)市场。横向扩散金属氧化物半导体(LDMOS)晶体管在功率放大器领域几十年来的主导地位正在被氮化镓(GaN)撼动,这将对无线

2017-08-30 10:51:37

TVS在ESD防护中的作用ESD的危害我们都知道,轻则破坏电子产品,重的话会直接损坏甚至毁灭性的。美国的电子工业在ESD方面的损失一年可以达到数十亿美元之多。很多电子产品特别是自动化程度高,单键

2014-03-31 10:09:02

应尽量使其平滑。3.3 产品的电路设计 在壳体和PCB的设计中,对ESD问题加以注意之后,ESD还会不可避免地进入到产品的内部电路中,尤其是以下一些端口:USB接口、HDMI接口、IEEE1394

2015-08-06 02:49:47

什么是LDMOS?LDMOS有哪些有优良性能?什么是VDMOS?VDMOS具有哪些特征?

2021-06-18 06:56:36

`压敏电阻相比ESD电容在ESD保护中的优点?可以泄放ESD电压么?`

2015-12-28 17:41:43

用于现代通信系统中的功率放大器(PA)一般是通过级联和并联多个RF晶体管来获得期望的固态增益和功率。与RF集成电路(RFIC)相比,虽然采用单级分离RF晶体管占用的PCB空间更多,但因具有宽广

2019-06-25 06:55:46

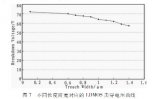

,结果表明,在保证LDMOS器件参数不变的条件下,采用深阱工艺可使其击穿电压提升50%以上。LDMOS (Lateral Diffused MetalOxide Semiconductor

2019-07-31 07:30:42

不适用。随着科技电子的发展,特别是消费电子产品,向着多功能、轻薄化发展,使得内部IC尺寸不断减小,相应ESD防护能力不断减弱。这时,电子工程师在设计过程中,通常会加入ESD静电保护器,当下使用率极高的ESD二极管,以此来防护静电对产品的伤害。ESD静电二极管规格书下载:

2022-04-27 16:12:10

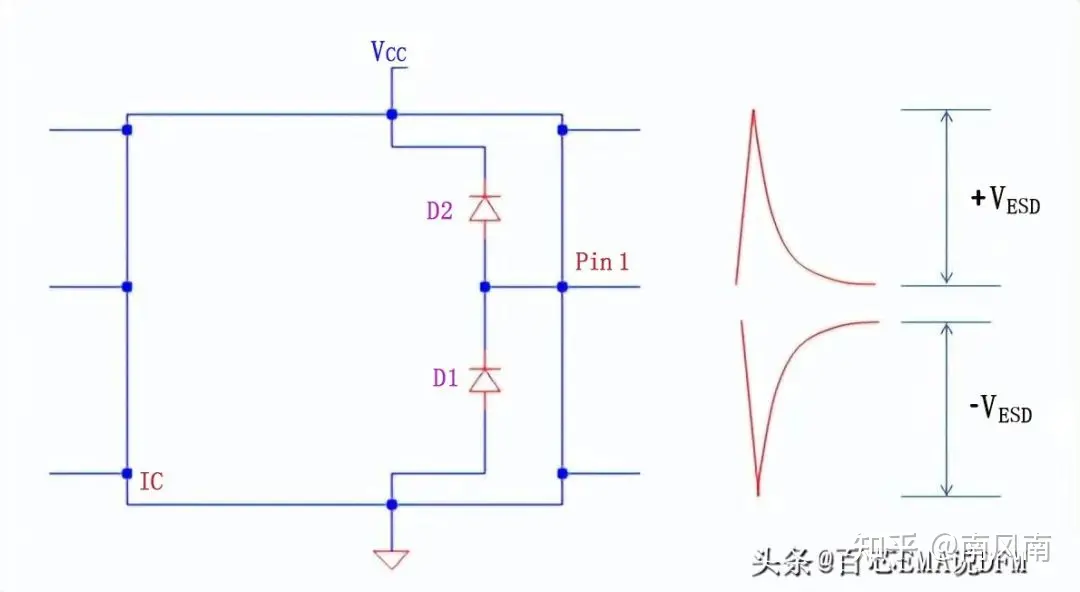

相信你就知道ESD是什么了。 一般而言,ESD可能会高达上千伏特,这会对比较敏感的半导体和集成电路造成损害。ESD在集成电路系统中对裸露在外的接口有非常重要的作用,当带有电荷的物体比如人类靠近或者

2020-10-22 13:31:35

今天给大家分享的是:在电路设计和PCB设计如何防止ESD损坏设备。

今天给大家分享的是:在电路设计和PCB设计如何防止ESD损坏设备。

在电子行业中,保护设备免受ESD

2024-03-26 18:47:57

LDMOS RF功率放大器因其极高的性价比在GSM和CDMA基站市场占据了主导地位。使用LDMOS放大器时,保证高性能的一个关键因素是补偿栅极偏置电压,以在温度变化时保持恒定的静态电流。Maxim的DS1870偏置控制器是目前众多的LDMOS RF功放偏置方案中的一款。

2019-08-23 06:38:37

已有电磁干扰。静电放电会破坏手机里的电子部件。手机容易替换,但对用户的伤害很大。手机电路设计者必须确保采取必要的措施,以消除ESD的破坏。 在音频电路中如有电磁干扰(EMI),会出现嘶嘶、噼啪、嗡嗡

2014-01-27 14:10:58

一个问题是电池状况不足。汽车中的电池短路事件发生在车辆中这些装置的组装,服务或消费者使用期间。在组装和维修期间,电池线路断开或暴露可能会连接到其中一个接口,从而可能对ESD保护装置造成损坏。在消费者

2018-10-12 11:53:47

作者:Jeremy Correale,安森美半导体目前市场上的多数硅ESD保护解决方案都是面向消费级电子器件设计的,但是ESD威胁也会使汽车电子器件设计师夜不成寐。令汽车电子设计师深感忧虑的不仅是“正常”的ESD状况,其他汽车特定事件也是让人寝食难安的一个重要原因,例如电池短路(STB)情况。

2019-07-25 07:32:28

在一天的工作正式开始前,粗略地浏览电子邮件,看到一连串报价、样品、项目和其他要求。对我来说,总是突颖而出的一个要求通常包含“帮助”和“ESD”两个词。这特殊的请求是在艰难的时刻产生,然而我忍不住笑了

2018-10-25 09:02:26

ESD保护器件。消费者使用过程中发生的电池短路事件的典型例子是,USB电缆掉进车载点烟器插座,把电池线电压带进接口线。汽车环境中存在12V电池网络,这本身就会对车载ESD保护器件造成额外的负担,因为这些

2018-10-25 08:49:49

在测试平板电脑ESD的过程中,我们时常会遇到这样的现象:平板电脑的放置方式对测试结果会有绝然不同的影响。将平板电脑Panel朝上时,ESD几枪就会死机;将Panel朝下时,正负电压各放电几十次都没

2014-02-20 11:23:55

射频半导体技术的市场格局近年发生了显著变化。数十年来,横向扩散金属氧化物半导体(LDMOS)技术在商业应用中的射频半导体市场领域起主导作用。如今,这种平衡发生了转变,硅基氮化镓(GaN-on-Si)技术成为接替传统LDMOS技术的首选技术。

2019-09-02 07:16:34

时,IC 内部更容易受到损害,因此电子产品中的 ESD 保护越来越重要。为帮助读者清晰了解电子系统的 ESD 保护设计思路和解决方案,针对触摸屏和指纹识别人机界面、HDMI等高速接口电路等热点

2013-12-11 15:58:03

大家都知道esd可以起保护作用,但是会加大通讯负担,影响通讯质量,那么USB设计中ESD到底要还是不要?

2019-03-22 09:51:56

■ 恩智浦半导体 K. Werner,S. Theeuwen,J. de Boet,V. Bloem,W. Sneijers高压LDMOS是高达3.8GHz的国防和航空电子设备RF功率应用的最佳技术

2019-07-05 07:01:04

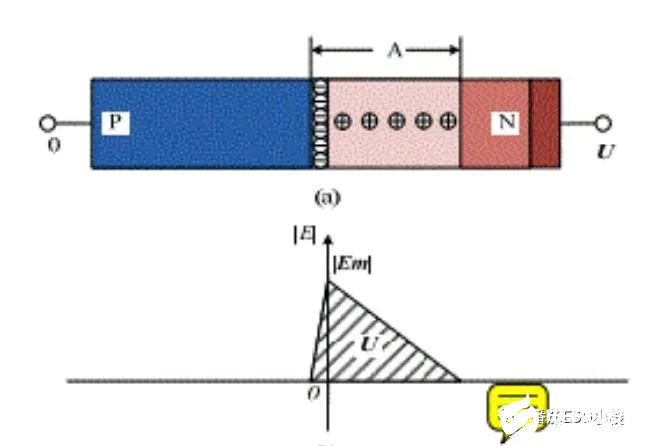

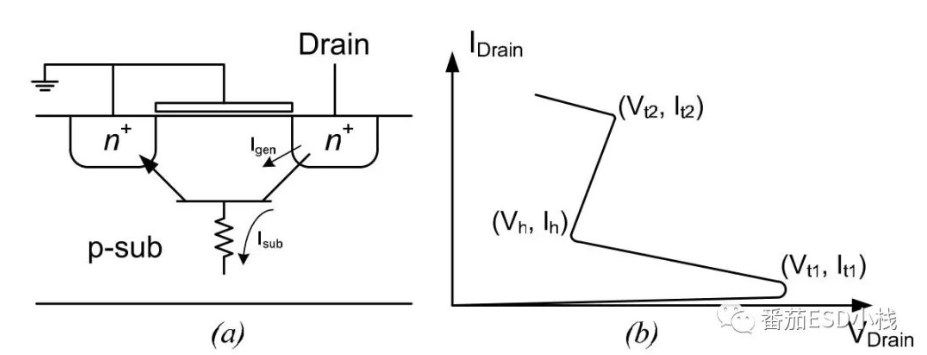

ESD设计提出了更高的防护要求。LDMOS是功率IC的常用器件,它与低压MOSFET一样存在静电泄放电流非均匀分布的问题,因而而器件在不做任何改进的情况下,不能充分发挥其静电防护的潜能,是LDMOS

2016-03-03 17:54:51

微电子技术有限公司开发的BSDOT器件,在相同面积下将LDMOS的静电防护潜能提高一倍。高压功率集成电路是半导体产业的一个重要分支,在汽车电子、电源管理、高压驱动、航天航空、武器装备里有着广泛

2016-03-12 14:12:31

微电子技术有限公司开发的BSDOT器件,在相同面积下将LDMOS的静电防护潜能提高一倍。高压功率集成电路是半导体产业的一个重要分支,在汽车电子、电源管理、高压驱动、航天航空、武器装备里有着广泛

2016-04-06 09:24:23

本文针对LDMOS 器件在ESD 保护应用中的原理进行了分析,重点讨论了设计以及应用过程中如何降低高触发电压和有效提高二次击穿电流,结合实际工艺对器件进行参数优化,得到了

2009-12-14 09:48:51 35

35 本文研究了在CMOS 工艺中I/O 电路的 ESD 保护结构设计以及相关版图的要求,其中重点讨论了PAD 到VSS 电流通路的建立。关键词:ESD 保护电路,ESD 设计窗口,ESD 电流通路Constru

2009-12-14 10:45:54 55

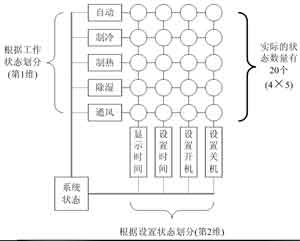

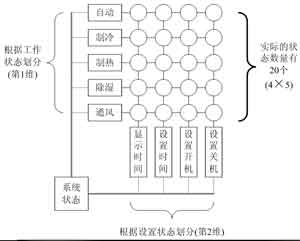

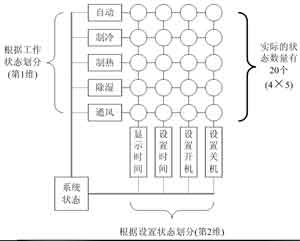

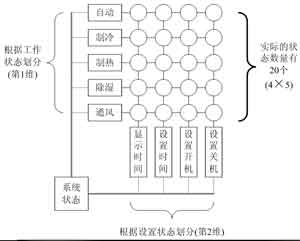

55 状态机思路在单片机程序设计中的应用

状态机的概念状态机是软件编程中的一个重要概念。比这个概念更重要的是对它的灵活应用。在一个思路清晰而且高效的程序中,

2009-02-09 11:25:13 10559

10559

状态机思路在单片机程序设计中的应用

状态机的概念

状态机是软件编程中的一个重要概念。比这个概念更重要的是对

2009-03-18 15:00:02 1523

1523

摘要:LDMOS RF功率放大器因其极高的性价比在GSM和CDMA基站市场占据了主导地位。使用LDMOS放大器时,保证高性能的一个关键因素是补偿栅极偏置电压,以在温度变化时保持恒定的静态

2009-04-28 13:54:12 1024

1024

什么是RF LDMOS晶体管

DMOS主要有两种类型,垂直双扩散金属氧化物半导体场效应管VDMOSFET( vertical double-diffused MOSFET)和横向双扩

2010-03-05 16:22:59 7379

7379 本文介绍采用直接检测LDMOS 漏端电压来判断其是否过流的设计方案,给出了电路结构。通过电路分析,并利用BCD 高压工艺,在cadence 环境下进行电路仿真验证。

2011-08-17 15:24:44 2963

2963

本内容详细介绍了 LDMOS 功放温度特性及温补电路设计

2011-08-18 17:29:27 62

62 LDMOS( Laterally Diffused Metal Oxide Semiconductor)横向扩散金属氧化物半导体)是为900MHz蜂窝电话技术开发的

2011-12-01 10:50:56 10926

10926

与双极型晶体管相比,LDMOS管的增益更高,LDMOS管的增益可达14dB以上,而双极型晶体管在5~6dB

2011-12-01 11:21:09 4697

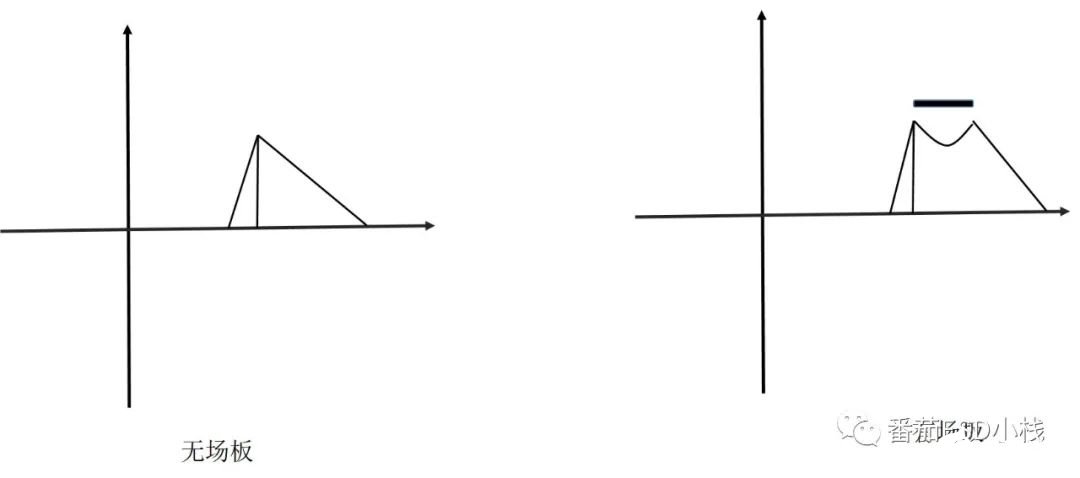

4697 场板是高压LDMOS中普遍使用的一种结终端技术,对单阶梯LDMOS场板的长度、其下方氧化 厚度以及场氧侵蚀厚度等参数进行了模拟和分析, 在此基础上设计了一种新型体硅双阶梯场板LDM

2011-12-01 14:08:10 40

40 提出了具有n 埋层PSOI(部分SOI) 结构的射频功率LDMOS 器件. 射频功率LDMOS 的寄生电容直接影响器件的输出特性. 具有n 埋层结构的PSOI 射频LDMOS ,其Ⅰ层下的耗尽层宽度增大,输出电容减小,漏

2011-12-01 14:13:43 38

38 分析了LDMOS(lateral DMOS) 在一次雪崩击穿后的局部电热效应. 提出并证明了等温分析和电热分析分别得到的LDMOS 的触发点是不同的;分析了局部晶格温度在空间上的分布特点;并提出晶格温度

2011-12-01 14:15:02 22

22 这是有关于esd测试在汽车电子产品安全可靠性能中的重要性体现。

2016-05-24 14:14:47 3

3 在PCB板的设计当中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。在设计过程中,通过预测可以将绝大多数设计修改仅限于增减元器件。通过调整PCB布局布线,能够很好地防范ESD。以下是一些常见的防范措施。

2016-12-07 01:07:11 2212

2212 LDMOS (Lateral Diffused MetalOxide Semiconductor Transistor,横向扩散金属氧化物半导体)以其高功率增益、高效率及低成本等优点,被广泛应用

2017-10-13 10:59:17 13

13 随着集成电路的发展,尤其是智能功率集成电路的发展,对功率器件提出了越来越高的要求。LDMOS由于它的电极均可以在器件的表面引出,因而可以与主流的VLSI集成电路丁艺技术相兼容,成为了功率集成电路

2017-11-02 14:32:49 12

12 ,结果表明,在保证LDMOS器件参数不变的条件下,采用深阱工艺可使其击穿电压提升50%以上。 LDMOS (Lateral Diffused MetalOxide Semiconductor

2017-11-23 06:44:49 878

878

LDMOS晶体管的应用,也使得LDMOS的技术不断成熟,成本不断降低,因此今后在多数情况下它将取代双极型晶体管技术。与双极型晶体管相比,LDMOS管的增益更高,LDMOS管的增益可达14dB以上,而双极型

2017-12-08 20:01:09 69062

69062

在PCB设计 中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。在设计过程中,通过预测可以将绝大多数设计修改仅限于增减元器件。通过调整PCB布局布线,能够很好地防范ESD。

2018-11-19 15:34:47 6776

6776 如果把静电当做突如其来的洪水,那ESD整改的基本思路可以概括为三字“堵”“防”“疏”。 “堵”顾名思义就是把ESD堵在产品的外面,使之不能进入到产品的PCB上,例如:将金属外壳的地与PCB的地完全

2019-01-26 16:18:36 1391

1391 ,在保证LDMOS器件参数不变的条件下,采用深阱工艺可使其击穿电压提升50%以上。 LDMOS (Lateral Diffused MetalOxide Semiconductor Transistor

2020-09-25 10:44:00 0

0 通信系统中开关电源EMC设计思路及解决方法

2021-06-18 10:09:19 21

21 部署中逐渐取代 LDMOS。 在本系列的第一部分《5G 和 GaN 系列之一:全面了解 Sub-6Ghz 大规模 MIMO 基础设施》中,我们回顾了在全国范围内推动 5G 实施的大规模 MIMO 技术。尽管毫米波频率应用的潜力最终会显现,但在未来几年,5G 服务将主要采用 6GHz 以下频段传输。为实现

2021-07-30 09:51:33 3006

3006 正确理解ESD单元在一个器件中是如何实现的,设计人员就能通过适当的电路设计大大扩展放大器的生存范围。

2022-09-05 10:07:19 1261

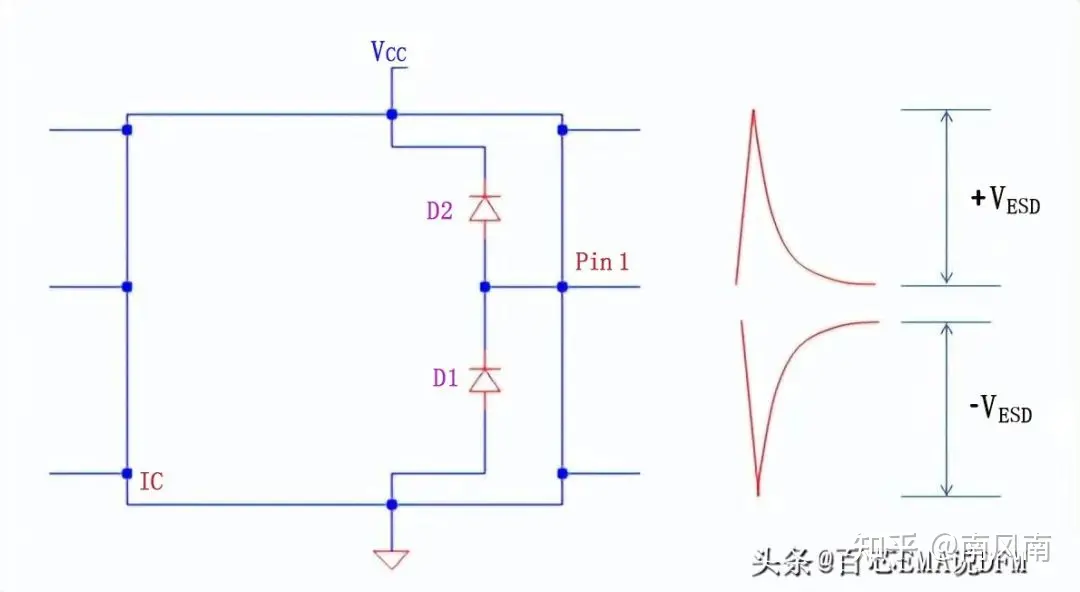

1261 ESD设计在芯片的可靠性中尤为重要,而其中电源的ESD钳位电路的设计对芯片的ESD表现的影响更为显著。本文简单介绍了电源的ESD钳位电路是如何影响芯片的ESD工作,以及介绍一种常用的电源ESD钳位电路。

2022-12-02 17:05:29 7548

7548

LDMOS RF功率放大器因其极高的性价比在GSM和CDMA基站市场占据了主导地位。使用LDMOS放大器时,保证高性能的一个关键因素是补偿栅极偏置电压,以在温度变化时保持恒定的静态电流。Maxim

2023-02-14 10:50:08 1737

1737

目前主流的ESD-NMOS有两大设计思路:GGNMOS(Gate Ground NMOS),GCNMOS(Gate Couple NMOS)。

2023-05-16 16:44:46 19663

19663

IEC61000-4-2。最重要的是,可以将外部保护器件置放在连接器或端口处,在ESD进入电路板之前就有效的抑制ESD事件的发生。

2021-12-14 05:17:19 2009

2009

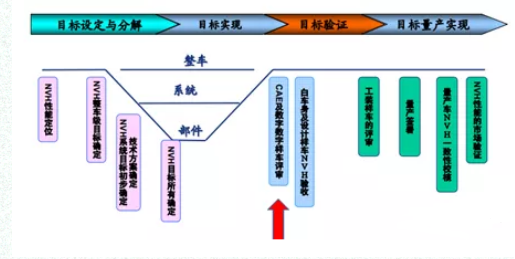

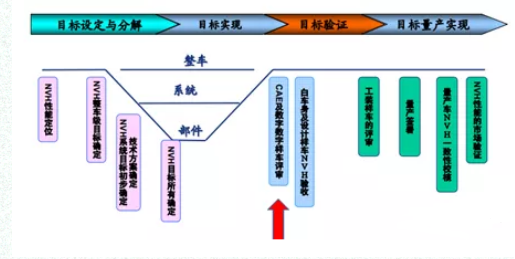

本文向读者朋友介绍 一套NVH仿真在整车开发中的分析方法和思路 ,如有不当,欢迎专家老师批评指正共同进步。

2023-07-07 10:47:44 6448

6448

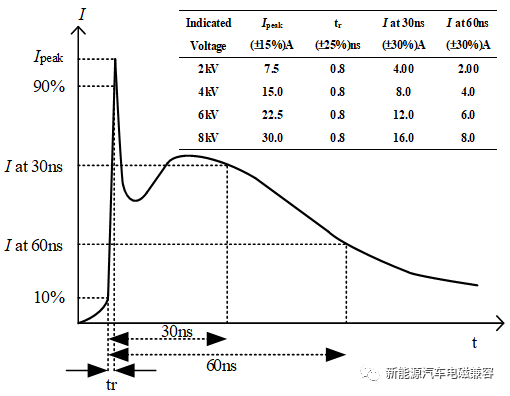

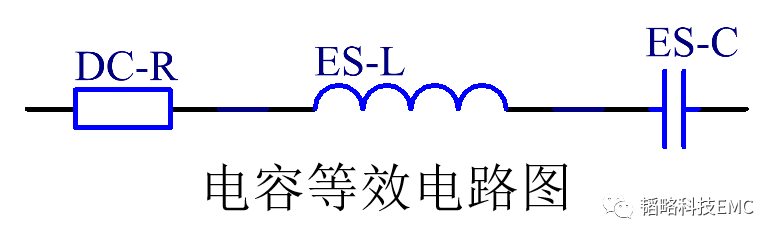

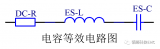

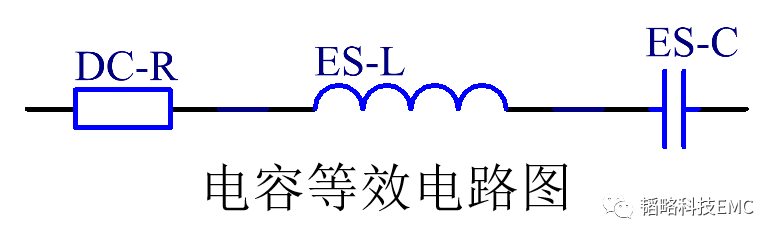

电容是构成电路的基本器件之一,也是在EMC整改手段中最便利、最有效和成本最低的手段之一。而在ESD测试中,我们会遇到一些比较明显的测试现象,比如机器重启或者屏幕闪屏,而这些现象有时候只需要加一个电容就能解决。本篇文章就电容的这个妙用进行探讨分析。

2023-10-09 11:29:45 1306

1306

好像任何一个行业的EMC都离不开ESD测试, ESD问题排查中,最重要最难的无疑是静电路径问题了。 本次就和大伙稍微探讨下ESD电流路径的分析,哪怕在为大家排查静电问题的时候提供一丝丝有益的思路,我就觉得没有白写。

2023-10-17 15:55:47 3777

3777

ESD静电整改有什么基本思路?|深圳比创达电子EMC

2023-11-02 10:08:46 1371

1371 电容在ESD测试整改中的妙用

2023-12-07 09:44:30 1348

1348

ESD(Electrostatic Discharge)即静电放电,是当带电体上的电荷通过接触、电击或感应突然流至另一个物体上的现象。在电子制造业中,ESD被认为是电子产品和元件的主要破坏原因

2024-02-16 09:50:00 12244

12244 嵌入式开发过程中,UART、 CAN、 USB等通信基本离不开通信协议。 下面给大家分享一种通信协议(MAVLink)在应用编程中的编程原理和思路。

2024-03-08 12:45:20 2060

2060

今天给大家分享的是:在电路设计和PCB设计如何防止ESD损坏设备。 在电子行业中,保护设备免受ESD损坏是必须要注意的。静电放电(ESD)是一种非常高的电压尖峰,很容易损坏集成电路和低功率半导体等

2024-03-23 16:49:03 1600

1600

一种LDMOS场效应管及其制备方法本发明涉及半导体器件设计领域,具体涉及一种LDMOS场效应管及其制备方法。在当前半导体行业竞争日趋激烈的背景下,LDMOS场效应管因其在高压应用中的优越性能而受到

2024-04-13 08:38:06 1004

1004

场效应晶体管),广泛应用于无线通信、广播电视、雷达、医疗和工业等领域。LDMOS以其低失真、高效率、高输出功率、高可靠性和低成本等优点,在功率放大器的设计中占据了重要地位。以下是对LDMOS的详细介绍,包括其结构、优点、应用领域及发展趋势。

2024-08-23 14:03:04 7568

7568 器件,作为保护电子设备免受静电损害的重要组件,在工业自动化中扮演着至关重要的角色。 ESD器件的定义和作用 ESD器件是指用于保护电子电路免受静电放电损害的电子元件。它们能够在电路中吸收和耗散静电能量,从而保护敏感的电子组件。ESD器件的主要作用包括: 保护

2024-11-14 11:26:28 2632

2632

电子发烧友App

电子发烧友App

评论