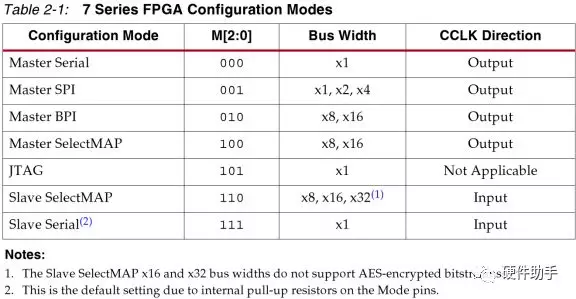

本文主要介绍Xilinx FPGA的配置模式。

2021-01-01 10:12:00 21578

21578

AXI接口虽然经常使用,很多同学可能并不清楚Vivado里面也集成了AXI的Verification IP,可以当做AXI的master、pass through和slave,本次内容我们看下

2023-07-27 09:19:33 633

633

`FPGA 上电配置时候IO口会有一个短暂的3.3V 10ms 的电平,导致我控制端出现问题,我想问下如何可以避免这个电平`

2020-11-23 10:31:40

设计、 时钟设计、乒乓操作设计等重要设计方法和技巧。6.掌握软件无线电设计精髓,而且能够独立的利用FPGA开发设计高速数字化无线通信收发信机 。 宽带中频带通采样软件无线电结构软件无线电发射机中FPGA软件功能框图软件无线电接收机中FPGA软件功能框图[hide][/hide]

2009-04-18 08:53:11

FPGA上电瞬间IO管脚输出的高电平怎么消除呢?

2023-04-23 14:48:08

API函数实现JTAG to AXI Master的读写通过调用SDK里的API函数,可以实现通过JTAG线与FPGA内部逻辑通信。即在FPGA内部例化SDK里的IP(JTAG转localbus或者

2020-09-27 10:45:13

请教关于7系列FPGA的供电(1)如果不用GTX和XADC模块,那么MGTAVTT/MGTAVCC/VCCADC等等电源可以不供电吗?(2)虽有上电顺序说法,但是FPGA的各供电可以同时上电吗?~谢

2015-05-13 20:57:36

FPGA在软件无线电中的应用本文结合各种实际测试介绍了罗德与施瓦茨公司的手持式频谱仪R&S FSH在发射机与天馈线测试、无线电干扰查处以及电磁兼容诊断测试中的应用。

2012-08-12 11:55:19

FPGA在软件无线电中的应用是什么

2021-05-06 06:34:38

Artix 7板上编程SPI Flash(N25Q256 3.3v)时,尽管闪存编程成功,但在Artix 7板上电时,FPGA无法从闪存启动。我必须按下FPGA_PROG_B按钮&只有

2020-08-12 09:31:34

FPGA程序写完编译已用94%的资源。下载没有问题,上电后,有时正常运行,有时一上电没有现象,示波器看管腿的波形也没有,怀疑FPGA没有工作,有时epcs4的程序没有正确下载。量了FPGA的供电也都正常。到底是什么问题呢?

2015-01-08 15:18:37

连接:图 1开发板上电,在Windows下点击“开始菜单 -> Xilinx Design Tools -> ISE Design Suite 14.7 -> ISE Design

2020-09-25 09:57:45

cyclone fpga jtag突然不能下载程序,测量了一下电压,发现上电后 ,nstatus管教一直是低电平,其他供电正常 ,这是为什么呢?求帮忙解答,谢谢了

2016-09-27 20:40:03

如上,fpga开发版上电后有个红色的灯常亮了(正常情况下是闪烁的),现在也连接不上电脑,是板子坏了吗?有没有大神有过经验?求告知。

2023-06-01 14:55:08

板子采用的是master—series模式1.板子之前是好用的(用了有6个月了);2.目前单独配置fpga是成功的,fpga—done这个管脚在配置成功时变高;3.单独配置prom时也是成功的(当我

2014-11-12 16:04:30

我第一次做FGPA,PCB完全完成,现在是上电FGPA就烧了,但是不知道从什么地方下手,求大神指教,从哪开始调试。

2014-11-11 10:39:18

- 2.5VVCCO_35 - 2.5V连接到I / O bank的一些外部电路在2.5V FPGA电源轨之前上电(这超出了我的控制范围)。这会以奇怪的方式导致2.5V FPGA电源轨斜坡,请参考附图。基本上2.5VFPGA

2020-07-30 09:51:29

你好,ADI工程师,我现在想用AD9516-4时钟芯片产生一个200M的时钟,给FPGA用。当我单独测试AD9516-4时,能够产生200M时钟,并且多次上电依然可以,但是当我把fpga及其外围电路

2018-12-20 14:15:47

学习的时候了解到FPGA的多路供电要求一定的上电断电顺序,目前在搞Altera的Cyclone IV系列的FPGA,主要有内部逻辑供电VCCINT,PLL供电VCCD_PLL,IO口供电VCCIO等

2017-05-18 22:36:29

我在 S32K144 MCU 上使用 CSEc 外围设备,在配置 MASTER ECU KEY 时偶尔会出现错误(90% 的时间工作正常):第一次配置 MASTER_ECU_KEY 时,CSEC

2023-03-27 08:53:26

本次发布 Gowin SPI Master IP 和 Slave 参考设计。Gowin SPI Master IP 和 Slave 参考设计可在高云官网下载,参考设计可用于仿真,实例化加插用户设计后的总综合,总布局布线。

2022-10-09 08:01:03

CABLE FOR LIN MASTER TO EVAL

2024-03-14 22:01:39

/Virtex-6/7 Series FPGA PCI Express Block Endpoint模块,基于该模块设计了PCI Express Endpoint Master DMA.1. Master

2014-08-23 13:15:30

Endpoint模块,基于该模块设计了PCI Express Endpoint Master DMA.1. Master DMA位于FPGA内部,FPGA执行DMA操作,主要包括两大功能DMA Write

2015-06-21 13:38:12

、Erase、Program Page、Read Page、Program Page Cache、Read Page Cache4. 支持上电自动坏块检测5. 支持坏块表动态更新6. 支持坏块管理(BBM

2012-05-21 09:32:15

1.同样的板子,用过好多块,都没有问题,就这块无法加载,应该不是PCB设计问题。2.我设计的是主串加载模式(Master Serial)。硬件上将FPGA的M2~M0直接接到GND上。3.上电以后

2015-08-15 09:20:26

设计了PCI Express Endpoint Master DMA.1. Master DMA位于FPGA内部,FPGA执行DMA操作,主要包括两大功能DMA Write(FPGA-->内存

2014-03-01 18:11:32

包含ETX(或者x86等CPU)以及FPGA,由于一般PCI接口通过FPGA来控制实现,所以如果系统上电后FPGA的配置、初始化时间太长势必影响到板卡CPU对于PCI总线接口的访问,而且大部分情况下系统

2015-01-22 14:41:34

嗨, 我正在开发一种设计,我们的主板有1个virtex5 fpga和9个从属卡,每个都有1个V5 fpga。我想同步所有9个从卡的操作。我还希望主卡和从卡之间的数据传输速率为300-400Mbps

2019-01-30 06:52:36

之后最高只能到400M,在全国电设里能用上么?从今年的题目来看,一届的频率比一届要高,以后的题目估计不会再出现低频题目了。我知道FPGA是并行操作,看过那个很多人说,ALTERA的芯片最高时钟频率也只能到200M,在高的话处理效果就不会很好。我就是 想问如果用FPGA的这款 芯片最高可以处理多高频率的信号?

2015-09-13 11:25:37

, Virtex-5/Virtex-6/7 Series FPGA Serial RapidIO Block Endpoint模块,基于该模块设计了Serial RapidIO Endpoint Master

2015-11-11 15:06:39

的问题是,我可以在FPGA内部使用这个时钟作为FPGA和电路板的主时钟吗?我有一个应用程序,我想在板上尽可能少的部件,我不关心主时钟频率是什么,只要它是1-50MHz时钟。要使用CCLK我必须有一个PCB

2019-05-07 13:40:54

你好,我可以在LS1043A上做localbus总线和spi master的开发吗?

2022-01-06 06:30:49

产生的问题是在FPGA上电启动时这部分引脚总是会快速的闪过一次高电平才恢复低电平,请问应该怎么做才能使避免高电平会闪一次的这种情况?程序中因为需要复位时保持输出结果,所以不能使用复位信号,关键代码

2023-04-23 14:53:05

大家好,我们正在设计一个基于kintex-7 FPGA的电路板。该板具有DDR,QDR,BPI,以太网,UART等外设。我们有一个关于加电排序的查询。有没有要求外围IC在FPGA上电之前应该上电,反之亦然。感谢致敬Tarang JIndal

2020-07-31 11:32:50

BeRadio,基于FPGA的软件定义无线电参考设计。 SDR通常是具有在固件和软件中定义的主要功能(模/解调,滤波等)的无线电,数字域

2019-07-04 10:09:20

如何控制FPGA各电源的上电顺序呢?请教一下大神

2023-03-27 13:48:32

大家下午好,我计划使用主fpga板的IO引脚配置目标cpld板,即菊花链。我使用主fpga板的IO引脚连接cpld的JTAG头。如何编程master fpga的IO引脚来配置目标cpld?请发送与此相关的任何文件....谢谢问候Vimala

2020-03-24 06:43:09

你好,在我们的研究中,我们正在探索FPGA器件上SRAM的上电状态的固有随机性。因此,我们现在正试图在启动后从aVirtex-5器件读出分配的RAM值。但是,根据“Virtex-5 FPGA配置指南

2020-06-18 09:26:09

最近在用AD7768在做数据采集,采用FPGA控制和处理转换后的数据,但是将FPGA和AD7768端口链接后,每次上电AD都会发烫 ,断开连线后正常,这是怎么回事

2018-08-06 09:17:15

包含ETX(或者x86等CPU)以及FPGA,由于一般PCI接口通过FPGA来控制实现,所以如果系统上电后FPGA的配置、初始化时间太长势必影响到板卡CPU对于PCI总线接口的访问,而且大部分情况下系统

2015-01-20 17:37:04

大家好,我在更新master上的某些值时遇到问题,我正在使用bluenrg-1我有一个设备作为主设备而另一个设备作为从设备。奴隶有一个按钮,我已连接,每次按下从属按钮时,调用函数

2019-02-20 13:37:54

本人做课设,想用FPGA输出一个方波作为时钟信号,使用FPGA的是Altera公司的EP1C12Q240I7,配置芯片是EPCS4I8,我用QuartusII下载了程序之后,发现只有上电和手动复位后

2016-12-08 16:20:03

求助:基于SRAM结构的FPGA上电瞬间电流大小如何去评估,上电瞬间的电流很大,比正常工作电流大很多,如何去评估?资料上没找到描述,感谢讨论

2019-04-18 16:50:00

本帖最后由 Razer 于 2013-10-17 10:11 编辑

FPGA+CY7C68013A,两个片子都没程序,觉得在无程序的情况下上电,插上USB数据线,如果线路正确,PC应该能反应出

2013-10-17 09:52:42

现在的FPGA还严格要求上电时序吗?想请教一下大家

2017-09-26 15:39:07

最近在用AD7768在做数据采集,采用FPGA控制和处理转换后的数据,但是将FPGA和AD7768端口链接后,每次上电AD都会发烫 ,断开连线后正常,这是怎么回事

2023-12-11 07:56:47

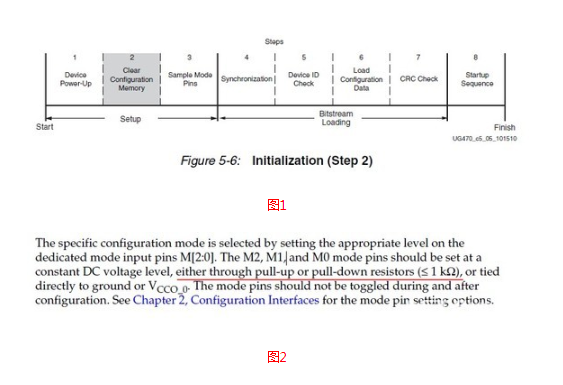

目前,大多数FPGA芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常的运行

2019-07-18 08:10:11

大家好, 谁能告诉我Spartan-3AN的FPGA上电和闪存配置之间的时间间隔?谢谢RGDS以上来自于谷歌翻译以下为原文Hi All, Could anyone tell me the Time

2019-06-27 08:15:46

请问CPLD/FPGA上电初始时IO口的状态是怎么样的呢?

2023-04-23 14:26:44

软件无线电设计中ASIC、FPGA和DSP怎么选?

2021-04-28 06:09:22

概述EasyGo FPGA Solver是EasyGo开发的专门部署在FPGA 硬件上的解算器软件。根据不同的应用需求,会有不同的FPGA Solver 选择

2022-05-19 09:21:43

The PCA9541 is a 2-to-1 I2C-bus master selector designed for high reliability dual masterI2C-bus

2009-11-11 12:09:46 21

21 Platform Flash In-System Programmable Configuration PROMs

When the FPGA is in Master Serial mode, it generates aconfiguration clock that d

2010-04-15 11:12:21 81

81 dsp fpga 电路 打标机上用的主板

2016-06-27 15:24:08 7

7 arduino-esp32-master开发环境设置用的库

2017-08-07 08:53:17 25

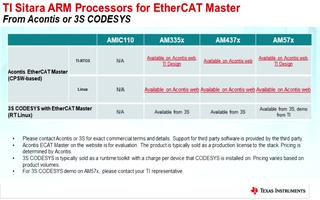

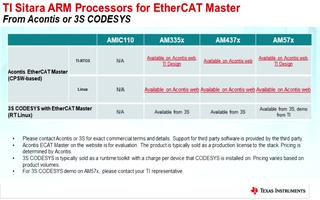

25 基于AMIC产品的工业通信总线设计方案-1.4 EtherCAT Master

2018-08-10 00:45:00 5541

5541 依据SPI同步串行接口的通信协议, 设计一个可配置的、高度灵活的SPI Master 模块,以满足正常、异常及强度测试要求。利用Verilog 语言实现SPI接口的设计原理和编程思想。

2018-11-05 17:42:38 10793

10793

基于AMIC产品的工业通信总线设计方案-1.4 EtherCAT Master

2019-05-08 06:16:00 3647

3647

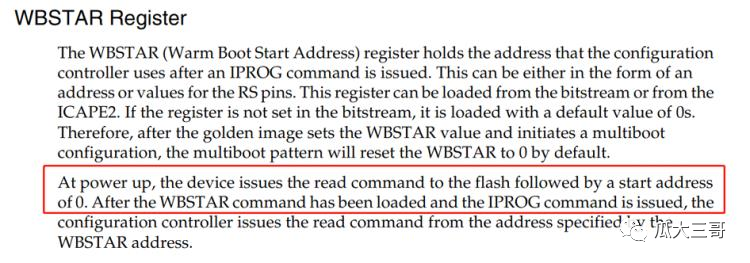

问题是FPGA使用JTAG口能把程序到FPGA,FPGA也能跑得动,当配置模式选择MASTER SPI时,通过JTAG口下载也可以下载成功,但是问题是重新上电发现FPGA无法读出FLASH的配置文件。

2020-03-15 16:08:00 2685

2685

在 AMBA 系列之 AXI 总线协议初探 中,了解到 AXI 总线交互分为 Master / Slave 两端,而且标准的 AXI 总线支持不同的位宽,既然是总线,那么必须要支持总线互联,多 Master,多 Slave的场景

2022-02-08 11:44:02 12802

12802 使用GA-master的FOPID调谐器

2021-03-24 10:13:21 0

0 PCS7下ASCII模式Modbus Master的实现说明。

2021-04-23 09:38:49 8

8 对FPGA进行上板调试时,使用最多的是SignalTap,但SignalTap主要用来抓取信号时序,当需要发送信号到FPGA时,Jtag Master可以发挥很好的作用,可以通过Jtag Master对FPGA进行读写测试

2022-02-16 16:21:36 1900

1900

ardupilot master程序分享

2022-08-24 09:36:23 0

0 Gowin SPI Master 和 Slave IP 用户指南主要包括功能简介、信号定义、

工作原理、GUI调用等,旨在帮助用户快速了解Gowin SPI Master IP和Slave

参考设计的特性及使用方法。

2022-09-15 10:13:11 0

0 Gowin I2C Master 和 Slave 用户指南主要包括功能简介、信号定义、工

作原理、实例化等,旨在帮助用户快速了解 Gowin I2C Master IP 和 Slave

参考设计的特性及使用方法。

2022-09-15 10:07:01 1

1 FPGA端实现SDIO Slave功能 a.FPGA将SDIO Master发送的2KByte数据保存至BRAM。 b.SDIO Master发起读数据时,FPGA从BRAM读取2KByte通过SDIO总线传输给SDIO Master。

2022-11-10 12:22:18 1913

1913 ElasticSearch(下文简称ES)集群中,每一台服务器都有自己的角色,有一部分服务器可以设定为候选Master(至少是3台),也就是说这些服务器已经具备成为Master角色的能力,但是具体谁最终成为Master是要通过选举才可以。

2023-02-23 09:54:31 2128

2128 AXI接口虽然经常使用,很多同学可能并不清楚Vivado里面也集成了AXI的Verification IP,可以当做AXI的master、pass through和slave,本次内容我们看下AXI VIP当作master时如何使用。

2023-07-27 09:16:13 792

792

电子发烧友App

电子发烧友App

评论