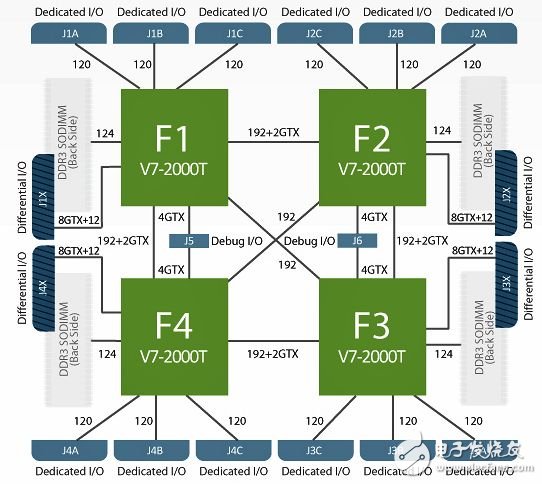

S2C Inc.今日宣布将最新的原型验证平台Quad V7加入其V7 TAI Logic Module系列。Quad V7 是基于Xilinx Virtex-7 2000T可编程3D IC的最新一代SoC/ASIC原型硬件。

2013-01-23 11:28:14 2068

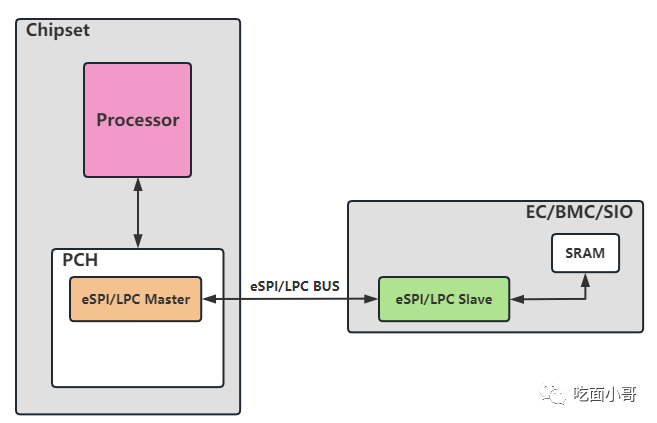

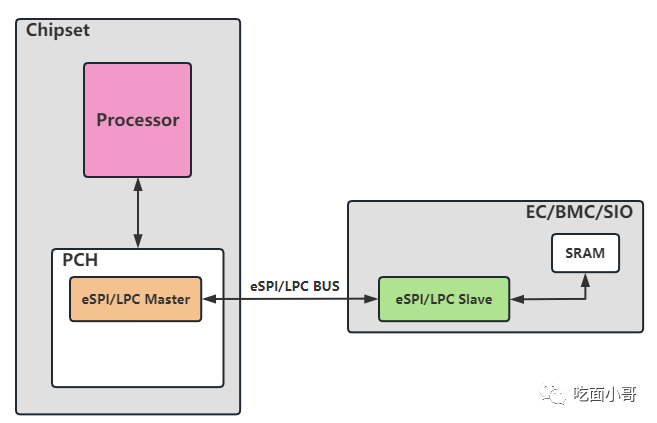

2068 ShareMemory,顾名思义就是共享内存。这个概念在很多计算机系统中都存在,本文特指 EC SRAM 映射到 CPU Memory 空间的共享内存设计。

2023-11-18 15:11:36 599

599

2022年6月28日,国微思尔芯面向全球客户正式发布芯神瞳自动原型编译软件Player Pro-7(PPro-7)。新版本针对大规模芯片设计提供了有效的解决方案,拥有更高的编译效率和更好的分割性能

2022-06-28 10:21:59 827

827

性能。 “新版本的TAI Player Pro提高了我们整个产品线的能力与强度,” S2C 首席执行官林俊雄先生表示,“它是一款功能强大的配置工具 – 我们的一位客户最近用它成功的将高达3亿门的逻辑设计分割

2019-07-02 06:23:44

嗨,我想问一下Virtex-2-Pro是否有内置的系统监视器。谢谢。阿卜杜拉以上来自于谷歌翻译以下为原文Hi, I want to ask that Virtex-2-Pro has a built-in system monitor or not. Thank you.abdullah

2019-01-10 11:01:12

你好,,我做的项目涉及从fpga向任何手机发送消息任何gsm调制解调器...所以需要接口Virtex 2Pro和GSM调制解调器..因为我设计了一个工作在9600波特率的UART ..当我通过

2020-06-13 20:28:50

我只是想知道,virtex II PRO支持来自PROM的MULTIBOOT ??在iMPECT中的多引导修订部分中没有这样的设备选项显示为virtex II pro ..我无法在virtex中为多重引导制作PROM mcs文件II PRO..Plz建议我......谢谢...期待回复......

2020-06-11 14:51:07

【说明】程序将CAN引脚重映射到了PD0和PD1引脚上。由于打开了Loopback模式,所以这两个引脚不需要接任何器件,悬空就行。必须要设置CAN消息过滤寄存器(CAN filter

2021-08-19 08:47:15

我目前正在尝试将Linux添加到Virtex4上的一个PPC405上。我添加了软件平台设置但不确定如何实际启动和运行内核。有什么建议么?我已经看到了Virtex Pro 2的一些方法,但我似乎无法A

2018-09-30 11:09:28

嗨,大家好,我遇到了Xilinx ISE映射过程的棘手问题。当我综合我的设计时,我得到了一些FPGA资源的利用。虽然在映射过程中映射到FPGA上的LUT时,所有利用率都会达到0%。他很可能是由于

2020-06-13 09:57:50

CC3200 的PWM是如何映射到引脚的?SetupTimerPWMMode(TIMERA2_BASE, TIMER_B,[size=1em](TIMER_CFG_SPLIT_PAIR | TIMER_CFG_B_PWM), 1);[size=1em][size=1em]

2016-04-19 10:51:23

拷贝到对应ram内存中,当在线标定时,会直接操作ram中相应的地址,以实现参数在线修改。请问ESP32如何实现Flash到ram重映射这种功能呢?通常的做法是使用重映射,或者使用mmu。但是esp32的mmu无法将flash地址重映射到指定的ram区域里。

2023-02-13 08:42:07

EVAL BOARD VIRTEX II PRO XLVDS

2023-03-30 11:49:32

我正在使用 mcxn9XXbrk_face_detection 参考项目研究 MCX-N9XX-BRK。而且我不知道在哪里连接调试端口。它映射到 LPUART6。

我想知道 LPUART6 映射到的物理引脚以及在哪里可以找到更多信息。我在用户手册或源代码中找不到任何信息。

2023-06-12 08:52:02

到发送天线”过程的两个的子过程。

层映射首先按照一定的规则将码字流重新映射到多个层(新的数据流),参见P68表3-23、3-24。(注:层的数量小于物理信道传输所使用的天线端口数量P)。

预编

2023-05-16 15:02:47

能否同时对应同一个BAR的地址?( ib0_bar = 1 )

2、多组win能否将数据映射到重叠的内存地址上?(举例:ibw1将BAR地址映射到0x0c10_0000,ibw2也把数据映射到0x0c10_0000,是否会有错?)

2018-06-21 07:28:30

我现在用PID做温控,我实际是用控制可控硅的过零后的触发时间,来调节功率。但是在PID输出一个量,将其映射到过零触发时间上,出现了问题。例如:AC220,控制范围在10mS之内,温度越高,可控硅导

2015-10-14 15:00:50

RAM Saver Pro【内存自动调整工具】v9.0 绿色中文注册版电脑执行一段时间后,内存可用资源会变少,而内存管理工具 - RAM Saver Pro,能够随时自动调整电脑内存,让系统保有足够

2009-03-02 12:23:14

我使用的是 STM32G0B1CC,我正在尝试将地址 0x00000000 重新映射到 SRAM,如下所示:__HAL_RCC_SYSCFG_CLK_ENABLE

2022-12-22 06:18:17

EXTI寄存器的中断控制器章节时,寄存器中没有位映射PORT I来中断向量。第12.6章中有一条注释说“端口G,H和I仅适用于中型和高密度设备”我的问题是如何将GPIO映射到例如PI2到外部中断

2018-09-14 10:04:34

我尝试通过以下(简化的)顺序使用 TC33X 将数据缓存映射到 RAM 区域:

CPU_DCON0 = 2

MTU_CLC = 0 MTU_MEMMAP |= 1

在软件闪烁且调试器保持连接

2024-01-25 06:23:38

嗨,我在XUP Virtex 2 Pro Board上工作。我使用Win Vista Home Premium。我安装了ISE 10.1但无法配置设备,因为它不安装驱动程序。但是同样的程序适用于

2018-11-20 14:15:46

本章小结第5章 ISE 6的辅助设计工具5.1 概述5.2 IP核生成工具5.3 布局规划器5.4 FPGA底层编辑器5.5 集成化逻辑分析工具5.6 XPower功耗分析工具5.7 本章小结第6章

2012-02-27 14:43:30

在2440开发板上将一副BMP图片显示到LCD上(不用GUI),我的做法是将BMP图片用mmap()函数映射到内存中,在将其读到Framebuffer设备中显示(frambuffer有驱动),映射

2019-02-25 12:42:59

如题,用某powerpc板作为RC,C6678作为EP,目前已经能用RC枚举到6678,且能通过PCIE映射到C6678的DDR3、L2等地址,并能正常读写。

现在我想用RC映射到6678的寄存器(比如0x02600000),但是发现往里面写值失败,请教各位专家如何解决?

2018-06-21 04:26:46

为什么Steppingstone映射到nGCS0?

2013-10-11 18:19:55

BOOT0:0时为主闪存存储器启动,主闪储存器0x08000000会映射到0x00000000BOOT0:1,BOOT1:0时为系统存储器启动,0x1FFFFF000会映射到

2019-07-29 04:35:15

消费类产品中日益增长的模拟器件数量、当今的设计规模以及先进工艺节点所面临的愈加复杂的制造约束,使得模拟设计领域对自动化设计工具的企盼更加迫切。 自动化设计工具的目标是使模拟版图设计人员能够简单自动

2019-07-08 06:00:51

在进行内电层分割时,同一网络必须是一个连续的整体,而不能分割成多个不连续块么?

2014-09-29 08:37:27

驱动程序时,我无法将配置工具 (1.6) 映射到正确的 SpiPhyUnit。我将单个 SpiJob 分配给 SpiSequence 和 SpiExternalDevice。所有作业都将在我定义为

2023-04-17 08:45:16

200 MHz时钟信号映射到输入? (我在原理图上看到它是差分的)是否有一个文件覆盖了这个?我无法在AC701文档中找到任何内容......我确实在用户指南中看到Vivado工具有一个主约束文件 - 我应该使用Vivado吗?谢谢!

2020-07-15 10:42:33

开发板是正点原子的F407,参考“启动第一个线程”创建了工程,通过板上USB_232(UART1)可以收到打印信息,如何将rt_kprintf重新映射到其它串口,例如uart2。尝试改了以下2处,发现不行。

2022-08-01 10:42:18

。对于第二个核心,我将输入/输出连接到外部端口。在ucf文件中,我将第二个核心的网络添加到与第一个核心网络相同的引脚位置。这是我的问题。我不确定这是否正确。我尝试在互联网上搜索如何将两个信号映射到同一个

2020-04-06 07:22:49

Scratch-Pad Sram(CPU5 DSPR)相关联。 在链接器脚本中,我已经映射了每个.text 部分移至其各自的 PSPR 内核。 我想知道如何将共享代码映射到 DSPR5 以及如何将其映射到其他 RAM 区域。

2024-01-24 07:26:27

cybl10563-56lqxi。程序员,PSoC miniprog3,正确识别我的设备为212019,但抱怨“HEX文件不与获取的设备匹配,请检查设备”。造物主/项目/设备选择提供了我一部分,但没有一个是212019如何将创建者设备选择映射到我的212019?还是别的地方有问题?蒂亚,李察

2019-11-06 07:32:29

如何使用CubeMax进行参数配置将端口重映射到PD0和PD1?

2021-12-02 06:20:17

如何使用半自动化设计工具。这些工具对于电源设计工程师新手和专家都很有价值。

2021-09-29 10:51:53

正如您在上图中看到的,我正在尝试设计一个电机控制器。但是 L293D 的引脚 16 需要一个 5v 输入作为 VCC1,但是 STM 给出的最大输出是 3V。我想知道如何使用无源元件将 3V 转换和映射到 5V?

2023-02-09 08:45:15

亲爱的先生我的项目需要virtex2pro上的两个串口(RS232)端口。如何在virtex2pro中使用两个串口?

2019-09-12 06:23:39

大家好,我是新手使用Xilinx板。最近我被分配了一个任务来编程VIRTEX II PRO 1152板。你能给我一个广泛的想法,从我可以学习使用它开始一些好的来源。我必须编写代码Verilog的。谢谢你期待快速回复DHIRAJ

2020-06-02 11:36:39

亲爱的大家我需要知道如何计算virtex 2 pro 30的功耗,如xpower estimatorspreadsheet(excel文件)等你的回复最好的祝福

2020-06-14 13:16:38

大家好,我正在研究一个项目,我想知道如何读取Virtex II PRO芯片的所有I / O信息。您是否可以使用iMPACT软件来帮助我(使用JTAG通信)?我需要为此制作其他东西吗?你可以通过发送

2019-01-17 11:00:30

输出是或否。按键盘上的1应输出yes,按2应输出no。我最大的问题是将我想要的信号映射到键盘。如何通过.ucf约束文件将键盘按钮映射到我的设计中的特定信号?谢谢

2020-05-15 08:28:27

逻辑门控无法映射到Vivado中的一个时钟区域时,BUFHCTRL能够复制自身并将逻辑映射到多个时钟区域吗?谢谢,雨翔

2020-07-27 14:26:34

haii需要帮助将pin映射到pic24中的计时器2,计时器充当计数器。我想计算来自该pin.RPINR3bit.T2CKR=11的每个信号脉冲;这对于将pic24fj128gb106中的计时器映射到pin RP11没关系。这样就足够写计数器配置了吗?谢谢你

2020-03-06 09:16:58

Pro提供了先进的设计分割功能,即将发布的Prodigy MulTI-Debug 模块则可以缓解 多颗FPGA 联合调试的任务。S2C 的 Prodigy FPGA 原型系统解决方案是目前市场上最全面的能帮助您实现物联网设计 的解决方案。『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

2018-08-07 09:41:23

2410上电后从0x0处执行,在bootloader中首先将ROM中的代码和数据搬到RAM中,然后如何将RAM映射到0x0处?看2410的文档,它的bank地址都是固定的。

2022-06-20 14:41:20

请教一下是不是io口的复用功能可以重映射到任何普通io还是只能映射到指定的几个普通io啊?

2020-08-13 08:00:22

用openmp时讲到,需要将共享的变量放到no cacheable的空间中。对于6678片子来讲,如果想要放到共享内存中,要么将msmc全部设为no cacheable,或者将部分msmc的空间映射到

2018-07-24 08:40:26

CCS工程的条件。场景如下:1. 4个核,运行4组不同的task,运行时用DNUM区分启动不同的task组2. 想使用相同的配置,将私有数据映射到相同的一段ram,例如(0xa0000000 开始的64M

2019-01-04 11:34:19

。我想知道什么是USB总线上的数据速率(因为它增加了额外的同步位和PIDs etc.)CX3如何将所有接口映射到USB上?如何计算吞吐量?谢谢您。

2019-11-01 11:12:22

是否有任何工具可以并行编程多个设备,并且可以使用DLL将程序员与Labview连接起来? 像TI的Gang Pro这样的东西。以上来自于谷歌翻译以下为原文 Is there any tools

2019-06-17 10:26:48

usb设计工具,本软件非常有意思。

2006-03-25 13:01:36 151

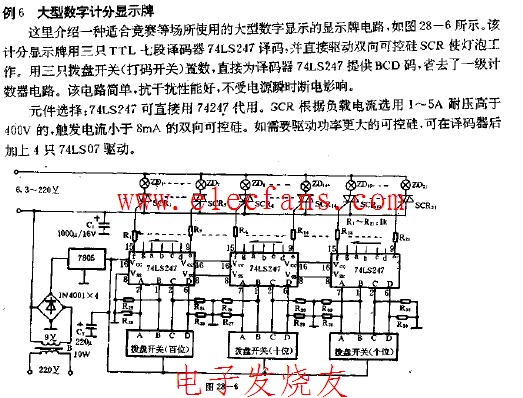

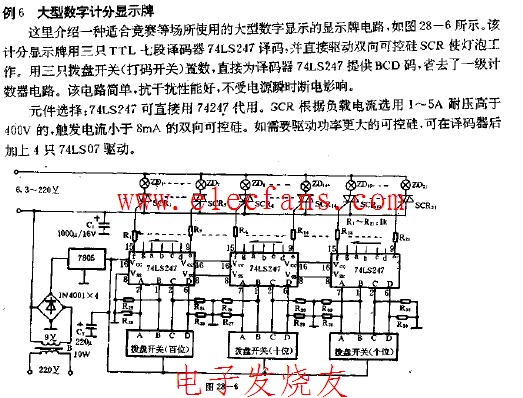

151 大型数字计分显示牌电路图是一种适合竞赛场所使用的大型数字显示的显示牌电路.

2017-06-30 17:12:26 1448

1448

S2C Inc.宣布在Altera公司的40-nm StraTIx IV现场可编程逻辑闸阵列(FPGA)基础上发布其第四代快速SoC原型工具,即S4 TAI Logic Module。

Dual S4 TAI Logic Module因配备两个Stratix IV EP4SE82

2010-07-01 08:50:39 917

917 Virtex-7 2000T FPGA的容量是市场同类最大28nm器件的2倍,而且比赛灵思最大型Virtex-6 FPGA大2.5倍。虽然2000T由4个切片组成,但它仍然保持着传统FPGA的使用模式,设计人员可通过赛灵思工具流程

2011-10-26 09:11:30 2795

2795 ,用户可使用多种不同的接口(例如PCIe、千兆以太网、HDMI、LCD和双A9 ARM处理器)进行SoC原型设计,并通过S2C的Virtex-7 TAI Logic Module系列快速搭建SoC/ASIC原型验证平台。

2013-01-30 10:39:43 1516

1516 (现更名为Prodigy逻辑模块)( TAI Player Pro 5.1原型工具可以跨多个Virtex-7 3D FPGA自动区分大规模的设计。) FPGAs Prodigy

2017-02-09 03:49:04 437

437 此方案可简化,无电缆的设计分割,最多允许四个用户同时使用。S2C公司,业内领先的 FPGA 快速原型验证系统供应商,发布了适用于超大规模设计的基于赛灵思Virtex UltraScale(VU

2018-06-29 08:09:00 4932

4932 电子发烧友网站提供《几款原型设计工具推荐.docx》资料免费下载

2017-09-26 15:08:03 0

0 值,分别形成多个候选文摘句子集;再运用多重映射策略,将多个候选子集映射到文摘句子集中,同时使用提取文本中心句的方法提高召回率。实验表明,多重映射可在短文摘提取上获得稳定的性能。在NLP&CC2015评测中,该方法的

2017-12-23 11:46:29 0

0 TI WEBENCH 的设计工具们:时钟架构工具、有源滤波器设计工具、电源设计工具、LDC设计工具、发光二极管(LED)设计工具、传感器设计工具! TI WEBENCH 设计工具,让设计轻松一点~

2018-06-13 05:25:00 5523

5523 电源系统设计工具

2018-08-06 01:13:00 3978

3978 了解如何将复杂的SoC平台映射到单个Virtex®-7 2000T FPGA

2018-11-23 06:38:00 2515

2515 华秋PCB设计分析软件-BOM自动分析智能工具

2021-07-16 15:47:44 0

0 华秋PCB设计分析软件-BOM自动分析智能工具

2021-07-16 15:37:50 0

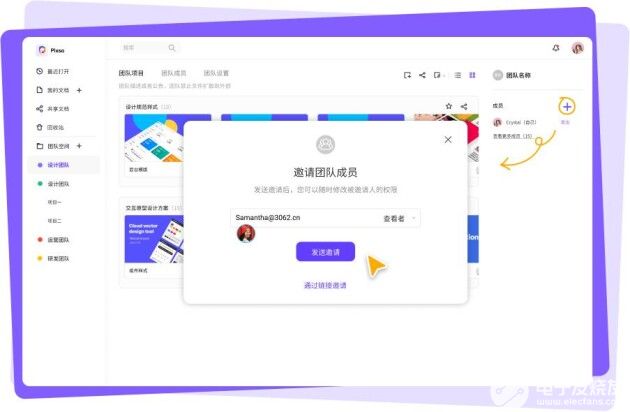

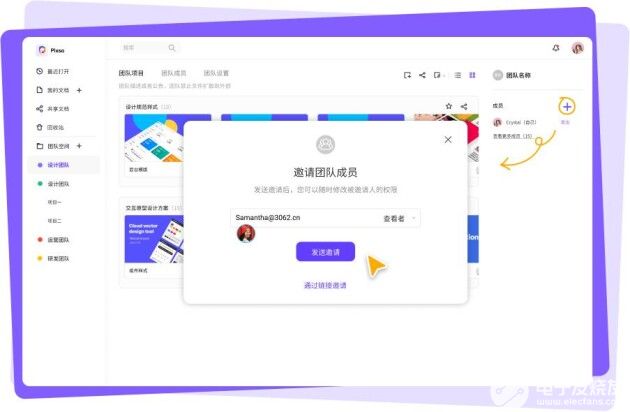

0 一款好的电脑设计工具对于设计师而言就犹如神兵利器,有了它,设计工作的开展简直如虎添翼、效率倍增,很多一闪而逝的灵感可以完美呈现给客户。下面介绍的4款全面且强大的电脑设计工具一定能祝你的工作一臂之力

2021-09-26 16:25:33 630

630

、开发、测试焦头烂额,摸不着头脑,让产品经理的威信大大降低。下面介绍的这5款软件,能够在你绘制原型图时助你一臂之力。 1.Axure RP Axure RP是一款强大的原型设计和开发人员工具,适用于任何项目的强大原型设计。无论你是创建图

2021-10-11 11:42:02 1106

1106

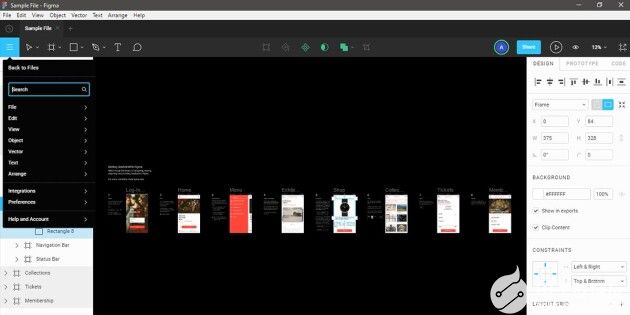

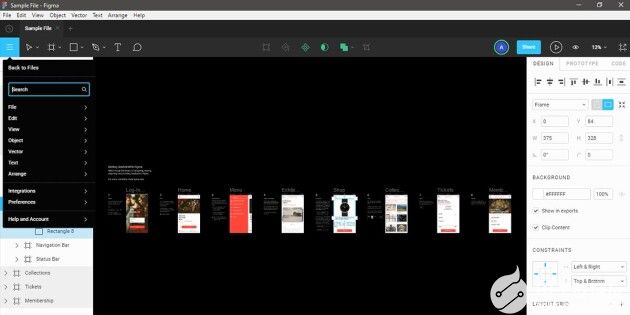

涯中不可错过的。 1. Figma Figma是一款主流原型设计工具,之所以能够成为主流,是因为它确实好用。它于 2016 年 9 月正式上线,仅用时 4 年便取得了市占率第一的成绩。这就足以说明Figma的受欢迎程度。Figma是一款全平台可使用的使用软件

2021-10-21 17:44:15 739

739

2022年6月28日,国微思尔芯面向全球客户正式发布芯神瞳自动原型编译软件Player Pro-7(PPro-7)。新版本针对大规模芯片设计提供了有效的解决方案,拥有更高的编译效率和更好的分割性能。

2022-06-28 11:10:11 845

845 思尔芯从2004年开始做原型验证系统,2022年推出第七代原型验证系统。结合原型验证完整的软件工具链,很多用户用到了百亿门级的系统。可实现自动编译与自动设计分割等功能。

2023-01-16 11:27:25 882

882 AN022 如何将0xC0000000映射到0x00000000地址运行程序

2023-02-27 18:24:39 0

0 综合工具的任务是将SoC设计映射到可用的FPGA资源中。自动化程度越高,构建基于FPGA的原型的过程就越容易、越快。

2023-06-13 09:27:06 278

278

引言Preface如何快速便捷的完成巨型原型验证系统的组网,并监测系统的连通性及稳定性?如何将用户设计快速布局映射到参与组网的原型验证系统的每一块FPGA?随着用户设计规模的日益增大,传统基于单片

2022-06-16 10:19:18 459

459

的编译效率和更好的分割性能。为高密原型验证系统逻辑矩阵LX的客户提供更佳的操作体验,并大幅提高大型SoC验证的效率。PPro-7三大优势解决大规模芯片设计痛点:对大规

2022-07-02 10:58:24 275

275

电子发烧友App

电子发烧友App

评论