S2C日前宣布他们已经开发了一种原型验证产品,即TAI Verification Module(专利申请中)。它允许使用者通过一条x4 PCIe Gen2通道到连接FPGA原型中的用户设计和用户的电脑,使得用户能够使用大量

2011-06-16 08:55:48 1785

1785 电子发烧友网讯: 本文主要讲述了TAKUMI公司的图象IP核参考设计可用于S2C原型验证平台。S2C宣布,一家总部位于日本的高级图形知识产权(IP)供应商,TAKUMI 公司,已成功在S2C基于FPGA的快

2012-07-03 13:50:45 1548

1548 据报道,Aldec公司日前正式发布HES-7新产品,HES-7原型验证板基于Xilinx Virtex-7芯片设计而成,其设计容量可从4MG扩充至96MG,单一HES-7原型验证板的最大容量为24MG(V7-2000T*2)。藉由Aldec公司所

2012-09-19 18:37:17 2152

2152

S2C Inc.今日宣布将最新的原型验证平台Quad V7加入其V7 TAI Logic Module系列。Quad V7 是基于Xilinx Virtex-7 2000T可编程3D IC的最新一代SoC/ASIC原型硬件。

2013-01-23 11:28:14 2068

2068 基于 FPGA 的 ASIC 原型可快速、准确地实现 SoC 系统建模和验证并加速软件和固件的开发。Xilinx 推出Virtex®-7 2000T 器件,使基于 FPGA 的原型得到了进一步发展

2013-03-14 14:33:00 1269

1269

什么是FPGA原型? FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能

2022-07-19 16:27:29 1735

1735 产品 IP开发 本板卡 基于Virtex7 XC7V690T-1FFG1761I,设计的PCIe 底板,板卡特点如下: 1、标准PCI-E接口,支持PCI-E 8x,支持PCI-E 3.0。 2

2016-03-11 10:57:58

原型验证---用软件的方法来发现硬件的问题 在芯片tap-out之前,通常都会计算一下风险,例如存在一些的严重错误可能性。通常要某个人签字来确认是否去生产。这是一个艰难的决定。ASIC的产品NRE

2019-07-11 08:19:24

原型验证过程中的ASIC到FPGA的代码是怎样进行转换的?

2021-05-08 09:16:18

1ASIC 验证技术.................................................11.1 ASIC 设计流程

2015-09-18 15:26:25

ASIC设计-FPGA原型验证

2020-03-19 16:15:49

) 通过本地总线、RapidIO与DSP连接; 7) 提供主FPGA所有接口代码的封装库;DSP子系统规格 1) 选用TI公司8核DSP,型号TMS320C6678,工作主频1GHz; 2) 外挂1

2019-09-06 10:15:41

FPGA原型验证已是当前原型验证的主流且成熟的芯片验证方法——它通过将RTL移植到现场可编程门阵列(FPGA)来验证ASIC的功能,并在芯片的基本功能验证通过后就可以开始驱动的开发,一直到芯片

2020-08-21 05:00:12

什么是S2C?与中国SoC事业之间有什么联系?

2019-08-02 07:17:10

Virtex 7 PCIe硬IP是否意味着FPGA内部的ASIC?或者像Tandem方法一样,在第一阶段,CPLD将PCIe初始配置加载到FPGA? (http://www.em.avnet.com

2020-05-29 12:52:09

您好,Virtex7的SERDES运行的最大频率是多少?请问,有人可以帮我这个吗?在此先感谢,最好的问候

2020-07-30 17:20:12

模数转换器AD9625的评估板AD-FMCADC3-EBZ能不能和赛灵思的Virtex7系列FPGA开发板连接,我看到他们都具备JESD204B接口,物理接口上能直接连吗?还是说需要在使用转换接口来连接?

2023-12-08 08:25:12

基于FMC的支持Virtex7系列FPGA的Full Camera Link 输出子卡 [img][/img]1、板卡概述 FMC连接器是一种高速多pin的互连器件,广泛应用于板卡对接的设备中

2020-02-07 11:00:41

嗨,LVDS发送器IP(基于OpenLDI,像素和控制数据转换为LVDS信号)可用于Virtex6和Virtex7 FPGA吗?谢谢克里希纳

2020-06-17 14:52:28

。HAPS-51采用FPGA阵列Xilinx Virtex-5 LX330和板上存储器,加快了ASIC验证的速度。先前的HAPS系统在存储器存取方面采用子板,而最新的HAPS-51则采用位于板上并靠近

2018-11-20 15:49:49

加利福尼亚州,圣何塞— 2014年9月3日– S2C公司今日宣布TAI Player Pro 5.1版本正式发布。此次最新版本将帮助用户加速FPGA原型开发、提高工程师的生产力,以及实现最高的原型

2019-07-02 06:23:44

门,但 Xilinx Virtex-II 解决方案得到先进的逻辑和系统设计工具的支持,这些工具包括快速设计项、强大的综合功能、灵活的实现算法、以及高效的验证能力等各个方面,从而减少了开发时间

2013-09-06 16:28:27

由于路由问题(7000路径),XC7V2000T设备的SLR的一半设计可能会失败。而在XC7VX690T设备上尝试相同的设计时,仅需要32个故障路径。我们使用synplicity来合成设计。为两个

2018-10-31 15:29:24

和系统接口着手,那也是白白浪费时间。原型验证的一大优势就是尽早地从系统和集成的角度,以硬件原型着手进行软件与嵌入式的开发。而于此同时后端以及流片的ASIC研发时间可以同步进行。 但和RTL

2023-03-28 11:14:04

嗨,我使用virtex7 550t接收许多stm16链接。 GTH的参考时钟为155.520MHz,stm16接收正常。现在我想接收stm64,但在核心发生器中用于stm64参考时钟我只能选择

2020-08-24 10:10:44

嗨,我需要Virtex7 PCIE_3_0的DRP地址映射。我在用户指南pg25中找不到它我在哪里可以找到这些信息?

2020-04-22 10:07:02

你好 ,我在哪里可以找到几个在virtex7板上实现的示例设计文件,以便在板上获得良好的实际操作?提前致谢

2020-08-11 06:06:59

ASIC验证能够采用的主要技术是什么?如何利用现成FPGA开发板进行ASIC原型开发?

2021-05-08 07:51:04

嗨,我正在通过JTAG为Virtex-7开发系统内配置。我已经阅读了7系列FPGAs配置用户指南,但没有关于JTAG指令以及单/多设备配置顺序的详细信息。在哪里可以找到Virtex-7的单/多设备配置顺序信息?

2020-05-29 12:35:45

相比,能够为通信和多媒体应用提供高达10倍速的更高的设计和验证能力。Synphony HLS为ASIC 和 FPGA的应用、架构和快速原型生成最优化的RTL。Synphony HLS解决方案架构图

2019-08-13 08:21:49

的软件和基于FPGA 的原型系统可以相互通信,通常包括内存、 处理器和高速接口等。S2C 独有的申请专利的 Prodigy ProtoBridge? 系统正是允许这种类型的高速通信一个解决方案

2018-08-07 09:41:23

嗨,我已经为axe_cros***ar配置了12个从站和16个主站,用于Virtex7 2000T设备。ID宽度为4,即arid [3:0],awid [3:0],rid [3:0],bid [3

2019-03-14 17:07:40

你好,我正在开发一个在VC709开发板上使用Virtex7 FPGA的系统。该应用程序使用32Mb的板载Block RAM作为设计中的存储元件。 FPGA配置序列完成后,有没有一种方法可以使用PC上的JTAG / USB接口直接写入和读取Block RAM的内容?谢谢,

2019-09-29 14:00:01

亲关于如何使用GTX生成PIPE接口PCIE PHY的以下主题,有没有人有答案?https://forums.xilinx.com/t5/7-Series-FPGA

2020-05-04 09:05:44

模数转换器AD9625的评估板AD-FMCADC3-EBZ能不能和赛灵思的Virtex7系列FPGA开发板连接,我看到他们都具备JESD204B接口,物理接口上能直接连吗?还是说需要在使用转换接口来连接?

2018-07-31 07:45:33

失败的原因不是时序或者功率的问题,而是逻辑或功能错误。为此,功能验证已经成为ASIC开发周期中一个最关键的环节,通常最耗费时间。越来越多的ASIC设计人员发现通过采用FPGA进行功能原型设计能够最好

2019-07-15 07:00:39

。基于FPGA的原型验证方法凭借其速度快、易修改、真实性的特点,已经成为ASIC芯片设计中重要的验证方法[2].本文主要描述高频RFID芯片的FPGA原型验证平台的设计,并给出验证结果。

2019-06-18 07:43:00

。基于FPGA的原型验证方法凭借其速度快、易修改、真实性的特点,已经成为ASIC芯片设计中重要的验证方法。本文主要描述高频RFID芯片的FPGA原型验证平台的设计,并给出验证结果。1、RFID芯片的FPGA

2019-05-29 08:03:31

描述 Virtex®-7 FPGA 针对 28nm 系统性能与集成进行了优化,可为您的设计带来业界最佳的功耗性能比架构、DSP 性能以及 I/O 带宽。 该系列可用于 10G 至 100G

2023-09-01 10:41:54

随着SoC设计复杂度的提高,验证已成为集成电路设计过程中的瓶颈,而FPGA技术的快速发展以及良好的可编程特性使基于FPGA的原型验证越来越多地被用于SoC系统的设计过程。本文讨论

2010-11-11 16:00:07 35

35 FPGA原型验证和其他验证方法是不同的,任何一种其他验证方法都是ASIC验证中的一个环节,而FPGA验证却是一个过程。由于FPGA与ASIC在结构、性能上各不相同,ASIC是基于标准单元库,FPGA用的

2010-09-10 17:22:26 989

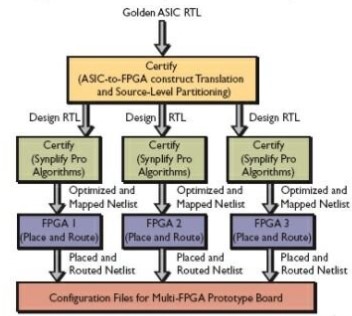

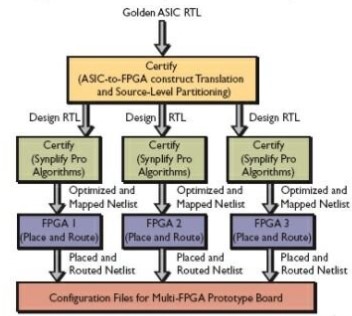

989 对ASIC设计进行FPGA原型验证时,由于物理结构不同,ASIC的代码必须进行一定的转换后才能作为FPGA的输入。 现代集成电路设计中,芯片的规模和复杂度正呈指数增加。尤其在ASIC设计流程中

2011-03-25 15:16:20 108

108 S2C公司发表最大容量SoC/ASIC原型系统,Quad S4 TAI Logic Module 能够容纳高达3,280万闸的设计并且拥有 S2C 第4代原型系统的所有优点

2011-04-26 09:40:00 952

952 S2C日前宣布其Verification Module技术(专利申请中)已可用于其基于 Xilinx 的FPGA原型验证系统中。V6 TAI Verification Module可以实现在FPGA原型验证环境和用户验证环境之间高速海量数据传输。用户

2011-09-20 09:07:58 1231

1231 赛灵思已向客户推出世界最大容量FPGA:Virtex-7 2000T。这款包含68亿个晶体管的FPGA具有1954560个逻辑单元,容量相当于市场同类最大28nm FPGA的两倍

2011-10-26 14:31:29 1491

1491 Virtex-7 2000T FPGA的容量是市场同类最大28nm器件的2倍,而且比赛灵思最大型Virtex-6 FPGA大2.5倍。虽然2000T由4个切片组成,但它仍然保持着传统FPGA的使用模式,设计人员可通过赛灵思工具流程

2011-10-26 09:11:30 2795

2795 全球可编程平台领导厂商赛灵思公司宣布其28nm Virtex®-7 2000T 荣膺2012年度中国电子成就奖之数字处理器/DSP/FPGA类最佳产品奖

2012-03-01 18:33:43 921

921 S2C今日宣布为其全面的Prototype Ready™配件家族新增ARM1176和ARM926 GUC测试芯片模块,用于搭建基于FPGA的原型并将基于FPGA的原型验证板接到用户的目标操作环境。

2012-06-06 10:25:08 1358

1358

2000T培训文件

2016-12-29 11:56:13 0

0 新增的8种模块使设计者更专注于产品差异化, 并加快产品上市时间 S2C 公司,业内领先的 FPGA 快速原型验证系统供应商, 今日发布8种新的 FPGA 原型验证接口子卡和配件,其旨在加快发展

2017-02-08 06:50:11 629

629

万个 ASIC 门。这款 FPGA 原型板提供 10 个扩展站点,具有多达 1,327 个用户 I/O,用来连接子板(例如存储器板、接口板)、连接电缆或用户专用的应用板。该产品可与 proFPGA

2017-02-08 12:12:11 343

343 数据流及数据包处理的系统原型设计的理想平台,可充分满足 400+ Gbps 系统、大规模仿真以及高性能计算等应用需求。 主要性能和优势 使用 Virtex UltraScale FPGA 优化实现快速原型

2017-02-08 14:19:11 478

478 如今,设计人员使用两种相对独立的方法进行 SoC 原型验证:以事务级模型为基础的虚拟原型验证和基于 FPGA 的原型验证。 虚拟原型验证执行快速的 TLM,并可提供更高效的调试和分析方案,非常适合

2017-02-08 14:32:11 293

293 。Cadence的Protium快速原型平台基于Xilinx Virtex-72000T 3D FPGA。(见Generation-jumping 2.5D Xilinx Virtex-7 2000T

2017-02-08 15:49:11 307

307

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 想开发一款能在多个地理位置处理任何设计规模的FPGA原型系统么?那么,最好拟定一个大规模的计划方案。S2C新发布的Prodigy

2017-02-09 03:49:04 437

437 Aldec 的 HES-7 (HES7XV12000BP) 在 FLG1925 封装中包含 6 个 Xilinx Virtex-7 2000T FPGA ,每款电路板可提供多达

2017-02-09 06:27:08 327

327 FPGA原型验证和其他验证方法是不同的,任何一种其他验证方法都是ASIC验证中的一个环节,而FPGA验证却是一个过程。

2017-02-11 12:46:11 2975

2975 此方案可简化,无电缆的设计分割,最多允许四个用户同时使用。S2C公司,业内领先的 FPGA 快速原型验证系统供应商,发布了适用于超大规模设计的基于赛灵思Virtex UltraScale(VU

2018-06-29 08:09:00 4932

4932 新思科技(Synopsys, Inc.,纳斯达克股票市场代码:SNPS)日前宣布:推出全新HAPS-80基于FPGA的原型系统,该系统为Synopsys的端到端原型解决方案的一部分。HAPS-80

2018-07-10 10:42:00 2067

2067 加利福尼亚州,圣何塞 - 2014年2月25日 - 业界领先的SoC/ASIC快速原型解决方案提供商S2C Inc.于今日宣布,在其基于FPGA的原型平台V7 TAI Logic Module系列

2018-02-11 14:27:00 3302

3302 赛灵思Virtex-7 2000T 演示

2018-06-05 01:45:00 2632

2632 由于新型AISC投片的成本和复杂性不断增加,越来越多的企业转向采用基于FPGA的原型设计和仿真功能,以及在投片推出前验证AISC RTL并降低相关风险。

2018-06-06 13:46:00 2852

2852

Xilinx公司全球最大容量芯片Virtex-7 2000T 性能演示。

2018-06-04 13:47:00 5120

5120 近年来,ASIC设计规模的增大带来了前所未有的芯片原型验证问题,单颗大容量的FPGA通常已不足以容下千万门级、甚至上亿门级的逻辑设计。现今,将整个验证设计分割到多个采用最新工艺大容量FPGA中,FPGA通过高速总线互联,成为大规模ASIC或SOC原型验证的极佳选择。

2018-07-02 08:20:00 1695

1695 在不太遥远的过去,对ASIC设计团队而言,在这类情况下主要的解决方案就是在内部建立他们自己的定制多个FPGA的原型开发板。然而,今天,使用现成的多个FPGA原型开发板——例如,由Synplicity

2019-05-16 08:07:00 2742

2742

采用fpga原型技术验证asic设计,首先需要把asic设计转化为fpga设计。但asic是基于标准单元库,fpga则是基于查找表,asic和fpga物理结构上的不同,决定了asic代码需要一定

2019-07-23 08:07:00 1923

1923

了解如何将复杂的SoC平台映射到单个Virtex®-7 2000T FPGA

2018-11-23 06:38:00 2515

2515 通过Virtex-7 2000T FPGA中的GTX收发器实现高速串行性能。

2018-11-22 06:27:00 3461

3461 ASIC芯片一旦流片功能就无法改变,基本专片专用。而FPGA可配置特性就可以应用在功能会改变的场合,例如,原型验证,ASIC设计过程中会使用到FPGA来进行原型验证;功能升级,在产品中采用FPGA实现一些业内暂时还没成熟的解决方案,可以在后续功能变动时方便升级。

2019-08-25 10:40:01 10934

10934

S2C公司,业内领先的FPGA快速原型验证系统供应商,宣布推出其全新的基于英特尔Stratix 10 GX 10M FPGA的S10 10M Prodigy逻辑系统,其配置包括单颗、双颗以及四颗FPGA。

2019-11-20 09:08:32 2159

2159 国微集团旗下子公司S2C公司,业内领先的FPGA快速原型验证系统供应商,宣布推出其全新的基于英特尔 Stratix 10 GX 10M FPGA 的 S10 10M Prodigy 逻辑系统,其配置包括单颗、双颗以及四颗FPGA。

2019-11-20 14:53:32 976

976 发布了基于该FPGA的ASIC和SoC原型设计与验证系统的详细信息。 proFPGA quad Intel® Stratix® 10 GX 10M FPGA 原型设计系统集成了四个基于英特尔Stratix 10

2019-12-06 15:09:14 2144

2144 丰富计算资源的同时还具备有非常丰富的外设接口:SFP+、QSFP、IPASS PCIe、FMC等;非常适用于ASIC原型验证、高性能计算系统原型开发等场景。

2020-05-19 10:50:05 2521

2521 国微思尔芯(“S2C”), 全球领先的前端电子设计自动化 (EDA) 供应商, 发布全球首款FPGA验证仿真云系统 Prodigy Cloud System。这是为下一代 SoC 设计验证需要而特别

2020-07-13 09:18:38 664

664 了 Xilinx 的 Virtex® UltraScale+™ FPGA,在性能和易用性上也进行了优化。此系列产品具有高比率的 DSP 和内存数量,对于验证高速连接和密集计算应用来说,是理想的原型验证平台。S7系列首先推出的前两款产品是 Prodigy™ S7-9P 和 Prodigy™ S7-13P。

2020-07-13 09:32:30 709

709 Virtex UltraScale+ VU19P是赛灵思密度最高的FPGA,是ASIC和SOC原型验证的最佳选择。

2020-10-22 14:23:13 1385

1385 ,加速超大规模设计验证,提升设计性能 完整的原型验证解决方案包括多FPGA深度调试,系统级协同建模及 90 多种应用接口子板库 2020年10月22日,国微思尔芯,一站式EDA验证解决方案专家,正式推出面向超大规模SoC原型市场的ProdigyTM S7-19P原型验证系统。 S7-19P提供单、

2020-10-23 15:02:18 2375

2375 “基于我们20余年的产业经验,我们快速选定了S2C的芯神瞳逻辑系统S7-19PQ。S2C毕竟是十多年的成熟品牌,有着稳定流畅的系统,再配合超强分割引擎,在研发初期快速、高效地支撑了我们5G 芯片系统的原型验证。为我们完整的5G芯片平台顺利推进奠定了坚实的基础。”

2022-07-22 16:00:12 1507

1507 FPGA(Field Programmable Gate Array)原型验证,基于其成本适中、速率接近真实系统环境等优点,受到了验证工程师的青睐。正是由于广泛丰富的应用场景,FPGA 原型系统

2022-09-19 13:40:03 533

533

在现代SoC芯片验证过程中,不可避免的都会使用FPGA原型验证,或许原型验证一词对你而言非常新鲜,但是FPGA上板验证应该是非常熟悉的场景了。

2023-03-28 09:33:16 854

854 FPGA原型验证在数字SoC系统项目当中已经非常普遍且非常重要,但对于一个SoC的项目而言,选择合适的FPGA原型验证系统显的格外重要

2023-04-03 09:46:45 928

928 FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能和性能。

2023-04-10 09:23:29 947

947 FPGA原型验证系统要尽可能多的复用SoC相关的模块,这样才是复刻SoC原型的意义所在。

2023-05-23 16:50:34 381

381

多片FPGA的原型验证系统的性能和容量通常受到FPGA间连接的限制。FPGA中有大量的资源,但IO引脚的数量受封装技术的限制,通常只有1000个左右的用户IO引脚。

2023-05-23 17:12:35 1149

1149

在现代SoC芯片验证过程中,不可避免的都会使用FPGA原型验证,或许原型验证一词对你而言非常新鲜,但是FPGA上板验证应该是非常熟悉的场景了。

2023-05-30 15:04:06 905

905

FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能和性能。

2024-01-12 16:13:01 220

220

电子发烧友App

电子发烧友App

评论