利用FPGA实现双口RAM的设计及应用

概述:为了在高速采集时不丢失数据,在数据采集系统和

2010-04-16 14:08:36 11323

11323

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作。

2021-01-22 09:43:11 4794

4794

在选择FPGA时,关注LUT(Look-Up Table)和BRAM(Block RAM)是非常重要的,因为它们是FPGA架构中的两个核心资源,对于设计的性能和资源利用至关重要。

2023-11-21 15:03:06 548

548

.互连线资源(Interconnect)4.嵌入式块 RAM(BRAM)(Block RAM)5.底层内嵌功能单元6.内嵌专用硬核7.致谢FPGA 芯片整体架构FPGA 芯片整体架构如下所示,大体按照...

2021-07-30 08:10:06

、FPGA一般触发器资源比较丰富,而CPLD组合逻辑资源更丰富。6、FPGA和CPLD的组成:FPGA基本有可编程I/O单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核

2020-10-21 10:32:50

FPGA由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等。

2019-05-24 06:15:05

利用FPGA设计双口ram,最大设计多的空间的?如果是cpld来实现,空间是不是更小?如何去确定这个大小呢?求指导

2013-10-21 21:23:21

,实际上每一个系列的FPGA都有其相应的内部结构),FPGA芯片主 要由6部分完成,分别为:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌

2017-05-09 15:10:02

功能(如RAM、时钟管理和DSP)的硬核(ASIC型)模块。如图1-1所示(注:图1-1只是一个示意图,实际上每一个系列的FPGA都有其相应的内部结构),FPGA芯片主要由6部分完成,分别为:可编程输入输出

2023-05-30 20:53:24

一.查找表(Look-Up-Table)的原理与结构采用这种结构的PLD芯片我们也可以称之为FPGA:如altera的ACEX,APEX系列,xilinx的Spartan,Virtex系列等。查找表

2012-04-28 14:57:28

一、FPGA的基本结构 FPGA由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式摸块RAM、丰富的布线资源、底层嵌入式功能单元和内嵌专用硬核等。 每个单元简介如下: 1.

2019-09-24 11:54:53

一、FPGA的基本结构 FPGA由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式摸块RAM、丰富的布线资源、底层嵌入式功能单元和内嵌专用硬核等。 每个单元简介如下: 1.

2016-07-16 15:32:39

一、FPGA的基本结构 FPGA由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式摸块RAM、丰富的布线资源、底层嵌入式功能单元和内嵌专用硬核等。 每个单元简介如下: 1.

2016-08-23 10:33:54

一、FPGA的基本结构 FPGA由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式摸块RAM、丰富的布线资源、底层嵌入式功能单元和内嵌专用硬核等。 每个单元简介如下: 1.

2016-09-18 11:15:11

一、FPGA的基本结构 FPGA由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式摸块RAM、丰富的布线资源、底层嵌入式功能单元和内嵌专用硬核等。 每个单元简介如下: 1.

2016-10-08 14:43:50

我有8个Spartan 6 FPGA设计原型和一个外部DDR RAM。我使用Multi-Port-Memory-Controller并选择bank 3进行外部DDR-RAM连接。我的Spartan

2019-06-20 15:21:24

的Spartan,Virtex系列等。查找表(Look-Up-Table)简称为LUT,LUT本质上就是一个RAM。 目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成一个有4位地址线的16x1

2008-05-20 09:46:10

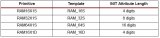

》, Volume I,Section I,3)。Cyclone III中的ram块是M9k,每一块中包含8192个存储位,加上校验位共9216位,故称M9k。每个ram块可配置为表3-1中的各种模式

2015-09-05 18:59:57

请问版主,OKMX6UL-C2工业级开发板的方案四,8位地址,16位数据接口有对接ram或者FPGA的例程或者测试程序么?谢谢。

2022-01-11 07:52:59

嗨,为了调试系统,我需要在系统运行时动态读取Block-RAM内容....我只有JTAG线,我不能在FPGA中制作一个特定的块用于读取内容并通过JTAG等发送它们。我可以使用ISMP 13.2作为

2019-06-11 07:36:08

STM32H743 有各种可用的 ram 块,如下所示:DTCMRAM - 128kBITCMRAM - 64kBRAM_D1 - 512kBRAM_D2 - 288kBRAM_D3 - 64kB1

2023-02-06 06:19:29

大家好,我想在Spartan 3E XC3S250E中使用100Kbits Memrory(6400字深16位宽),根据数据表,它有216Kbits的总RAM(12个RAM块)。数据表还说每个RAM

2019-02-27 09:16:11

本帖最后由 lpc2292 于 2013-2-27 20:24 编辑

“部分 I: 用 Spartan-3 系列 FPGA 进行设计”第 1 章 “概述”第 2 章 “使用全局时钟资源”第 3

2013-02-27 20:20:10

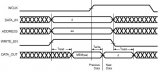

Vivado综合可以理解多种多样的RAM编写方式,将其映射到分布式RAM或块RAM中。两种实现方法在向RAM写入数据时都是采取同步方式,区别在于从RAM读取数据时,分布式RAM采用异步方式,块RAM

2020-09-29 09:40:40

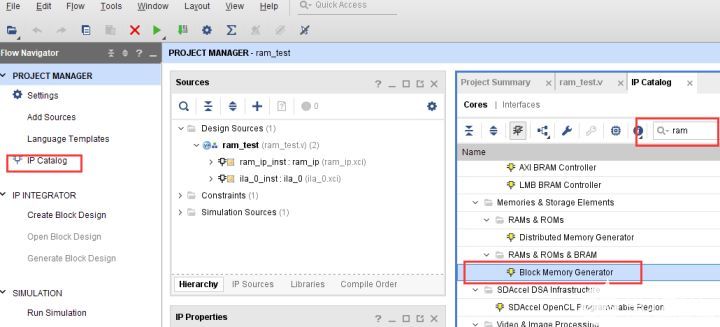

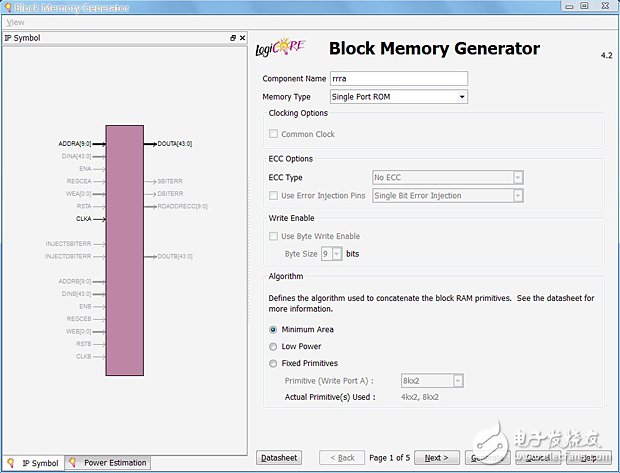

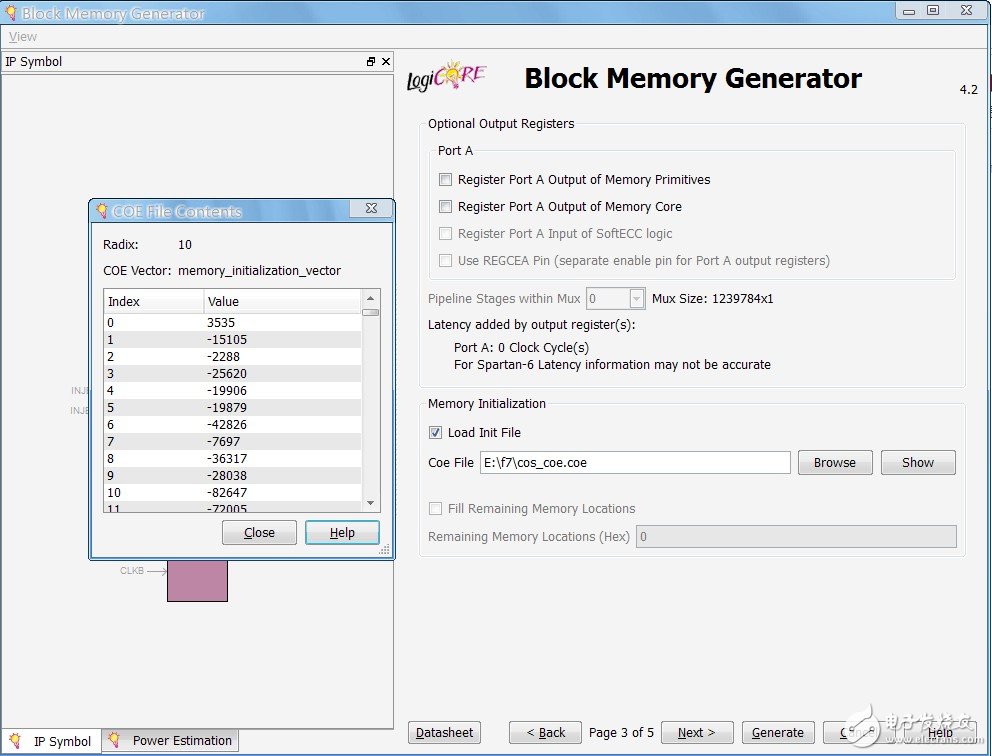

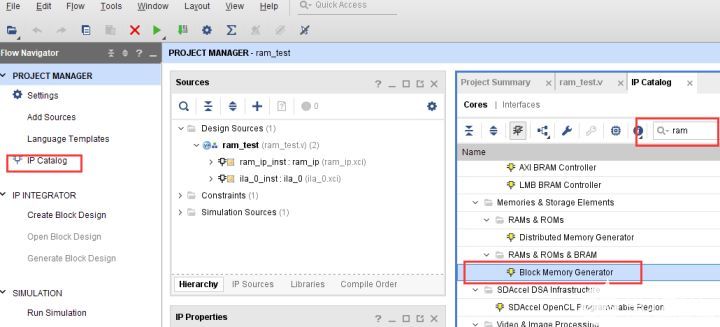

`Xilinx FPGA入门连载48:FPGA片内RAM实例之RAM配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1新建源文件打开

2016-01-22 13:39:24

`Xilinx FPGA入门连载49:FPGA片内RAM实例之功能仿真特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 Xilinx库

2016-01-25 12:55:23

Cortex-A9 处理器,但该器件上的 FPGA 数量存在差别,如表 1 所示:[td]Xilinx Zynq SoC可编程逻辑单元块 RAM 的容量大小 (Mb)DSP 切片

2018-08-31 14:43:05

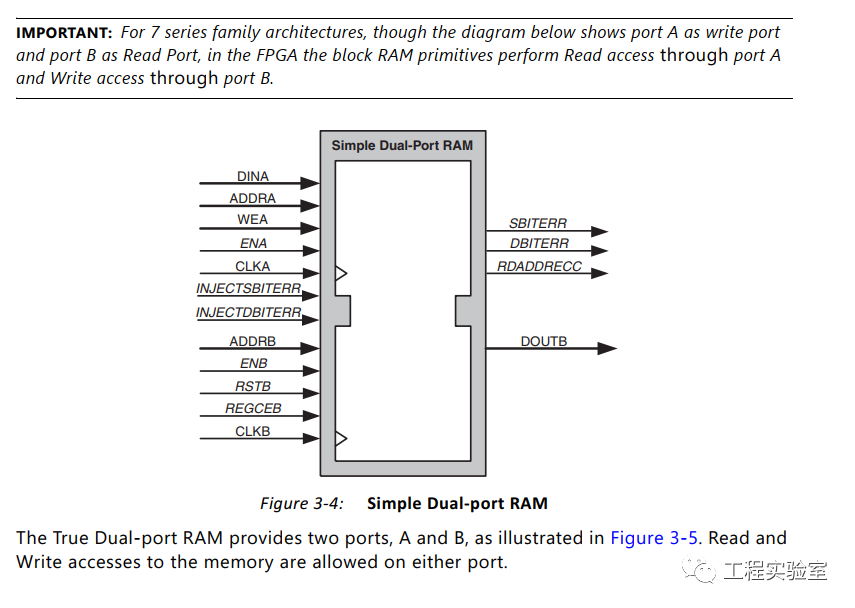

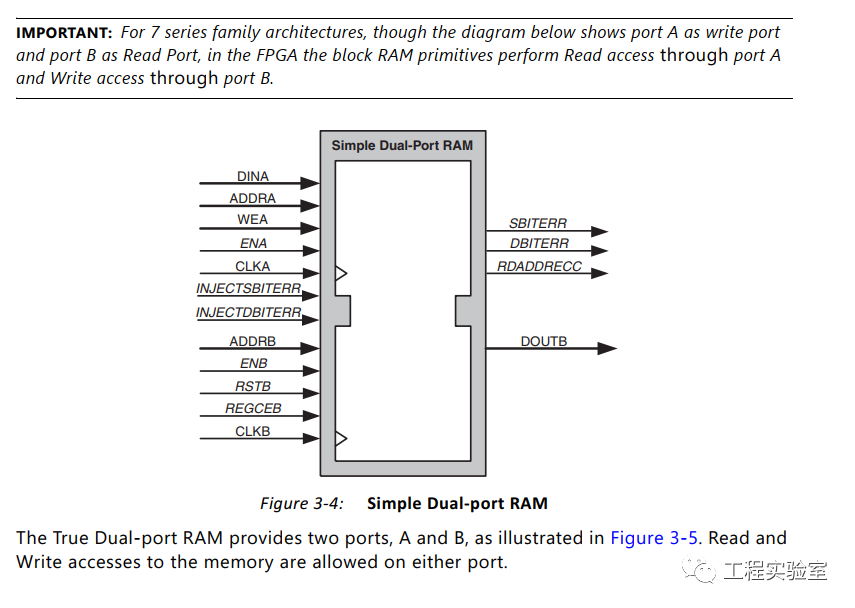

到每一个触发器的时钟、时钟使能和时钟缓存。 Artix-7系列块存储器Artix-7系列FPGA的嵌入式块RAM为双端口的36Kb块RAM,位宽高达72bit。每个M36K有两个完全独立的端口,因此可以

2016-11-01 15:52:18

,有对开发套件感兴趣的也可以加技术支持群472607506了解咨询。 今天是视频第十三讲,主要讲解FPGA芯片中提供的专用嵌入式块RAM的应用实例之一,也就是RAM IP核的使用。课程首先简单介绍了

2015-10-23 12:47:16

两块TMS320F***通过双端口RAM通讯,一块写入,另一块读出,应该怎么连接

2016-04-21 10:35:14

我正在运行Spartan 6 block ram的模拟。时钟速度为100Mhz。块ram的写作运作良好。我可以在内存中看到数据。但是当我读取数据时,输出有2个时钟的延迟。在块ram用户guidt中

2019-07-25 08:15:27

为什么要在显示器应用中使用FPGA?一种Spartan-3E显示器解决方案板

2021-06-04 06:47:39

这里要谈的是Xilinx的spartan-3系列FPGA的配置电路。当然了,其它系列的FPGA配置电路都是大同小异的,读者可以类推,重点参考官方提供的datasheet,毕竟那才是最权威的资料。

2019-10-10 06:16:52

什么是双口RAM?基于FPGA的双口RAM有哪些应用?

2021-05-06 07:41:03

设计来增设全新的芯片功能,据此实现了芯片整体构造的简化与性能提升。下面英尚微电子介绍FPGA开发板内部ram是如何操作的。 除逻辑外,所有新的FPGA都有专用的静态ram块,这些块在逻辑元素之间分布并由

2020-09-10 11:11:57

`例说FPGA连载38:DDR控制器集成与读写测试之FPGA片内RAM概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc 我们所

2016-10-12 17:18:25

给大家分享一下关于Spartan6板子的使用心得。

2021-04-30 07:03:13

求大神分享一些关于spartan6套件试用心得

2021-04-15 06:42:05

嗨这是来自海得拉巴的kishore。我们正在设计一个系统,我们使用的是XC6VSX475T ff1156 -1 FPGA。我们在这个FPGA中使用的是microblaze软核处理器。我们的要求是将

2019-02-18 09:01:37

ram或block ram进行设计的任何众所周知的标准3.任何人都可以比较所需的参数,例如127x8内存的速度,功率和效率,以及内存大小是否增加到512x8。请紧急回答

2020-03-23 07:17:45

的FPGA 都有其相应的内部结构),FPGA 芯片主要由6 部分完成,分别为:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌专用硬件模块

2018-08-23 09:14:59

FPGA入门嵌入式块RAM使用为FIOF(First In First Out)单时钟FIOF、双时钟FIOF(普通双时钟和混合宽度双时钟)由于单时钟FIOF只有一个时钟信号,所以可以在FPGA内部中使用单时钟FIOF用以其他模块数据的缓存。...

2021-12-17 07:59:18

我们正在尝试在Spartan 3器件中创建9个270个位置(每个8位)的RAM块。这在合成期间失败了。任何人都可以建议正确的方法吗?以上来自于谷歌翻译以下为原文We are trying

2019-05-15 14:06:41

E 系列中以18Kbits 为一块,在规模最小的型号XC3S100E 上集成了4 块这样的内存,如图2 所示:图2 Spartan-3E 系列FPGA 集成的Block RAM

2012-05-14 12:37:37

嗨,嗨,我想让ise实现我的ram作为双端口ram,它将有两个读端口(不需要或不使用写端口)。我在这个过程中使用以下几行process_read:process(clk,address1

2019-07-23 10:39:41

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作。1.实验原理Xilinx

2021-01-07 16:05:28

嗨,我正在使用Xilinx模板创建一个通用的True Dual端口ram。目标是在每个设计中使用此RTL,以便在切换FPGA系列时简化器件对器件的可靠性。从V5到K7。我修改了tempelate以

2020-07-23 10:14:09

你好xilinx用户,我正在使用FPGA实现人工神经网络。我想知道如何在FPGA中使用0.784,1.768..etc等数字。表示这些数字的方法是什么。以上来自于谷歌翻译以下为原文hello

2019-03-04 13:38:31

09 C4 30 70 00 64 16 0D 0A我希望在FPGA打开后将此十六进制字符串存储在块RAM中,以便FPGA可以在需要时检索此字符串有没有办法用for循环来实现这个?问候费萨尔以上

2019-06-14 07:54:16

套件的块rams中,另一个块ram用于存储另一个与R G B阵列相同的可变温度。Xilinx已经提到XC5LX110T具有5328Kb的内部RAM存储器,因此我必须使用多大的图像来确保使用内部DDR

2019-01-30 08:36:28

我为哈希程序编写了一个代码,它在合成时显示内部错误。但模拟效果很好。有人请告诉我正确的解决方案。如果我在always块中使用多个for循环(2维),这是一个问题吗?提前致谢......

2019-10-24 08:31:04

我有一个 ESP32-S3-WROOM1 模块,其中包含一个内部 SPI 2Mo RAM。我在 Eclipse 下开始了一个新项目,但我不知道如何在我的项目中声明 2Mo RAM。此外,我不知道

2023-03-01 06:37:03

大家好, 我使用Ultrascale Virtex Devices和Vivado工具, 在ASIC RAM中,ther是一个单独的奇偶校验写使能位,但在FPGA RAM中没有单独的Pariaty写使能位。 如何实现ASIC RAM奇偶校验写入启用ino FPGA RAM。谢谢娜文G K.

2020-04-24 09:37:05

我如何知道 S32K144 中使用了多少 RAM?RAM = Data + Bss,如何知道软件运行时S32K144使用了多少RAM?S32K144 现在在不固定的点重新启动。

2023-03-23 07:04:20

亲爱的大家我现在正在使用virtex5,我使用核心生成器IP制作块ram所以我将这些文件添加到项目(.vhd)以模拟代码IP的声明也已完成(将其添加为组件)但是在读取操作期间,我确定了块ram的地址

2020-06-11 09:47:52

学习fpga心得体会

2012-09-14 09:02:40

嵌入式块ram使用为rom(只读存储器)使用PC端的signaltap ii软件与FPGA内部搭建的片上逻辑分析仪连接,时刻查看FPGA内部的信号。使用Quartus II软件中提

2021-12-17 08:00:26

大家好,我曾使用Xilinx CoreGen生成块RAM,然后在我的设计中使用了它的实例化。该RAM适用于读写操作 - 在RTL sim中得到验证。我现在想要的是在访问此内存时相应地转储此特定RAM

2019-03-29 12:19:26

字节的 RAM 组成。FPGA 中存在的块 ram 的数量取决于 FPGA 的先进程度。例如,Spartan 6 FPGA 拥有比 Spartan 3更大的块 RAM。块 RAM 应该用于大型的实现。这两种

2022-04-03 11:20:18

新手入门FPGA领域心得

2015-11-30 20:59:18

的问题是:所有3种类型都可以在FPGA Spartan 6中使用,如果它们中的任何一种都有利于以更简单的方式实现。谢谢您的帮助。

2019-08-05 07:38:33

小弟最近在设计一款双核采集系统使用ep1c6q240c8和tms320vc5509a双核,两块芯片使用外部双口RAM进行数据传输,请教各位大神ep1c6q240c8怎么和双口RAM连接啊???????????????????????

2012-11-05 10:42:41

msp430的特点是什么?求大神分享关于msp430系列单片机的一些入门心得

2021-09-30 07:08:00

hithanx for ur support.I还有一个查询。如何从块ram(VirtexIIxc2v6000)读取值。是否必须在未初始化的寄存器中读取值?这意味着每次我必须创建一个新变量读取

2020-05-29 16:40:15

XC6SLX45T-3FGG484C FPGA - 现场可编程门阵列系列提供了成本、功率和性能的最佳平衡,提供了一种新的、更高效的双寄存器6输入查找表(LUT)逻辑和丰富的内置系统级块选择。其中

2022-08-04 11:47:34

为了在高速采集时不丢失数据,在数据采集系统和CPU之间设置一个数据暂存区。介绍双口RAM的存储原理及其在数字系统中的应用。采用FPGA技术构造双口RAM,实现高速信号采集系

2010-02-11 11:20:27 69

69 基于Actel FPGA 的双端口RAM 设计双端口RAM 芯片主要应用于高速率、高可靠性、对实时性要求高的场合,如实现DSP与PCI 总线芯片之间的数据交换接口电路等。但普通双端口RAM 最大

2010-11-15 17:44:19 82

82 在现代逻辑设计中,FPGA占有重要的地位,不仅因为具有强大的逻辑功能和高速的处理速度,同时因为其内部嵌有大量的可配置的块RAM,使其得到了广泛地应用,例如FFT算法的实现等。

2011-09-27 17:07:12 54

54 然后调用sinplify,对其进行综合,结果很不顺利。首先是synplify报不支持器件,才发现synplify 9.6.2是2008年的产品,比Spartan6器件还要老。更新到Synplify Pro D-2010.03之后,器件是支持了,但是一综合就报错停止了,却不提示有什么错误。

2017-02-11 12:49:40 2571

2571 带有异步写/同步读的SRAM,其中的同步读取可以使用与分布式RAM相关联的触发器实现。

2017-02-11 13:54:59 2160

2160

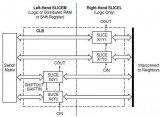

在赛灵思Spartan-3、3E等系列的FPGA中,其逻辑单元CLB中一般含有不同数量的单端口RAM(SRAM)或者双端口RAM(DRAM),这里的“单”或者“双”是由我们开发人员定义的。

2017-02-11 13:56:11 6348

6348

前面简要介绍了Spartan-3系列FPGA中分布式RAM的基本特性。为什么不从更高级的Virtex系列入手呢?我仔细看了一下各个系列的介绍、对比,Spartan系列基本就是Virtex系列的精简版,其基本原理是一样的,所以从简单的入手来融会贯通未尝不是一个好办法。

2017-02-11 13:57:40 1176

1176

前面讲了分布式RAM的方方面面,下面以RAM_16S为例,分别给出其在VHDL和Verilog HDL下面的模板代码(在ISE Project Navigator中选择 Edit---

2017-02-11 13:59:33 1323

1323 FPGA内部的RAM M9K

2017-04-07 11:40:04 4

4 FPGA中RAM的使用探索。以4bitX4为例,数据位宽为4,深度为4。

2018-03-28 17:07:28 9726

9726

大家好,又到了每日学习的时间了,今天我们来聊一聊在FPGA设计中RAM的两种使用方法,RAM是用来在程序运行中存放随机变量的数据空间,使用时可以利用QuartusII的LPM功能实现RAM的定制

2018-06-08 11:30:28 19562

19562 本指南是描述所有Spartan-6 FPGA中可用的Spartan®6 FPGA块RAM的技术参考。块RAM用于高效的数据存储或缓冲,用于高性能状态机或FIFO缓冲,用于大移位寄存器、大查找表或ROM。

2019-02-15 16:38:59 13

13 RAM。 今天咱们就聊一聊7系列FPGA里面的Block RAM。 在7系列FPGA里面,每个Block RAM最

2020-11-23 14:08:43 7379

7379

本文档的主要内容详细介绍的是FPGA的RAM存储资源详细资料说明包括了:1、 FPGA存储资源简介,2、 不同厂家的 Block RAM 布局,3、 块 RAM 和分布式 RAM 资源,4、 Xilinx Block RAM 架构及应用

2020-12-09 15:31:00 10

10 本文档的主要内容详细介绍的是FPGA硬件基础之FPGA的RAM存储课件和工程文件。

2020-12-10 15:27:00 30

30 在FPGA中block ram是很常见的硬核资源,合理的利用这些硬件资源一定程度上可以优化整个设计,节约资源利用率,充分开发FPGA芯片中的潜在价值,本文结合安路科技FPGA做简单总结,说明基本原理。

2020-12-24 14:28:09 916

916 FPGA可以调用分布式RAM和块RAM两种RAM,当我们编写verilog代码的时候如果合理的编写就可以使我们想要的RAM被综合成BRAM(Block RAM)或者DRAM(Distributed

2020-12-30 16:27:52 9

9 RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作。

2022-02-08 15:50:49 12183

12183

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作。

2021-03-15 06:09:45 14

14 电子发烧友网站提供《Logos系列FPGA专用RAM模块(DRM)用户指南.pdf》资料免费下载

2022-09-26 09:31:40 9

9 在FPGA 逻辑设计中经常用到的数据存储方式有ROM、RAM和FIFO,根据不同的应用场景选择不同的存储方式。Xilinx 平台三种存储方式在使用过程中的区别如下。

2023-08-22 16:12:47 1380

1380

FPGA在一个时钟周期可以读取多个RAM数据吗?如何理解FPGA中存放程序的RAM? FPGA在一个时钟周期可以读取多个RAM数据 FPGA中的RAM是FPGA中存储数据的主要形式之一,许多FPGA

2023-10-18 15:28:20 598

598 FPGA双口RAM的使用主要涉及配置和使用双端口RAM模块。双端口RAM的特点是有两组独立的端口,可以对同一存储块进行读写操作,从而实现并行访问。

2024-03-15 13:58:14 81

81

电子发烧友App

电子发烧友App

评论