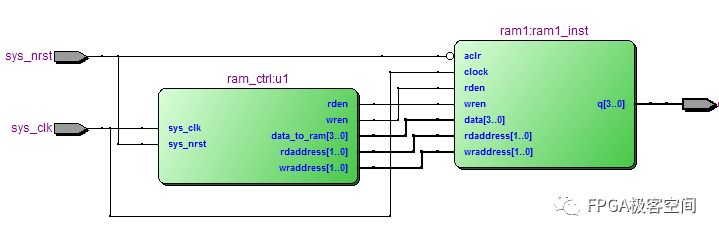

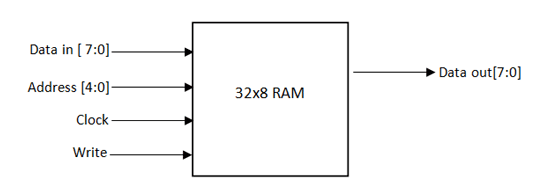

FPGA中RAM的使用探索。以4bitX4为例,数据位宽为4,深度为4。

第一种方式,直接调用4bitX4的RAM。编写控制逻辑对齐进行读写。

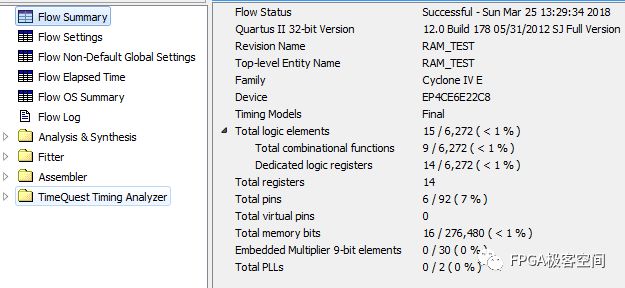

quartus ii 下的编译,资源消耗情况。

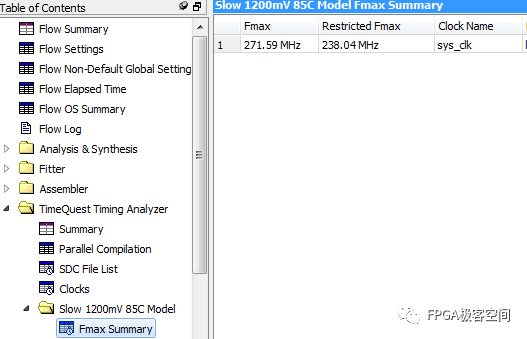

85C模型下的时钟频率。

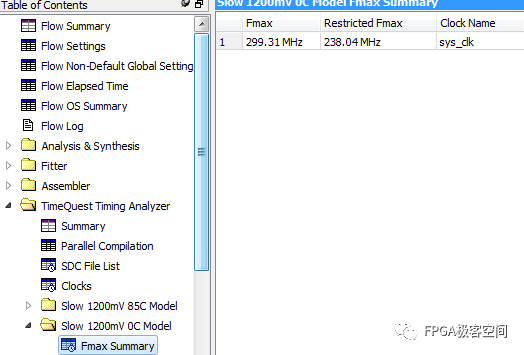

0C模型下的时钟频率。

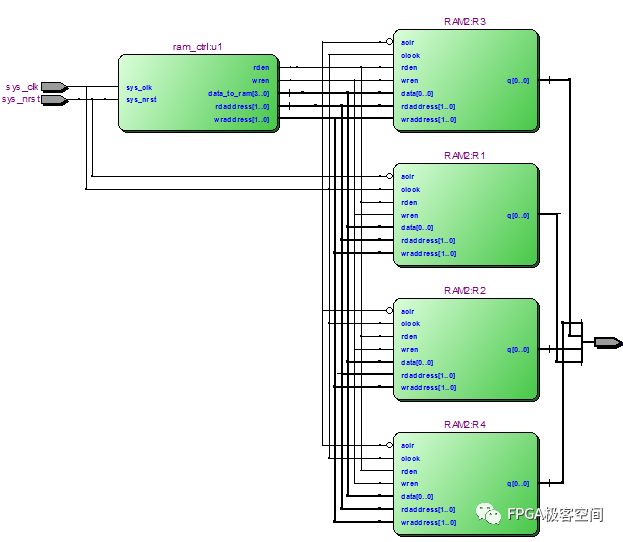

第二种方式,调用1bitX4的RAM,例化4次。编写控制逻辑对齐进行读写。

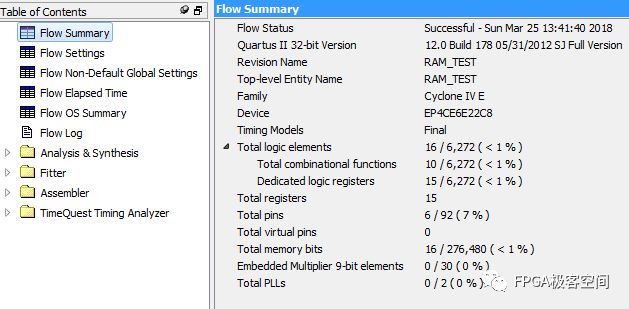

quartus ii 下的编译,资源消耗情况。

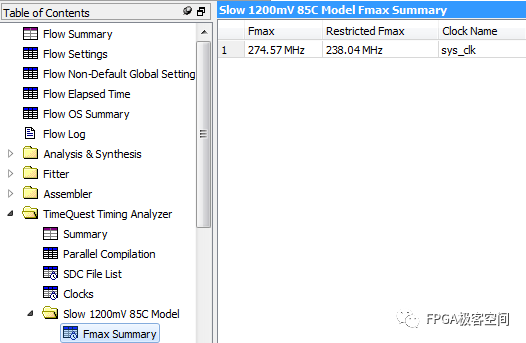

85C模型下的时钟频率。

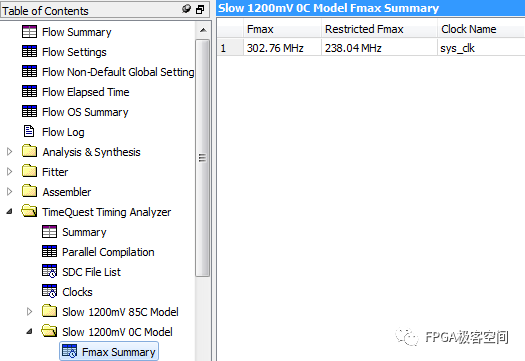

0C模型下的时钟频率。

从上述两种情况来看,两种RAM的使用方式,最终使用资源比较接近,方案二稍多,而从时序模型综合结果看,方案二的时钟频率明显比方案一高。在高速情况下,建议使用方案二。同样在位宽较宽情况下,可使用生成块语句进行例化,减少顶层对同一模块的例化数,是比较方便的。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22503浏览量

639272 -

RAM

+关注

关注

8文章

1401浏览量

121006

原文标题:FPGA中RAM使用探索

文章出处:【微信号:ALIFPGA,微信公众号:FPGA极客空间】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

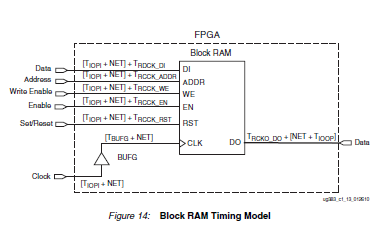

FPGA中块RAM的分布和特性

在选择FPGA时,关注LUT(Look-Up Table)和BRAM(Block RAM)是非常重要的,因为它们是FPGA架构中的两个核心资源,对于设计的性能和资源利用至关重要。

在FPGA中的RAM有与其他产品有什么不同?

实现了不同的逻辑功能。查找表(Look-Up-Table) 简称为LUT,LUT 本质上就是一个RAM。目前FPGA 中多使用4 输入的LUT,所以每一个LUT 可以看成一个有4 位地址线的 的

发表于 08-23 09:14

如何实现ASIC RAM替换为FPGA RAM?

大家好, 我使用Ultrascale Virtex Devices和Vivado工具, 在ASIC RAM中,ther是一个单独的奇偶校验写使能位,但在FPGA RAM

发表于 04-24 09:37

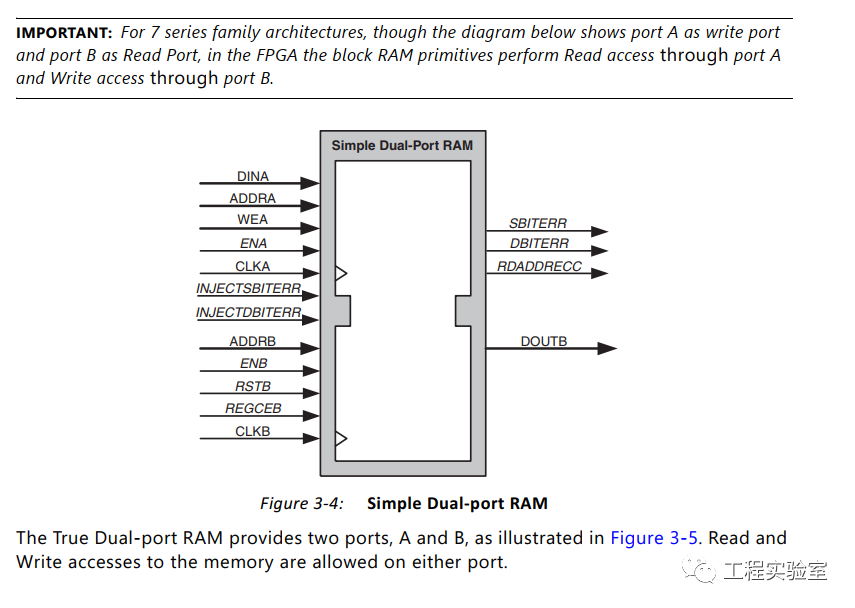

基于FPGA的双口RAM实现及应用

为了在高速采集时不丢失数据,在数据采集系统和CPU之间设置一个数据暂存区。介绍双口RAM的存储原理及其在数字系统中的应用。采用FPGA技术构造双口

发表于 02-11 11:20

•69次下载

FPGA内嵌的块RAM在FFT算法中的应用

在现代逻辑设计中,FPGA占有重要的地位,不仅因为具有强大的逻辑功能和高速的处理速度,同时因为其内部嵌有大量的可配置的块RAM,使其得到了广泛地应用,例如FFT算法的实现等。

发表于 09-27 17:07

•54次下载

如何用FPGA的Block RAM性能实现HDTV视频增强算法中灰度直方图统计

本文介绍了如何在FPGA 中利用Block RAM 的特殊结构实现HDTV视频增强算法中灰度直方图统计。

Spartan-6 FPGA块RAM的技术参考资料免费下载

本指南是描述所有Spartan-6 FPGA中可用的Spartan®6 FPGA块RAM的技术参考。块R

发表于 02-15 16:38

•14次下载

FPGA中block ram的特殊用法列举

在FPGA中block ram是很常见的硬核资源,合理的利用这些硬件资源一定程度上可以优化整个设计,节约资源利用率,充分开发FPGA芯片中的潜在价值,本文结合安路科技

如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该

fpga双口ram的使用

FPGA双口RAM的使用主要涉及配置和使用双端口RAM模块。双端口RAM的特点是有两组独立的端口,可以对同一存储块进行读写操作,从而实现并行访问。

技术控:FPGA中RAM使用技巧探索

技术控:FPGA中RAM使用技巧探索

评论