【Linux + C语言】话说,你真的了解system接口的调用吗?

2022-09-12 16:33:38 5356

5356

谈谈SiC MOSFET的短路能力

2023-08-25 08:16:13 3282

3282

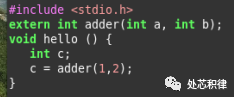

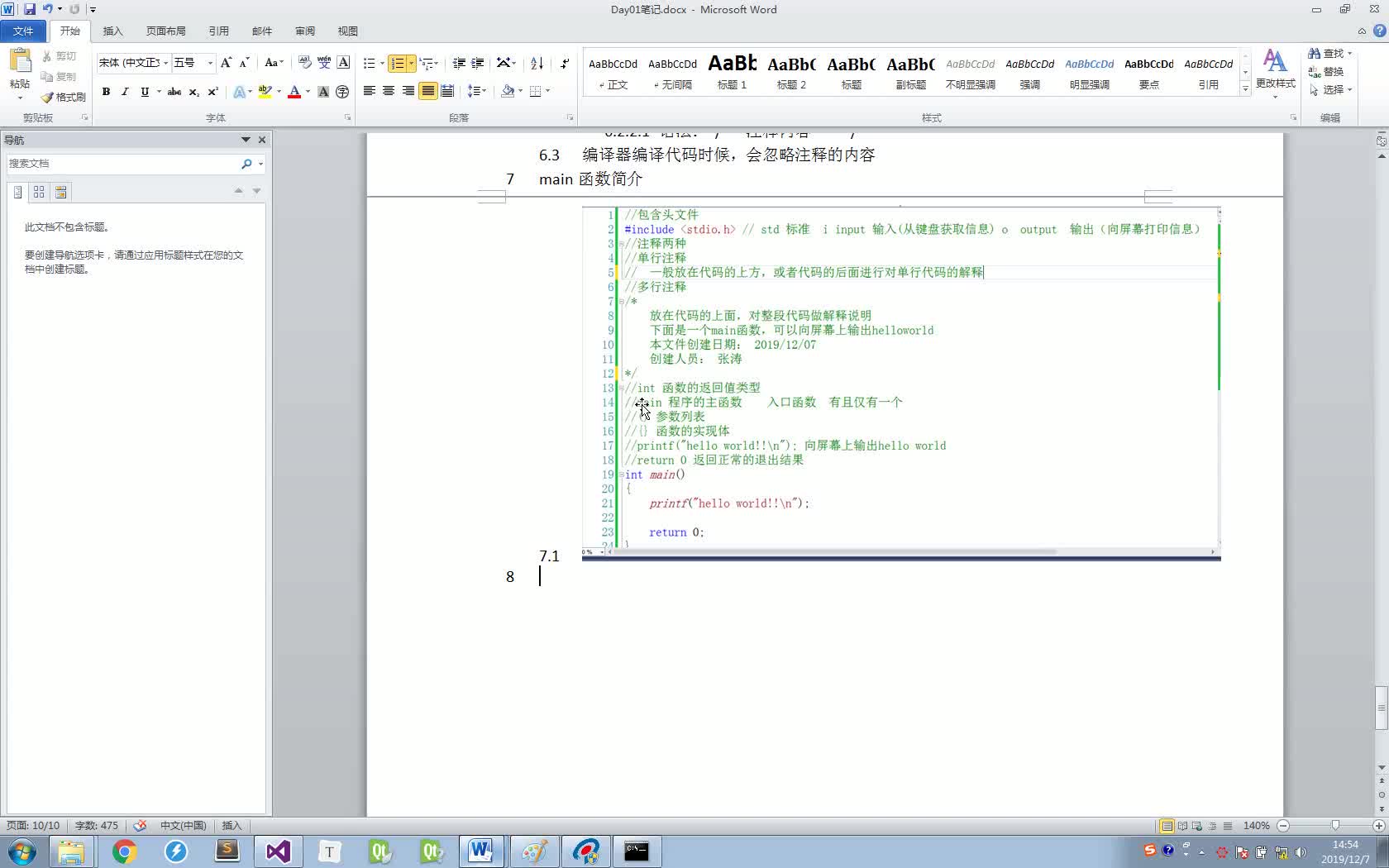

对代码执行时间要求很严格的算法,例如很多个点的FFT、IFFT中,汇编代码的高效仍然是C/C++所不能替代的。这些就涉及到了C/C++代码与汇编代码的接口问题,在此我们就来了解一下它们是如何交互的。首先要遵循以下的九大原则:

2021-02-01 07:12:42

SYSTEM C 是什么?它是怎样被提出来的?SYSTEM C有哪些显著的特点?SYSTEM C设计与传统设计比较,有哪些优点?

2021-04-14 07:10:12

本文讨论了一些System Verilog问题以及相关的SystemVerilog 语言参考手册规范。正确理解这些规格将有助于System Verilog用户避免意外的模拟结果。

2020-12-11 07:19:58

本文讨论了一些System Verilog问题以及相关的SystemVerilog 语言参考手册规范。正确理解这些规格将有助于System Verilog用户避免意外的模拟结果。

2020-12-24 07:07:04

Verilog HDL是一种用于数字逻辑电路设计的语言。用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型。Verilog HDL既是一种行为描述的语言也是一种结构描述

2019-09-06 09:14:16

谈谈C语言中指针有什么好处,请各位高手们谈谈自己的体会...

2012-09-01 17:38:47

谈谈TD-LTE及其测量技术

2021-05-26 06:55:49

谈谈ZigBee SoC的定位功能

2021-05-25 06:23:42

information:-1.Does itsupport System verilog forverification?2. Code coverage support.3.Assertion support.Whichversionof Modelsim XE supports these feature.

2018-11-27 14:20:41

你能否告诉我,自2014年4月以来Vivado 2016.3中对任何System Verilog功能的支持是否有所改变?你能告诉我这段代码是否适用于2014.4?interface ibb_if

2020-05-14 08:57:57

翻译成verilog,在FPGA里面实现,即system generator。altera有没有类似的接口,与matlab可以互连,直接在matlab里设计我所需要的算法,在翻译成verilog?

2015-01-14 14:20:50

。Verilog HDL 从 C 语言中继承了多种操作符和结构。Verilog HDL 提供了扩展的建模能力和扩展模块。Verilog HDL 语言的核心子集非常易于学习和使用,这对大多数建模应用来说已经足够

2018-09-18 09:33:31

CO_SIMULATION获取所有信号。我在SYSTEM C中用verilog HDL和Firmaware编写了RTL。但我没有得到任何适用于HW / FW协同仿真的文件。请帮我解决这个问题。谢谢

2020-04-17 10:09:54

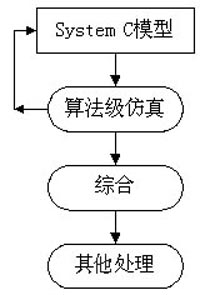

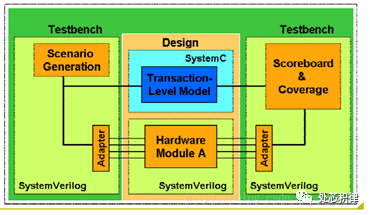

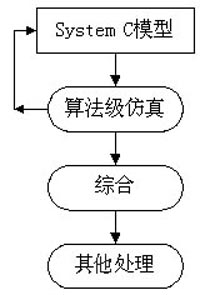

这种设计方法与现在常用的设计方法相比有很多优点: 1.精炼的设计方法。使用System C设计系统,系统设计人员不必花费很大的精力将整个系统设计由C语言描述转换为HDL描述。系统设计人员可以通过在C

2019-07-10 08:14:51

大家好,我试图在verilog文件中将命令传递给系统。 (在最初的开始循环中)我尝试使用$ system命令行。它现在处于verilog标准,但它似乎不适用于vivado。谁知道怎么做?这是我想要

2020-05-22 15:23:42

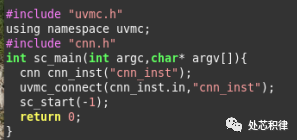

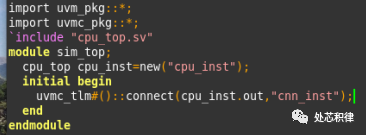

新手学习SystemVerilog & UVM指南 从刚接触System Verilog以及后来的VMM,OVM,UVM已经有很多年了,随着电子工业的逐步发展,国内对验证人才的需求也会急剧

2015-03-11 16:24:35

求大佬分享一些System Verilog的学习经验

2021-06-21 06:29:54

IEEE Standard Verilog Hardware Description Language

(This introduction is not part of IEEE Std

2008-10-21 15:37:44 0

0 The Verilog language is a hardware description language that provides a means ofspecifying a

2009-02-12 09:33:26 82

82 In-System FLASH Programming with hardwareimplemented bank switching capabilityThe following

2009-04-01 21:42:19 16

16 pcit32 verilog lattice源代码:The evolution of digital systems over the past two decades has placed new

2009-06-14 08:46:27 29

29 The Mindshare Architecture book series ISA System Architecture,EISA Syseten Architecture,80486

2009-07-17 16:55:47 41

41 The Mindshare Architecture book series includes:ISA System Architecture,EISA System Architecture

2009-07-17 17:36:58 0

0 The Verilog Programming Language Interface, commonly called the Verilog PLI,is one of the more

2009-07-22 09:55:36 0

0 The Verilog Programming Language Interface, commonly called the Verilog PLI,is one of the more

2009-07-22 09:57:33 0

0 This book is on the IEEE Standard Hardware Description Languagebased on the Verilog® Hardware

2009-07-23 08:59:50 0

0 提出了采用Verilog HDL 设计I2C 总线分析器的方法,该I2C 总线分析器支持三种不同的工作模式:被动、主机和从机模式,并提供了嵌入式系统设计接口。通过硬件总体框架分析,分

2009-08-10 15:32:18 40

40 简述了I2C总线的特点;介绍了开发FPGA时I2C总线模块的设计思想;给出并解释了用Verilog HDL实现部分I2C总线功能的程序,以及I2C总线主从模式下的仿真时序图。

2009-10-19 10:49:16 104

104 谈谈电路中的“地” 无论是在模拟电路中还是在数字电路

2006-04-16 23:34:00 3114

3114 摘要: 简述了I2C总线的特点;介绍了开发FPGA时I2C总线模块的设计思想;给出并解释了用Verilog HDL实现部分I2C总线功能的程序,以及I2C总线主从模式下的仿真时序图

2009-06-20 13:17:08 7138

7138

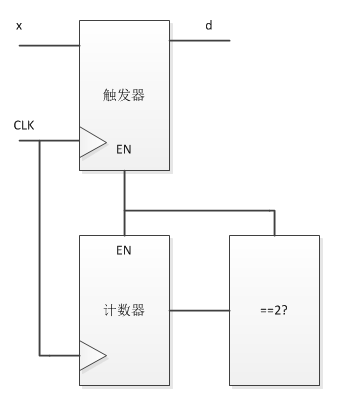

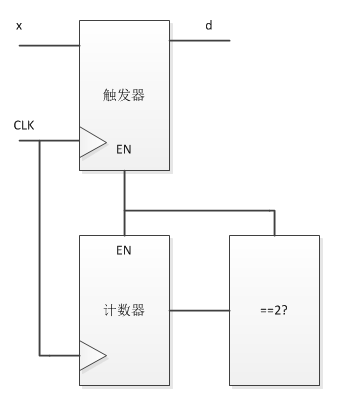

针对C语言编程者的Verilog开发指南实例

本文举例说明了如何用软件实现脉宽调制(PWM),如何将该设计转换成一个可以在FPGA中运行的逻辑块,并能利用

2009-12-27 13:26:43 1173

1173 什么是C-3/C3 system (Command、Control and Communication System)

英文缩写: C-3、C3 system (Command、Control and Communication System)

中文译名:

2010-02-22 10:54:48 1187

1187 一、概述 SYSTEM C 是由 Synospy Inc. 提出的,目前最新的版本为V2.0。它提出的目的就是以一种系统设计的思想进行系统设计。它将软件算法与硬件实现很好的结合在一起,提

2010-07-19 09:31:47 3259

3259

Verilog HDL与VHDL及FPGA的比较分析. Verilog HDL优点:类似C语言,上手容易,灵活。大小写敏感。在写激励和建模方面有优势。

2011-01-11 10:45:29 1580

1580 以前在贴Verilog代码时,都只能挑C++或者C#的语法着色,但两者的主题词毕竟不太一样,透过dudu的帮助,我将Verilog 2001年的主题词加上了,现在博客园也能漂亮的显示Verilog代码了!

2011-05-10 08:25:22 1244

1244 本文简单讨论并总结了VHDL、Verilog,System verilog 这三中语言的各自特点和区别 As the number of enhancements

2012-01-17 11:32:02 0

0 本资料是关于夏宇闻老师优秀的verilog教程课件,其中包括verilog讲稿PPT、verilog课件、verilog例题等。

2012-09-27 15:00:49 473

473 verilog verilog verilog verilog verilog verilog verilog verilog

2015-11-12 14:43:51 0

0 基于EP1C3的FPGA程序之seg7_verilog

2016-01-20 15:22:50 11

11 基于EP1C3的进阶实验_reference_verilog

2016-01-21 11:29:32 14

14 基于EP1C3的进阶实验seg7_verilog

2016-10-27 18:20:05 2

2 基于EP1C3的进阶实验eference_verilog

2016-10-27 18:20:05 3

3 基于EP1C3的进阶实验_reference_verilog

2016-11-18 16:05:02 4

4 基于EP1C3的FPGA程序之seg7_verilog

2016-11-18 16:05:02 0

0 《Visual C# 2005开发技术》与用户交互

2017-02-07 15:17:36 0

0 前一阵一直在忙,所以没有来得及写博文。弄完杂七杂八的事情,又继续FPGA的研究。使用Verilog HDL语言和原理图输入来完成FPGA设计的方法都试验过了,更高级的还有基于System Generator和基于EDK/Microblaze的方法。

2017-02-11 03:10:11 8716

8716

基于System Verilog中的随机化激励

2017-10-31 09:25:00 9

9 现在的FPGA算法的实现有下面几种方法: 1. Verilog/VHDL 语言的开发 ; 2. system Generator; 3. ImpulsC 编译器实现从 C代码到 HDL 语言; 4.

2017-11-17 14:29:06 8946

8946 Xilinx System Generator 是专门为数字信号算法处理而推出的模型化设计平台,可以快速、简单地将DSP系统的抽象算法转换成可综合的、可靠的硬件系统,弥补了大部分对C语言以及Matlab工具很熟悉的DSP工程师对于硬件描述语言VHDL和Verilog HDL认识不足的缺陷。

2018-07-19 09:32:00 4453

4453

数据传递是比较麻烦的事情。两者之间数据的传递有这样几种情况:java和c之间基本数据类型的交互,java向c传递对象类型,c向java返回对象类型,c调用java类。

2017-11-27 10:22:58 1974

1974 Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。而C语言是一门通用计算机编程语言,应用广泛。

2017-12-08 16:43:30 12969

12969 采用System Verilog语言设计了一种具有层次化结构的可重用验证平台,该平台能够产生各种随机、定向、错误测试向量,并提供功能覆盖率计算。将验证平台在Synopsys公司的VCS仿真工具上运行

2018-01-12 11:28:24 3225

3225

本文首先介绍了verilog的概念和发展历史,其次介绍了verilog的特征与Verilog的逻辑门级描述,最后介绍了Verilog晶体管级描述与verilog的用途。

2018-05-14 14:22:44 47074

47074

本文档的主要内容详细介绍的是Verilog HDL入门教程之Verilog HDL数字系统设计教程。

2018-09-20 15:51:26 86

86 本文档的主要内容详细介绍的是Verilog HDL教程之Verilog HDL的命令格式资料说明。

2019-01-09 08:00:00 32

32 Verilog HDL是一种用于数字系统设计的语言。用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型也称为模块。Verilog HDL既是一种行为描述的语言也是一种结构描述的语言。

2019-03-08 14:29:12 13726

13726 system的原理其实就是调用fork创建子进程去执行shell命令,然后返回最后一条shell命令的状态值。linux下man system可以看到返回值说明: 1.如果返回值等于

2019-04-02 14:41:05 1450

1450 Verilog与C语言还是存在许多差别。另外,作为一种与普通计算机编程语言不同的硬件描述语言,它还具有一些独特的语言要素,例如向量形式的线网和寄存器、过程中的非阻塞赋值等。总的来说,具备C语言的设计人员将能够很快掌握Verilog硬件描述语言。

2019-12-11 07:02:00 2375

2375

本文档的主要内容详细介绍的是Verilog教程之Verilog HDL程序设计语句和描述方式。

2020-12-09 11:24:23 53

53 和EDA工具之间交互的C语言例程。(模拟器、波形显示器)

SDF:标准延迟格式-一个文件,用于向模拟器和其他工具反注释精确的定时信息。

2021-02-02 16:19:23 9

9 发展历史 1984年,Verilog开始作为一种专用的硬件建模语言使用,取得了相当大的成功。1990年,Cadence Design Systems公司将该语言面向公众开放,作为试图与VHDL相抗衡

2021-06-21 14:46:08 12174

12174 SystemVerilog语言简介 SystemVerilog是一种硬件描述和验证语言(HDVL),它基于IEEE1364-2001 Verilog硬件描述语言(HDL),并对其进行了扩展,包括扩充

2021-09-28 17:12:33 4472

4472 SystemVerilog是一种 硬件描述和验证语言 (HDVL),它 基于IEEE1364-2001 Verilog硬件描述语言(HDL),并对其进行了扩展,包括扩充了C语言数据类型、结构、压缩

2021-10-19 10:58:05 5218

5218 ,用它可以表示逻辑电路图、逻辑表达式等数字逻辑功能。特点:verilog很多操作符和结构类似与C语言,比如

2021-11-06 09:05:57 15

15 公众号自取代码MSP430的代码Verilog和VHDL都有,80C51的是Verilog写的,感兴趣的可以下载参考。关注公众号:AriesOpenFPGA回复:MSP430

2021-11-20 15:06:08 14

14 #ifndef HC32L1XX_LL_SYSTEM_H_#define HC32L1XX_LL_SYSTEM

2021-11-23 18:06:52 9

9 /*! \brief setup the microcontroller system, initialize the system \param[in] none

2021-12-06 10:36:10 7

7 Verilog HDL入门教程-Verilog HDL的基本语法

2022-01-07 09:23:42 189

189 Verilog HDL(Hardware Description Language)是在用途最广泛的C语言的基础上发展起来的一种硬件描述语言,具有灵活性高、易学易用等特点。Verilog HDL可以在较短的时间内学习和掌握,目前已经在FPGA开发/IC设计领域占据绝对的领导地位。

2022-09-13 14:34:20 1858

1858 第一句话是:还没学数电的先学数电。然后你可以选择verilog或者VHDL,有C语言基础的,建议选择VHDL。因为verilog太像C了,很容易混淆,最后你会发现,你花了大量时间去区分这两种语言,而

2022-11-03 09:02:56 5102

5102 一个掌握Verilog语言的工程师初次看SystemVerilog都会有这样的感受,这就是Verilog啊,很容易啊,So easy啊。没错,确实是这样,System Verilog的产生

2022-12-09 15:08:05 5582

5582 一个复杂电路系统的完整Verilog HDL模型是由若干个Verilog HDL模块构成的,每一个模块又可以由若干个子模块构成。其中有些模块需要综合成具体电路,而有些模块只是与用户所设计的模块有交互联系的现存电路或激励信号源。

2023-02-02 10:03:38 12465

12465 fpga学习,verilog学习,verilog经典学习代码

2023-02-13 09:32:15 23

23 System Verilog(SV)语言的Class本身就带有“打包”的基因。众所周知,SV语言的很多特性是派生自C++语言的。

2023-03-15 13:55:25 1417

1417 FPGA需要良好的数电模电基础,verilog需要良好C语言基础。

2023-05-11 17:30:07 3320

3320

FPGA需要良好的数电模电基础,verilog需要良好C语言基础。

2023-05-22 15:04:29 1434

1434

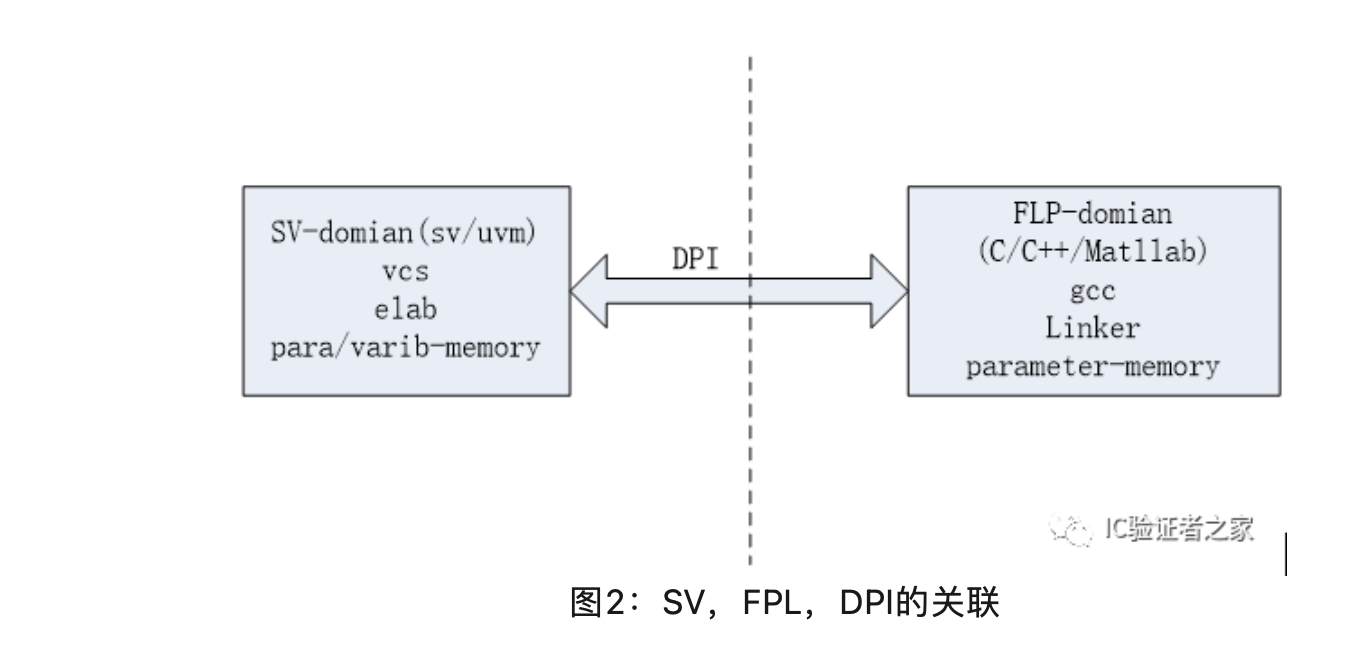

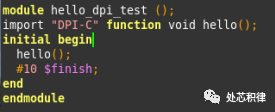

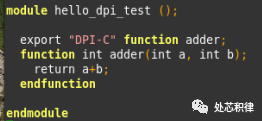

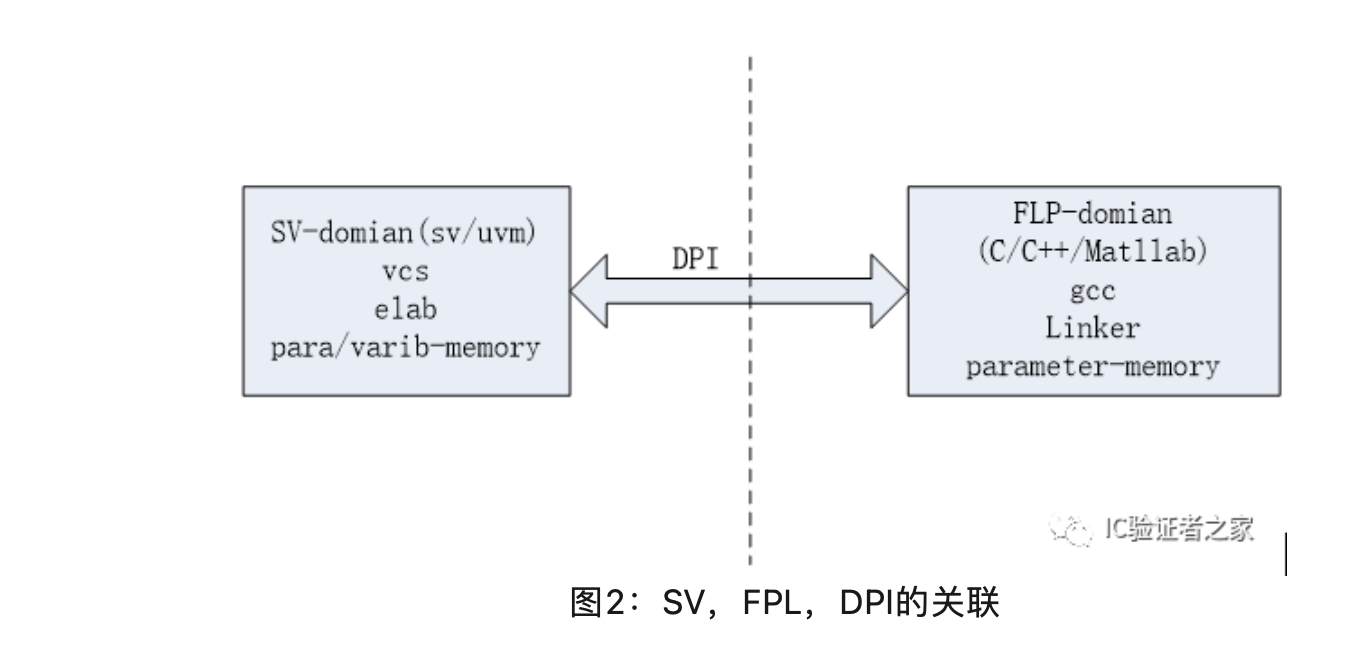

System Verilog(SV)把其他编程语言统一成为外语,Foreign Programming Language(FPL)。

2023-05-23 15:39:00 3529

3529

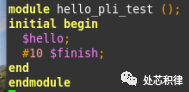

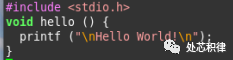

PLI全称 Program Language Interface,程序员可以通过PLI在verilog中调用C函数,这种访问是双向的。

2023-06-01 17:32:22 2625

2625

Verilog模块之间的连接是通过模块端口进行的。 为了给组成设计的各个模块定义端口,我们必须对期望的硬件设计有一个详细的认识。 不幸的是,在设计的早期,我们很难把握设计的细节。 而且,一旦模块

2023-06-12 10:05:01 2277

2277 读者如果学习了verilog,并且有了一定的实践经验的话应该强烈的感受到,verilog和软件(诸如C/C++)有着本质且明显的差别,是一条不可跨越的鸿沟。

2023-06-28 10:44:32 1111

1111

Verilog大量例程(简单入门到提高)

2023-08-16 11:49:31 5

5 电子发烧友网为你提供ADI(ADI)DS28C40EVKIT: Evaluation System for the DS28C40 Data Sheet相关产品参数、数据手册,更有

2023-10-17 19:20:20

Verilog中的模块端口对应方式,并提供示例代码和详细解释,以帮助读者更好地理解和应用。 首先,我们来了解一下Verilog中的模块和模块端口。一个Verilog模块被定义为包含一组声明和语句的代码块,类似于C语言中的函数。模块可以有输入端口(input)、输出端口(output)

2024-02-23 10:20:32 3071

3071 FPGA(现场可编程逻辑门阵列)开发主要使用的编程语言是硬件描述语言(HDL),其中Verilog是最常用的编程语言之一。而C语言通常用于传统的软件编程,与FPGA的硬件编程有所区别。

2024-03-27 14:38:14 3907

3907 谈谈 十折交叉验证训练模型

2024-05-15 09:30:17 2481

2481 ICer需要System Verilog语言得加成,这是ICer深度的表现。

2024-11-01 10:44:36 0

0 Verilog 与 VHDL 比较 1. 语法和风格 Verilog :Verilog 的语法更接近于 C 语言,对于有 C 语言背景的工程师来说,学习曲线较平缓。它支持结构化编程,代码更直观,易于

2024-12-17 09:44:44 2877

2877 Verilog测试平台设计方法是Verilog FPGA开发中的重要环节,它用于验证Verilog设计的正确性和性能。以下是一个详细的Verilog测试平台设计方法及Verilog FPGA开发

2024-12-17 09:50:06 1631

1631 Verilog与ASIC设计的关系 Verilog作为一种硬件描述语言(HDL),在ASIC设计中扮演着至关重要的角色。ASIC(Application Specific Integrated

2024-12-17 09:52:26 1543

1543 ZYNQ SoC 的 PS (Processing System) 和 PL (Programmable Logic) 之间的数据交互是系统设计的核心。

2025-10-15 10:33:19 738

738

电子发烧友App

电子发烧友App

评论