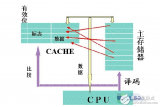

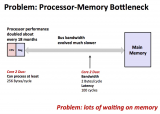

Cache是位于CPU与主存储器即DRAM(Dynamic RAM,动态存储器)之间的少量超高速静态存储器SRAM(Static RAM)

2023-10-31 15:07:23 1356

1356

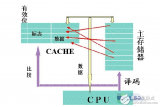

靠近 CPU 的小、快速的高速缓存存储器(cache memory)做为一部分存储在相对慢速的主存储器(main memory)中数据和指令的缓冲区域。

2023-12-25 09:21:50 2505

2505

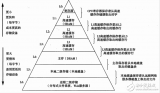

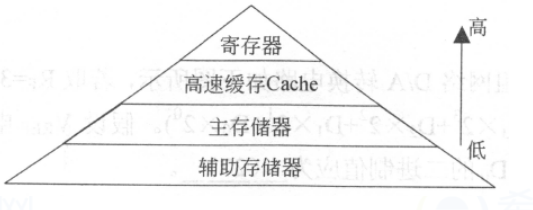

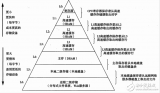

存储器的层次结构是怎样的?由哪些部分组成的?有何特点?Cache的原理是什么?Cache地址的过程是怎样的?

2021-12-23 09:35:31

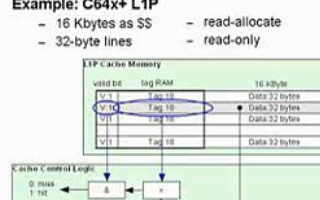

的L1 Cache存储管理段式存储管理页式存储管理存储系统的层次结构技术指标层次结构局部性原理主存储器读写存储器只读存储器存储器地址译码主存空间分配高速缓冲存储器工作原理地址映射替换算法写入策略80486的L1 CachePentium的L1 Cache存储管理段式存储管理页式存

2021-07-29 09:47:21

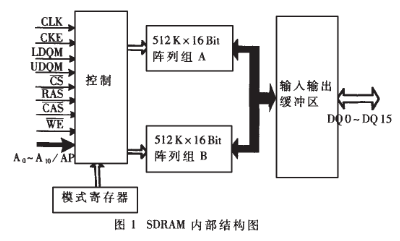

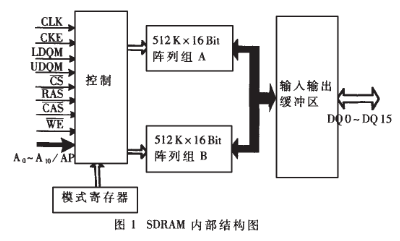

高速SDRAM存储器接口电路设计SDRAM可作为软嵌入式系统的(NIOSII)的程序运行空间,或者作为大量数据的缓冲区。SDRAM是通用的存储设备,只要容量和数据位宽相同,不同公司生产的芯片都是兼容

2019-06-03 05:00:07

概述:IDT70V9289是一款高速同步双口静态存储器(SRAM),可实现不同传输方式的双路高速数据流的无损传输,它主要由I/O控制器、存储器阵列、计数器/地址寄存器和一些逻辑电路组成。

2021-04-08 08:06:26

存储器系统的层次架构是如何构成的?高速缓存(cache)的工作原理是什么?高速缓存可分为哪几类?

2021-12-23 06:18:10

什么是高速缓存?• 高速存储器块,包含地址信息(通常称作TAG)和相关联的数据。• 目的是提高对存储器的平均访问速度• 高速缓存的应用基于下面两个程序的局部性 :• 空间局部性:如果一个存储器的位置

2023-09-07 08:22:51

一、cache分类及应用场合cache是内存和CPU之间的高速缓冲存储器,其分为icache(指令缓存)和dcache(数据缓存)。如果开启了cache,当CPU运行时会将正在运行的指令地址附近

2022-05-11 17:43:27

单片机和ARM处理器内存管理单元(MMU)高速缓冲存储器(CACHE)指令集ARM的指令系统ARM处理器工作模式ARM处理器的内部寄存器ARM处理器的异常ARM中断向量ARM架构的发展..

2021-07-16 07:18:14

read [2048],RDBUF定义为2048.基本上,我尝试从缓冲存储器中读取测量数据。任何人都可以对这个问题有所了解吗?非常感谢。 -Martin 以上来自于谷歌翻译 以下为原文Hi, I

2018-09-20 11:20:35

超大规模的集成电路,主要逻辑架构包括控制单元Control,运算单元ALU和高速缓冲存储器(Cache)及实现它们之间联系的数据(Data)、控制及状态的总线(Bus)。简单说,就是计算单元、控制单...

2021-07-26 07:02:18

相比,LL2 存储器器件和控制器的时钟运行速率更高。C66x LL2 存储器以等同于 CPU 时钟的时钟速率运行。更高的时钟频率可实现更快的访问时间,从而减少了因 L1 高速缓存失效造成的停滞,在此

2011-08-13 15:45:42

ML2308是立体声录音/播放LSI,在单个芯片中集成了录音和播放音频数据所需的所有功能。话筒或线入的模拟信号被模-数转换器转换成数字信号,经由缓冲存储器输出到外部设备。此外,从外部设备输入

2011-03-13 22:16:58

用来作为计算机中的高速缓冲存储器(Cache)。DRAM是动态随机存储器(Dynamic Random Access Memory),它是利用场效应管的栅极对其衬底间的分布电容来保存信息,以存储电荷

2011-11-28 10:23:57

计算机指令以及处理计算机软件中的数据。中央处理器主要包括运算器(算术逻辑运算单元,ALU,Arithmetic Logic Unit)和高速缓冲存储器(Cache)及实现它们之间联系的数据(Dat...

2022-02-10 08:00:15

关于高速存储器的调试和评估,看完你就懂了

2021-05-11 06:28:25

关于数Gpbs高速存储器接口设计的分析,看完你就懂了

2021-05-19 06:38:12

对于逻辑芯片的嵌入存储器来说,嵌入式SRAM是最常用的一种,其典型的应用包括片上缓冲器、高速缓冲存储器、寄存器堆等。除非用到某些特殊的结构,标准的六管单元(6T)SRAM对于逻辑工艺有着很好的兼容性。对于小于2Mb存储器的应用,嵌入式SRAM可能有更好的成本效率并通常首先考虑。

2019-08-28 08:18:27

如何实现扩展存储器的设计?

2021-10-28 08:08:51

DDR3存储器控制器面临的挑战有哪些?如何用一个特定的FPGA系列LatticeECP3实现DDR3存储器控制器。

2021-04-30 07:26:55

的工作时钟频率。然而,设计至DDR3的接口也变得更具挑战性。在FPGA中实现高速、高效率的DDR3控制器是一项艰巨的任务。直到最近,只有少数高端(昂贵)的FPGA有支持与高速的DDR3存储器可靠接口的块

2019-08-09 07:42:01

如何用低成本FPGA解决高速存储器接口挑战?

2021-04-29 06:59:22

本文提出了一个网络存储器的基本解决方案,实现了网络存储器的基本功能。

2021-04-26 06:50:19

指令、数据和地址。在CPU中,通常有通用寄存器,如指令寄存器IR;特殊功能寄存器,如程序计数器PC、sp等CacheCache :即高速缓冲存储器,是位于CPU与主内存间的一种容量较小但速度很高

2022-01-05 06:26:06

引言 随着CPU速度的迅速提高,CPU与片外存储器的速度差异越来越大,匹配CPU与外部存储器的方法通常是采用Cache或者片上存储器。微处理器中片上存储器结构通常包含指令Cache ,数据

2019-07-02 07:44:45

第四章微型计算机的存储设备4.1 内存内存是计算机中数据存储和交换的设备。在整个计算机中内存起着调节CPU和外部存储器之间速度差异过大的作用。内存包括Cache(高速缓冲存储器)、ROM(只读存储器

2021-09-10 09:02:31

如何满足各种读取数据捕捉需求以实现高速接口?怎么缩短高端存储器接口设计?

2021-04-29 07:00:08

寄存器、 控制与状态寄存器, 以及高速缓冲存储器(Cache)控制部件: 实现各部件间联系的数据、 控制及状态的内部总线; 负责对指令译码、发出为完成每条指令所要执行操作的控制信号、 ...

2021-07-26 07:46:25

高速缓存作为中央处理器 (CPU) 与主存之间的小规模快速存储器,解决了两者数据处理速度的平衡和匹配问题,有助于提高系统整体性能。多处理器 (SMP) 支持共享和私有数据的缓存,Cache 一致性

2021-02-23 07:12:38

数据存储器 FLASH程序存储器 FLASH数据存储器 片内RAM数据存储器16M字节外部数据存储器各有什么区别?特点?小弟看到这段 很晕。ADuC812的用户数据存储器包含三部分,片内640字节的FLASH数据存储器、256字节的RAM以及片外可扩展到16M字节的数据存储器。求助高手。解释一下不同。

2011-11-29 09:50:46

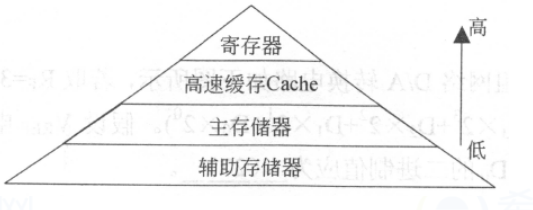

磁盘、内存、闪存、缓存等物理存储介质的区别计算机系统中存在多种物理存储介质,比较有代表性的有以下几种介质。寄存器(register)高速缓冲存储器(cache),即缓存主存储器...

2021-07-22 08:10:55

随着CPU速度的迅速提高,CPU与片外存储器的速度差异越来越大,匹配CPU与外部存储器的方法通常是采用Cache或者片上存储器。微处理器中的片上存储器结构通常包含指令Cache、数据Cache或者片上存储器。

2019-11-11 07:03:58

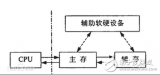

4.2 主存储器4.3 高速缓冲存储器4.4 辅助存储器

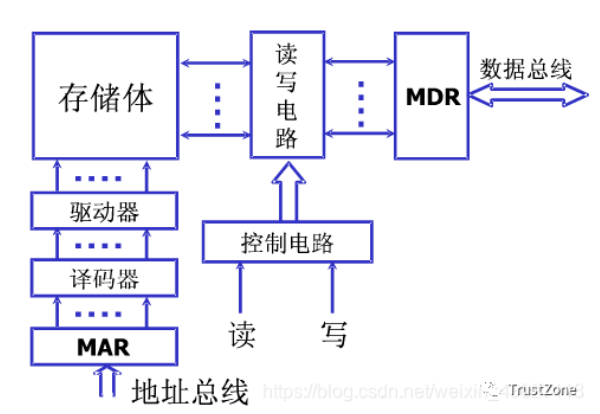

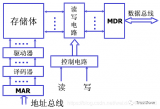

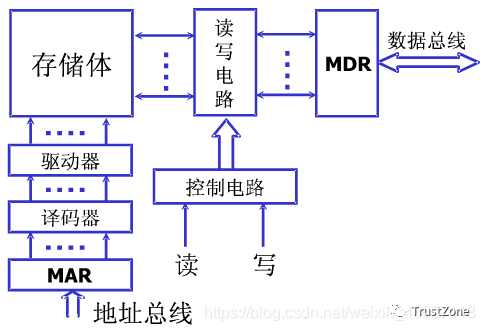

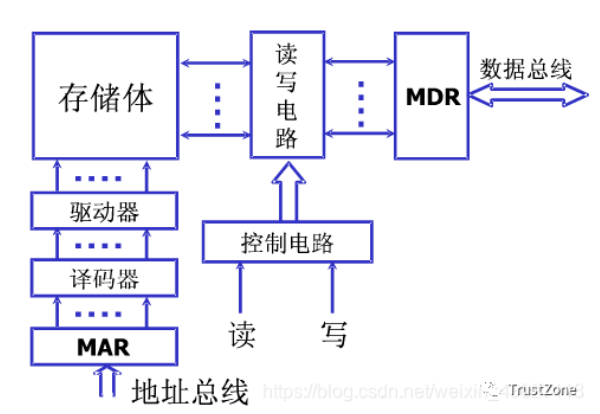

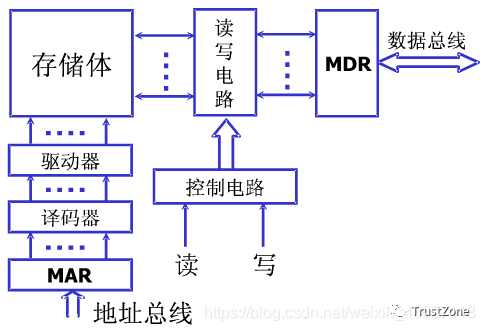

主存的基本组成

2009-04-11 09:34:52 0

0 针对嵌入式CPU 指令处理速度与存储器指令存取速度不匹配问题,本文基于FPGA 设计并实现了可以有效解决这一问题的指令Cache。根据嵌入式五级流水线CPU 特性,所设计指令Cache 的地

2009-08-05 14:27:54 36

36 不同的应用对存储器结构有不同的需求:在运行控制任务时,需要Cache 匹配速度差异;在处理数据流时,需要片内存储器提高访问带宽。本文设计了一种基于SRAM 的可配置Cache/SRAM

2010-01-25 11:53:55 24

24 ML2308是立体声录音/播放LSI,在单个芯片中集成了录音和播放音频数据所需的所有功能。话筒或线入的模拟信号被模-数转换器转换成数字信号,经由缓冲存储器输出到外部设备。此外

2010-07-13 21:57:10 34

34 高速缓冲存储器Cache在微处理器中已经成为至关重要的一部分,它的使用能有效地缓和CPU和主存之间速度匹配的问题。本文以32位S698M微处理器的高速缓冲存储器Cache为例,分析了Cac

2010-09-13 08:19:14 9

9 存储器的分类

内部存储器的系统结构

动、静态读写存储器RAM的基本存储单元与芯片

2010-11-11 15:35:22 67

67 摘要:磁电存储器不仅存取速度快、功耗小,而且集动态RAM、磁盘存储和高速缓冲存储器功能于一身,因而已成为动态存储器研究领域的一个热点。文章总结了磁电

2006-03-24 13:01:37 2314

2314

相变存储器:能实现全新存储器使用模型的新型存储器

从下面的几个重要特性看,相变存储器(PCM)技术均符合当前电子系统对存储器子系统的需求:

容量

2009-12-31 10:09:30 1360

1360 什么是缓存Cache

即高速缓冲存储器,是位于CPU与主内存间的一种容量较小但速度很高的存储器。由于CPU的速度远高于主内存,CPU直接

2010-01-23 10:57:13 1068

1068 什么是Cache/SIMD?

Cache :即高速缓冲存储器,是位于CPU与主内存间的一种容量较小但速度很高的存储器。由于CPU的速度远高于主内存

2010-02-04 11:29:44 586

586 什么是处理器缓存处理器缓存:

Cache(高速缓冲存储器)是位于CPU与主内存间的一种容量较小但速度很高的存储器。由于CPU的速度远

2010-02-04 12:02:26 1093

1093 什么是Cache

英文缩写: Cache

中文译名: 高速缓存器

分 类: IP与多媒体

解 释: 信息在本地的临时存储

2010-02-22 17:26:39 1141

1141 高速缓存(Cache),高速缓存(Cache)原理是什么?

高速缓存Cache是位于CPU和主存储器之间规模较小、存取速度快捷的静态存储器。Cache一般由

2010-03-26 10:49:27 7135

7135 高速缓冲存储器部件结构及原理解析

高速缓存 CACHE用途 设置在 CPU 和 主存储器之间,完成高速与 CPU交换信息,尽量避免 CPU不必要地多次直

2010-04-15 11:18:50 5035

5035 介绍一种单片机系统中 高速数据采集 的实现方法,在单片机与高速A/D转换器之间以静态存储器作缓冲器,采用A/D转换器直接写存储器的方式提高采样频率,实现高速数据采集。并给出了设

2011-07-18 16:59:08 193

193 基于FPGA的高速固态存储器优化设计_杨玉华

2017-01-13 21:40:36 1

1 低功耗的高性能四路组相联CMOS高速缓冲存储器

2017-01-19 21:22:54 12

12 Cache又叫高速缓冲寄存器,位于CPU与内存之间,是一种特殊的存储器子系统。根据局部性原理,可以在主存和CPU之间设置一个高速的,容量相对较少的存储器,如果当前正在执行的程序和数据存放在

2017-09-12 19:05:37 18

18 15.3 高速缓冲存储器Cache 当第一代RISC微处理器刚出现时,标准存储器元件的速度比当时微处理器的速度快。很快,半导体工艺技术的进展被用来提高微处理器的速度。标准DRAM部件虽然也快了一些

2017-10-17 16:36:21 1

1 高速缓冲存储器(Cache)其原始意义是指存取速度比一般随机存取记忆体(RAM)来得快的一种RAM,一般而言它不像系统主记忆体那样使用DRAM技术,而使用昂贵但较快速的SRAM技术,也有快取记忆体的名称。

2017-11-15 09:50:40 7982

7982

高速缓冲存储器是存在于主存与CPU之间的一级存储器, 由静态存储芯片(SRAM)组成,容量比较小但速度比主存高得多, 接近于CPU的速度。在计算机技术发展过程中,主存储器存取速度一直比中央处理器操作速度慢得多

2017-11-15 10:08:08 11646

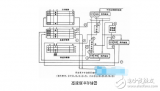

11646 高速缓冲存储器通常由高速存储器、联想存储器、替换逻辑电路和相应的控制线路组成。在有高速缓冲存储器的计算机系统中,中央处理器存取主存储器的地址划分为行号、列号和组内地址三个字段。于是,主存储器就在逻辑上划分为若干行;每行划分为若干的存储单元组

2017-11-15 10:38:11 4512

4512

高速缓冲存储器(Cache)其原始意义是指存取速度比一般随机存取记忆体(RAM)来得快的一种RAM,一般而言它不像系统主记忆体那样使用DRAM技术,而使用昂贵但较快速的SRAM技术,也有快取记忆体的名称。

2017-12-06 15:26:45 21881

21881

高速缓冲存储器(Cache)其原始意义是指存取速度比一般随机存取记忆体(RAM)来得快的一种RAM基于缓存的存储器层次结构行之有效,是因为较慢的存储设备比较快的存储设备更便宜,还因为程序往往展示局部性:

2017-12-06 17:35:42 11320

11320

许多 FPGA 设计都采用高速存储器接口,可能调试比较困难,不过只要采用正确的方法就能成功进行调试。 现代 FPGA 通常连接高速 SRAM 和 SDRAM 存储器 。要确保这种器件无差错运行,调试

2018-01-12 11:48:44 1662

1662

以及处理计算机软件中的数据。中央处理器主要包括运算器(算术逻辑运算单元,ALU,Arithmetic Logic Unit)和高速缓冲存储器(Cache)及实现它们之间联系的数据(Data)、控制

2018-01-26 10:05:22 13109

13109

在计算机存储系统的层次结构中,介于中央处理器和主存储器之间的高速小容量存储器。它和主存储器一起构成一级的存储器。高速缓冲存储器和主存储器之间信息的调度和传送是由硬件自动进行的。

2018-05-08 11:15:00 9659

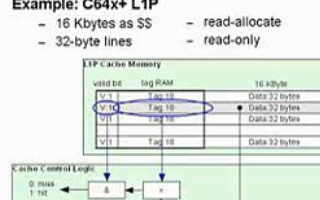

9659 TMS320C64x+网络课程5——多极高速缓冲存储器,包cache的概念,cache miss的一些类型以及关于cache的使用优化。此网络培训针对C64x+,每次一个专题,由DSP高性能部门技术支持工程师为您全程指导,敬请期待。

2018-06-26 13:00:00 4541

4541

其他元件,占用了宝贵的电路板空间。

Stratix® III FPGA具有专用内置I/O电路,降低了高速DDR3存储器设计的难度。观看这一演示,了解怎样轻松实现1,067 Mbps DDR3存储器

2018-06-22 02:04:00 4421

4421 在多媒体应用中,多媒体信息绝大部分是视频数据和音频数据,而数字化的视频数据和音频数据的数据量是非常庞大的。为了能够及时完整地处理前端采集的数据,一般系统都采用高速DSP和大容量缓冲存储器,且

2020-04-09 08:02:00 3433

3433

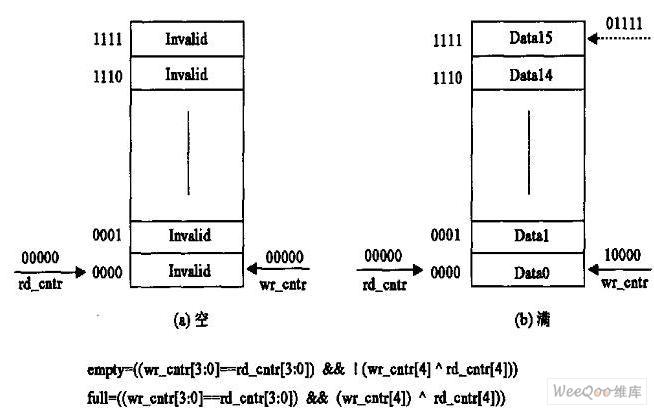

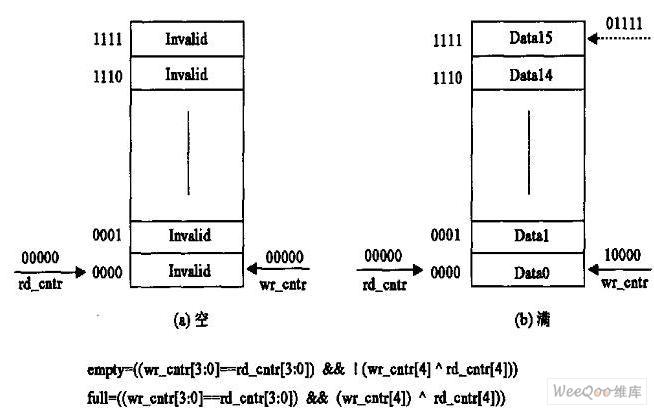

本32X8 FIFO的设计,采用了双体存储器的交替读写机制,使得在对其中一个存储器写操作的同时可以对另一个存储器进行读操作;对其中一个存储器读操作的同时可以对另一个存储器进行写操作。实现了高速数据缓冲,速度比单体存储器的FIFO提高了一倍。

2018-12-30 10:29:00 4312

4312

内存储器包括寄存器、高速缓冲存储器(Cache)和主存储器。寄存器在CPU芯片的内部,高速缓冲存储器也制作在CPU芯片内,而主存储器由插在主板内存插槽中的若干内存条组成。内存的质量好坏与容量大小会影响计算机的运行速度。

2019-01-07 16:54:32 35723

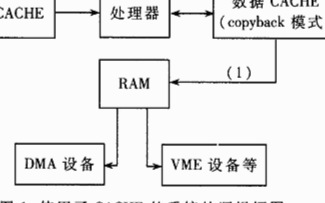

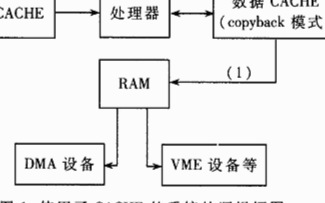

35723 (2)在有DMA控制器的系统和多处理器系统中,有多个部件可以访问主存。这时,可能其中有些部件是直接访问主存,也可能每个DMA部件和处理器配置一个CACHE。这样,主存的一个区块可能对应于多个

2020-10-04 16:55:00 2508

2508

随机存储存储器,可读可写,分为SRAM和DRAM,即静态随机存储器和动态随机存储器,理解上静动态主要体现是否需要刷新,通常DRAM需要刷新,否则数据将丢失;SRAM的效率较好,而成本较高,通常将SRAM作为cache使用。

2021-03-18 15:14:06 5292

5292 EE-271: 高速缓冲存储器在Blackfin®处理器中的应用

2021-03-21 07:50:52 8

8 计算机指令以及处理计算机软件中的数据。中央处理器主要包括运算器(算术逻辑运算单元,ALU,Arithmetic Logic Unit)和高速缓冲存储器(Cache)及实现它们之间联系的数据(Dat...

2021-12-06 16:51:11 9

9 CPU从存储器或高速缓冲存储器中取出指令,放入指令寄存器,并对指令译码,并执行指令。

2022-02-08 15:22:45 0

0 均在CPU外部,Cache和主存构成内存储系统,程序员通过总线寻址访问存储单元,访问速度较寄存器差;虚拟存储器对程序员而言是透明的 ;外部存储系统容量大,需通过I/O接口与CPU交换数据,访问速度最慢。 高速缓冲存储器 高速缓冲存储器(Cache)的原始

2022-06-18 20:47:10 7216

7216

存储器分为内部存储器、高速缓冲存储器和外部存储器。内部存储器简称为内存,计算机要执行的程序、要处理的信息和数据,都必须先存入内存,才能由CPU取出并进行处理。

2022-07-21 16:14:52 3281

3281 MELSEC iQ-R 高速模-数转换模块用户手册(应用篇) 产品规格书.以下对介绍本手册的功能、输入输出信号及缓冲存储器等的页面构成进行说明。

2022-08-26 15:52:47 0

0 Cache被称为高速缓冲存储器(cache memory),是一种小容量高速的存储器,属于存储子系统的一部分,存放程序常使用的指令和数据。

2023-03-06 15:05:31 7690

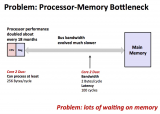

7690 Cache存储器也被称为高速缓冲存储器,位于CPU和主存储器之间。之所以在CPU和主存之间要加cache是因为现代的CPU频率大大提高,内存的发展已经跟不上CPU访存的速度。在2001 – 2005

2023-03-21 14:34:53 2168

2168

GPU(图形处理器)最初是为了解决 CPU 在图形处理领域性能不足的问题而诞生。CPU 作为核心控制计算单元,高速缓冲存储器(Cache)、控制单元(Control)在 CPU 硬件架构设计中所占比例较大

2023-05-15 11:00:45 2267

2267

,Arithmetic Logic Unit)和高速缓冲存储器(Cache)及实现它们之间联系的数据(Data)、控制及状态的总线(Bus)。

2023-10-15 10:49:55 5060

5060

Cache是位于CPU与主存储器即DRAM(Dynamic RAM,动态存储器)之间的少量超高速静态存储器SRAM(Static RAM),它是为了解决CPU与主存之间速度匹配问题而设置的,不能由用户直接寻址访问。

2023-10-17 10:37:47 1875

1875

具有Cache的计算机,当CPU需要进行存储器存取时,首先检查所需数据是否在Cache中。如果存在,则可以直接存取其中的数据而不必插入任何等待状态,这是最佳情况,称为高速命中; 当CPU所需信息不在

2023-10-31 11:34:46 1974

1974

提高高速缓存命中率的最好方法是尽量使Cache存放CPU最近一直在使用的指令与数据,当Cache装满后,可将相对长期不用的数据删除,提高Cache的使用效率。 为保持Cache中数据与主存储器中数据

2023-10-31 11:43:37 2199

2199 使用Cache的必要性 所谓Cache即高速缓冲存储器,它位于CPU与主存即DRAM之间,是通常由SRAM构成的规模较小但存取速度很快的存储器。 目前计算机主要使用的内存为DRAM,它具有价格低

2023-10-31 11:53:54 1522

1522 )两大类组成,以及还包括一些高速缓存(Cache)和寄存器(Register)等。下面将详细介绍这些内部存储器的工作原理、作用以及它们之间的区别。

2024-09-05 10:42:19 7305

7305 高速缓冲存储器(Cache),通常简称为缓存,是一种具有高速存取能力的存储器。其原始意义是指存取速度比一般随机存取存储器(RAM)更快的一种RAM。高速缓冲存储器一般采用静态随机存储器(SRAM

2024-09-10 14:09:28 4405

4405 高速缓冲存储器(Cache)与内存(Memory)在计算机体系结构中扮演着至关重要的角色,它们之间存在显著的区别。以下将从定义、功能、技术特点、作用机制等多个方面详细阐述这两者的区别。

2024-09-10 14:12:09 4258

4258 高速缓冲存储器(Cache)的工作原理,是基于计算机程序和数据访问的局部性原理,即程序在执行过程中,对数据的访问往往呈现出时间和空间的局部性。具体来说,就是程序在某一时间段内,会集中访问某一小块内存

2024-09-10 14:14:53 2059

2059 Cache(高速缓存)和内存(Memory,通常指主存储器或RAM)是计算机存储系统中两个重要的组成部分,它们在计算机的性能和数据处理中扮演着不同的角色。以下是对Cache和内存之间区别的详细解析。

2024-09-26 15:28:27 6082

6082 缓存(Cache)是一种高速存储器,用于临时存储数据,以便快速访问。在计算机系统中,缓存的作用是减少处理器访问主存储器(如随机存取存储器RAM)所需的时间。 缓存(Cache)概述 缓存是一种位于

2024-12-18 09:28:31 15992

15992 高速缓冲存储器(Cache)是内存的一种特殊形式,但它与通常所说的主存储器(RAM)有所不同。在计算机存储体系中,Cache位于CPU和主存储器之间,用于存储CPU近期访问过的数据或指令,以加快数据的访问速度。

2025-01-29 11:48:00 3399

3399 电子发烧友网站提供《EE-271: 高速缓冲存储器在Blackfin处理器中的应用.pdf》资料免费下载

2025-01-07 14:18:17 0

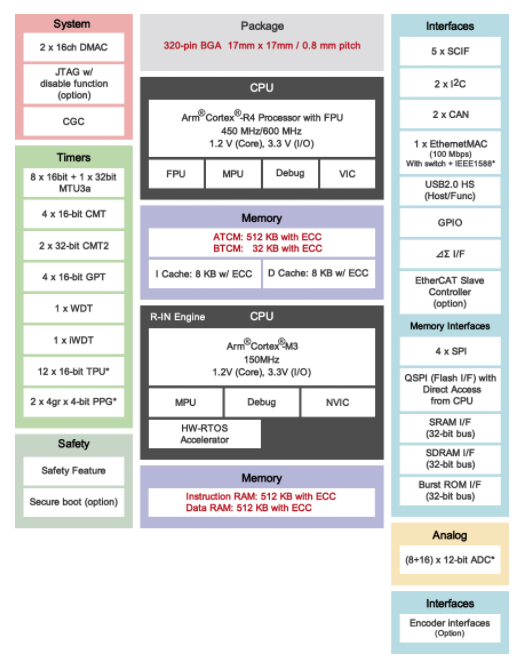

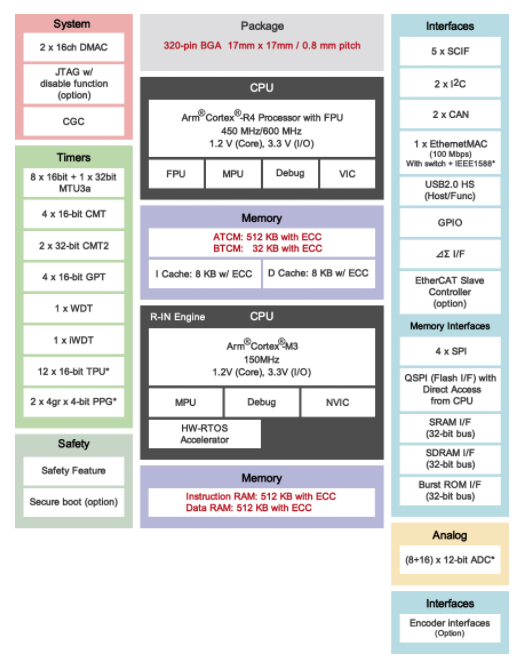

0 可进行明确的实时响应处理,无需通过高速缓冲存储器即可实现从 CPU 的高速访问, 内置的瑞萨电子R-IN 引擎的 RZ/T1 设备是工业以太网通信的加速器,可通过硬件 RTOS(HW-RTOS)执行工业以太网处理,而不会损失实时性能。RZ/T1配备了可配置的绝对编码器接口,非常适合精密运动控制应用

2025-03-13 17:53:30 893

893

电子发烧友App

电子发烧友App

评论