资料介绍

15.3 高速缓冲存储器Cache

当第一代RISC微处理器刚出现时,标准存储器元件的速度比当时微处理器的速度快。很快,半导体工艺技术的进展被用来提高微处理器的速度。标准DRAM部件虽然也快了一些,但其发展的主要精力则放在提高存储容量上。

1980年,典型DRAM部件的容量为4KB。1981年和1982年开发出了16KB芯片。这些部件的随机访问速率为3MHz或4MHz,局部访问(页模式)时速率大约快1倍。当时的微处理器每秒需要访问存储器2M次。

到2000年,DRAM部件每片的容量到达256Mbit,随机访问速率在30MHz左右。微处理器每秒需要访问存储器几百兆次。如果处理器速率远高于存储器,那么只能借助Cache才能满足其全部性能。

Cache存储器是一个容量小但存取速度非常快的存储器,它保存最近用到的存储器数据拷贝。对于程序员来说,Cache是透明的。它自动决定保存哪些数据、覆盖哪些数据。现在Cache通常与处理器在同一芯片上实现。Cache能够发挥作用是因为程序具有局部性特性。所谓局部性就是指,在任何特定的时间,微处理器趋于对相同区域的数据(如堆栈)多次执行相同的指令(如循环)。

Cache经常与写缓存器(write buffer)一起使用。写缓存器是一个非常小的先进先出(FIFO)存储器,位于处理器核与主存之间。使用写缓存的目的是,将处理器核和Cache从较慢的主存写操作中解脱出来。当CPU向主存储器做写入操作时,它先将数据写入到写缓存区中,由于写缓存器的速度很高,这种写入操作的速度也将很高。写缓存区在CPU空闲时,以较低的速度将数据写入到主存储器中相应的位置。

通过引入Cache和写缓存区,存储系统的性能得到了很大的提高,但同时也带来了一些问题。比如,由于数据将存在于系统中的不同的物理位置,可能造成数据的不一致性;由于写缓存区的优化作用,可能有些写操作的执行顺序不是用户期望的顺序,从而造成操作错误。

15.3.1 Cache的分类

Cache有多种构造方法。在最高层次,微处理器可以采用下面两种组织中的一组。

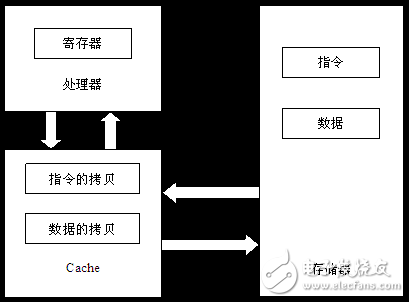

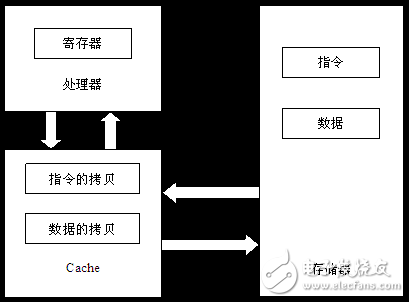

(1)统一Cache。指令和数据用同一个Cache。结构如图15.8所示。

图15.8 统一的指令Cache和数据Cache

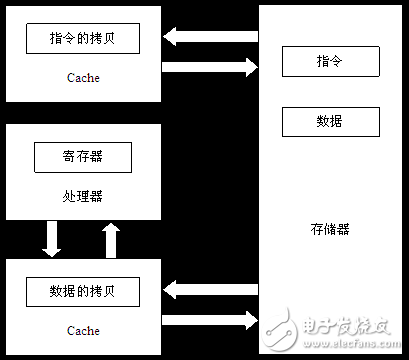

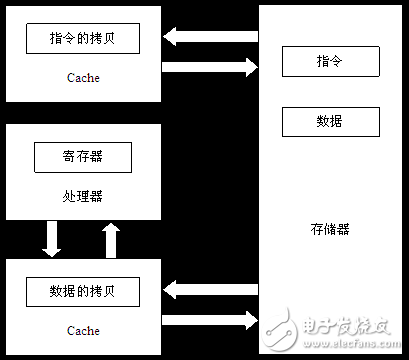

(2)指令和数据分开的Cache。有时这种组织方式也被称为改进的哈佛结构。

图15.9显示了这种组织方式。

这两种组织方式各有优缺点。统一Cache能够根据当前程序的需要自动调整指令在Cache存储器的比例,比固定划分的有更好的性能。另一方面,分开的Cache使Load/Store指令能够单周期执行。

15.3.2 Cache性能的衡量

只有当所需要的Cache存储器内容已经在Cache时,微处理器才能以高时钟速率工作。因此,系统的总体性能就可以用存储器访问中命中Cache的比例来衡量。当要访问的内容在Cache时称为命中(hit),而要访问的内容不在Cache时称为未命中(miss)。在给定时间间隔内,Cache命中的次数与总的存储器请求次数的比值被称为命中率。

图15.9 指令Cache和数据分开的Cache

命中率用下面的公式进行计算:

命中率=(Cache命中次数÷存储器请求次数)×100%

未命中率与命中率形式相似,即在给定时间间隔内,Cache未命中的总次数除以总的存储器请求次数所得的百分比。未命中率与命中率之和等于100。

目前设计良好的处理器,Cache的未命中率只有百分之几。未命中率依赖多个Cache参数,包括Cache大小和组织。

15.3.3 Cache工作原理

Cache的基本存储单元为Cache行(Cache line)。存储系统把Cache和主存储器都划分为相同大小的行。Cache与主存储器交换数据是以行为基本单位进行的。每一个Cache行都对应于主存中的一个存储块(memory block)。

Cache行的大小通常是2L字节。通常情况下是16字节(4个字)和32字节(8个字)。如果Cache行的大小为2L字节,那么对主存的访问通常是2L字节对齐的。所以对于一个虚拟地址来说,它的bit[31∶L]位,是Cache行的一个标识。当CPU发出的虚拟地址的bit[31∶L]和Cache中的某行bit[31∶L]相同,那么Cache中包含CPU要访问的数据,即成为一次Cache命中。

为了加快Cache访问的速度,又将多个Cache行划分成一个Cache组(Cache Set)。Cache组中包含的Cache行的个数通常也为2的N次方的倍数。为了方便起见,取N=S。这样,一个Cache组中就包含2S个Cache行。这时,虚拟地址中的bit[L+S-1∶L]为Cache组的标识。虚拟地址中余下的位bit[31∶L+S]成为一个Cache标(Cache-tag)。它标识了Cache行中的内容和主存间的对应关系。

当第一代RISC微处理器刚出现时,标准存储器元件的速度比当时微处理器的速度快。很快,半导体工艺技术的进展被用来提高微处理器的速度。标准DRAM部件虽然也快了一些,但其发展的主要精力则放在提高存储容量上。

1980年,典型DRAM部件的容量为4KB。1981年和1982年开发出了16KB芯片。这些部件的随机访问速率为3MHz或4MHz,局部访问(页模式)时速率大约快1倍。当时的微处理器每秒需要访问存储器2M次。

到2000年,DRAM部件每片的容量到达256Mbit,随机访问速率在30MHz左右。微处理器每秒需要访问存储器几百兆次。如果处理器速率远高于存储器,那么只能借助Cache才能满足其全部性能。

Cache存储器是一个容量小但存取速度非常快的存储器,它保存最近用到的存储器数据拷贝。对于程序员来说,Cache是透明的。它自动决定保存哪些数据、覆盖哪些数据。现在Cache通常与处理器在同一芯片上实现。Cache能够发挥作用是因为程序具有局部性特性。所谓局部性就是指,在任何特定的时间,微处理器趋于对相同区域的数据(如堆栈)多次执行相同的指令(如循环)。

Cache经常与写缓存器(write buffer)一起使用。写缓存器是一个非常小的先进先出(FIFO)存储器,位于处理器核与主存之间。使用写缓存的目的是,将处理器核和Cache从较慢的主存写操作中解脱出来。当CPU向主存储器做写入操作时,它先将数据写入到写缓存区中,由于写缓存器的速度很高,这种写入操作的速度也将很高。写缓存区在CPU空闲时,以较低的速度将数据写入到主存储器中相应的位置。

通过引入Cache和写缓存区,存储系统的性能得到了很大的提高,但同时也带来了一些问题。比如,由于数据将存在于系统中的不同的物理位置,可能造成数据的不一致性;由于写缓存区的优化作用,可能有些写操作的执行顺序不是用户期望的顺序,从而造成操作错误。

15.3.1 Cache的分类

Cache有多种构造方法。在最高层次,微处理器可以采用下面两种组织中的一组。

(1)统一Cache。指令和数据用同一个Cache。结构如图15.8所示。

图15.8 统一的指令Cache和数据Cache

(2)指令和数据分开的Cache。有时这种组织方式也被称为改进的哈佛结构。

图15.9显示了这种组织方式。

这两种组织方式各有优缺点。统一Cache能够根据当前程序的需要自动调整指令在Cache存储器的比例,比固定划分的有更好的性能。另一方面,分开的Cache使Load/Store指令能够单周期执行。

15.3.2 Cache性能的衡量

只有当所需要的Cache存储器内容已经在Cache时,微处理器才能以高时钟速率工作。因此,系统的总体性能就可以用存储器访问中命中Cache的比例来衡量。当要访问的内容在Cache时称为命中(hit),而要访问的内容不在Cache时称为未命中(miss)。在给定时间间隔内,Cache命中的次数与总的存储器请求次数的比值被称为命中率。

图15.9 指令Cache和数据分开的Cache

命中率用下面的公式进行计算:

命中率=(Cache命中次数÷存储器请求次数)×100%

未命中率与命中率形式相似,即在给定时间间隔内,Cache未命中的总次数除以总的存储器请求次数所得的百分比。未命中率与命中率之和等于100。

目前设计良好的处理器,Cache的未命中率只有百分之几。未命中率依赖多个Cache参数,包括Cache大小和组织。

15.3.3 Cache工作原理

Cache的基本存储单元为Cache行(Cache line)。存储系统把Cache和主存储器都划分为相同大小的行。Cache与主存储器交换数据是以行为基本单位进行的。每一个Cache行都对应于主存中的一个存储块(memory block)。

Cache行的大小通常是2L字节。通常情况下是16字节(4个字)和32字节(8个字)。如果Cache行的大小为2L字节,那么对主存的访问通常是2L字节对齐的。所以对于一个虚拟地址来说,它的bit[31∶L]位,是Cache行的一个标识。当CPU发出的虚拟地址的bit[31∶L]和Cache中的某行bit[31∶L]相同,那么Cache中包含CPU要访问的数据,即成为一次Cache命中。

为了加快Cache访问的速度,又将多个Cache行划分成一个Cache组(Cache Set)。Cache组中包含的Cache行的个数通常也为2的N次方的倍数。为了方便起见,取N=S。这样,一个Cache组中就包含2S个Cache行。这时,虚拟地址中的bit[L+S-1∶L]为Cache组的标识。虚拟地址中余下的位bit[31∶L+S]成为一个Cache标(Cache-tag)。它标识了Cache行中的内容和主存间的对应关系。

下载该资料的人也在下载

下载该资料的人还在阅读

更多 >

- EE-271: 高速缓冲存储器在Blackfin处理器中的应用

- CPU、MCU和SOC的区别以及外设的概念理解

- EE-271: 高速缓冲存储器在Blackfin®处理器中的应用

- PLC系统的存储器分类详细资料介绍 4次下载

- 如何使用eMMC阵列进行高速固态存储器的研究与设计 33次下载

- 单片机存储器的工作原理和结构与半导体存储器的分类说明

- Trace32高速缓冲寄存器 18次下载

- 低功耗的高性能四路组相联CMOS高速缓冲存储器 12次下载

- 存储器和高速缓存技术

- S698M SoC芯片中Cache控制器的设计与实现

- ML2308双通道录音/播放LSI,内置缓冲存储器

- 半导体存储器电路及结构

- 存储器.ppt 0次下载

- 存储器接口

- 存储器的分类及原理

- 内存储器的分类和特点是什么 1040次阅读

- 内存储器分为随机存储器和什么 1354次阅读

- 内存储器与外存储器的主要区别 5552次阅读

- 存储器的定义和分类 1465次阅读

- PLC系统的存储器分类介绍 6769次阅读

- 存储器分类及各自优劣势介绍 5860次阅读

- 计算机存储器的作用和分类说明 1w次阅读

- 半导体存储器有哪些类型 1.6w次阅读

- 内存储器和外存储器的分类与区别 4w次阅读

- 随机存取存储器为什么叫随机存取存储器(结构、特点、分类、优缺点) 2.1w次阅读

- 计算机的存储器主要作用_计算机的存储器的分类介绍 1.1w次阅读

- Cache是什么 CPU和GPU对于cache的应用 8708次阅读

- 高速缓冲存储器基础知识详细介绍 1w次阅读

- 高速缓冲存储器的作用是什么_有什么特点 2w次阅读

- 存储器分类及各自特点有哪些 1.7w次阅读

下载排行

本周

- 1DC电源插座图纸

- 0.67 MB | 2次下载 | 免费

- 2AN158 GD32VW553 Wi-Fi开发指南

- 1.51MB | 2次下载 | 免费

- 3AN148 GD32VW553射频硬件开发指南

- 2.07MB | 1次下载 | 免费

- 4AN111-LTC3219用户指南

- 84.32KB | 次下载 | 免费

- 5AN153-用于电源系统管理的Linduino

- 1.38MB | 次下载 | 免费

- 6AN-283: Σ-Δ型ADC和DAC[中文版]

- 677.86KB | 次下载 | 免费

- 7SM2018E 支持可控硅调光线性恒流控制芯片

- 402.24 KB | 次下载 | 免费

- 8AN-1308: 电流检测放大器共模阶跃响应

- 545.42KB | 次下载 | 免费

本月

- 1ADI高性能电源管理解决方案

- 2.43 MB | 450次下载 | 免费

- 2免费开源CC3D飞控资料(电路图&PCB源文件、BOM、

- 5.67 MB | 138次下载 | 1 积分

- 3基于STM32单片机智能手环心率计步器体温显示设计

- 0.10 MB | 130次下载 | 免费

- 4使用单片机实现七人表决器的程序和仿真资料免费下载

- 2.96 MB | 44次下载 | 免费

- 53314A函数发生器维修手册

- 16.30 MB | 31次下载 | 免费

- 6美的电磁炉维修手册大全

- 1.56 MB | 24次下载 | 5 积分

- 7如何正确测试电源的纹波

- 0.36 MB | 17次下载 | 免费

- 8感应笔电路图

- 0.06 MB | 10次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935121次下载 | 10 积分

- 2开源硬件-PMP21529.1-4 开关降压/升压双向直流/直流转换器 PCB layout 设计

- 1.48MB | 420062次下载 | 10 积分

- 3Altium DXP2002下载入口

- 未知 | 233088次下载 | 10 积分

- 4电路仿真软件multisim 10.0免费下载

- 340992 | 191367次下载 | 10 积分

- 5十天学会AVR单片机与C语言视频教程 下载

- 158M | 183335次下载 | 10 积分

- 6labview8.5下载

- 未知 | 81581次下载 | 10 积分

- 7Keil工具MDK-Arm免费下载

- 0.02 MB | 73810次下载 | 10 积分

- 8LabVIEW 8.6下载

- 未知 | 65988次下载 | 10 积分

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论