DDR布线在PCB设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,线长匹配又是一个重要的环节。我们来回顾一下,DDR布线,线长匹配的基本原则是:地址,控制

2017-09-01 14:03:41 5793

5793

DDR布线在PCB设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,

2017-09-26 11:39:47 7323

7323

多年前,无线时代(Beamsky)发布了一篇文章关于DDR布线指导的一篇文章,当时在网络上很受欢迎,有很多同

2017-10-16 09:22:08 38670

38670

星形拓补就是地址线走到两片DDR中间再向两片DDR分别走线,菊花链就是用地址线把两片DDR“串起来”,就像羊肉串,每个DDR都是羊肉串上的一块肉,哈哈,开个玩笑。

2018-03-12 08:36:07 15781

15781

嵌入式DDR(Double Data Rate,双数据速率)设计是含DDR的嵌入式硬件设计中最重要和最核心的部分。随着嵌入式系统的处理能力越来越强大,实现的功能越来越多,系统的工作频率越来越高,DDR的工作频率也逐渐从最低的133 MHz提高到200 MHz,从而实现了更大的系统带宽和更好的性能。

2018-04-14 07:38:01 5112

5112

本文首先列出了DDR2布线中面临的困难,接着系统的讲述了DDR2电路板设计的具体方法,最后给出个人对本次电路设计的一些思考。

2020-11-20 10:28:35 8529

8529 上期和大家聊的电源PCB设计的重要性,那本篇内容小编则给大家讲讲存储器的PCB设计建议,同样还是以大家最为熟悉的RK3588为例,详细介绍一下DDR模块电路的PCB设计要如何布局布线。

2023-08-16 15:20:58 3894

3894

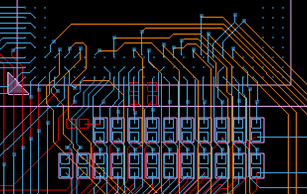

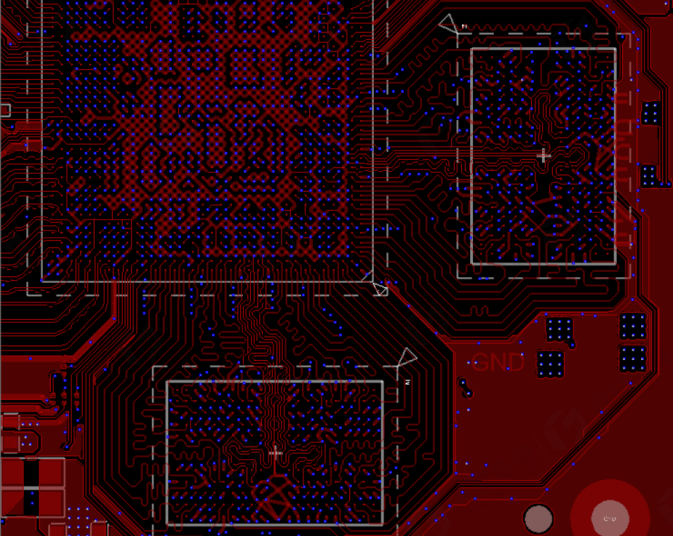

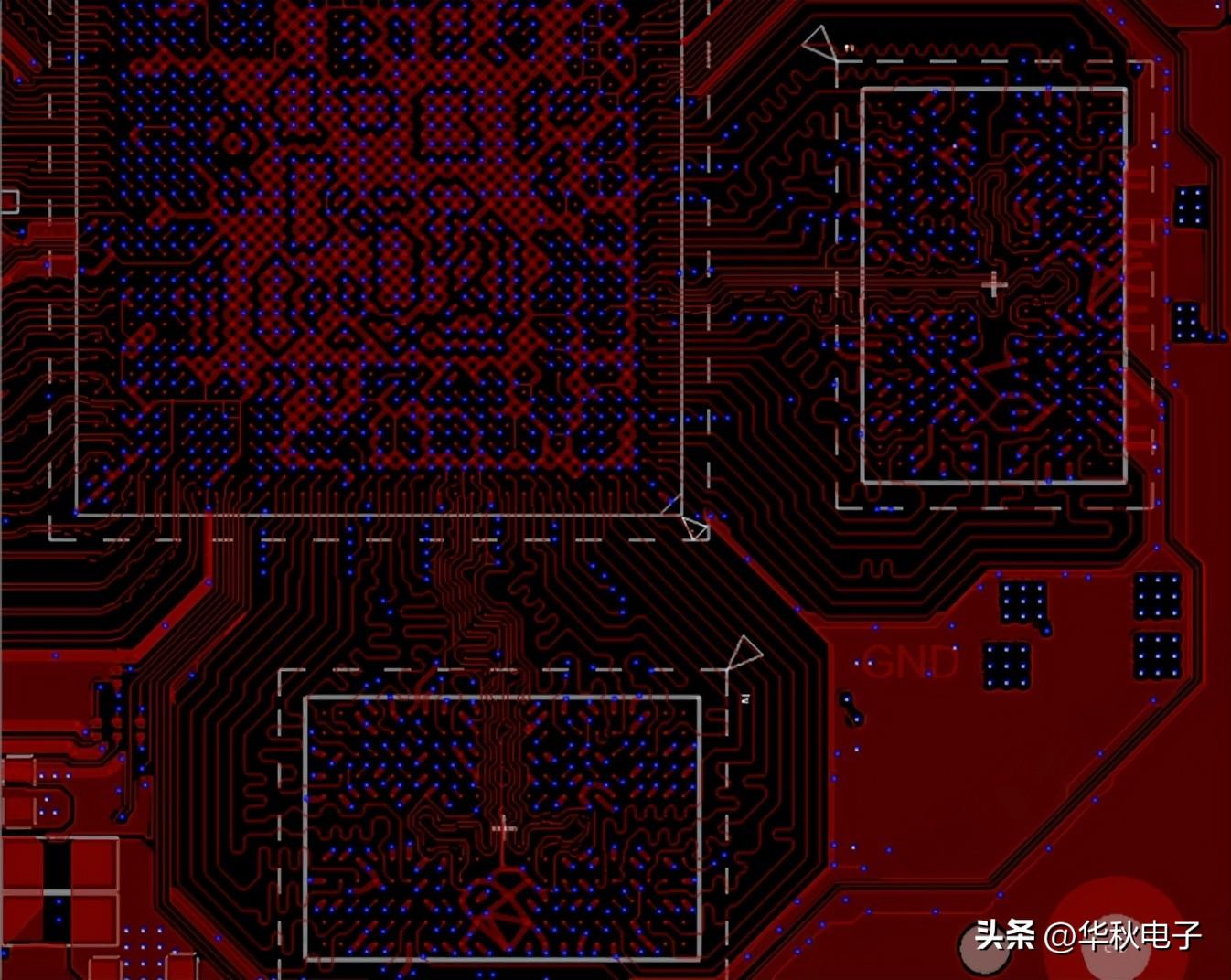

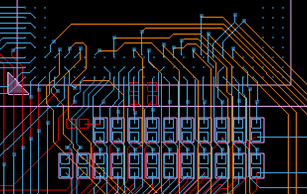

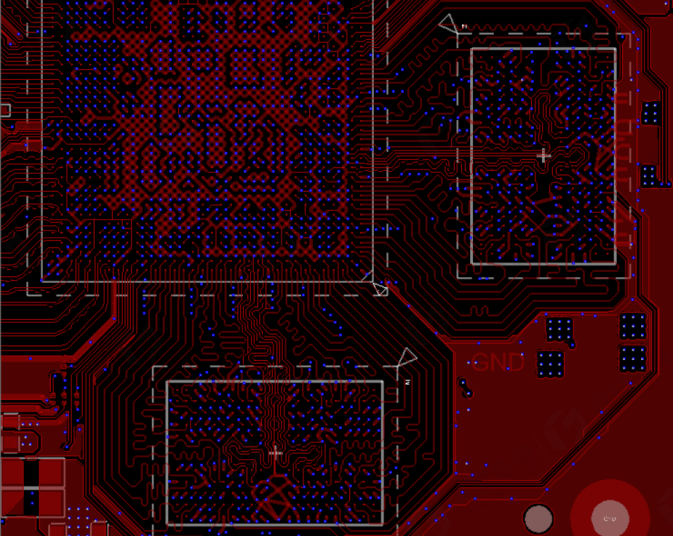

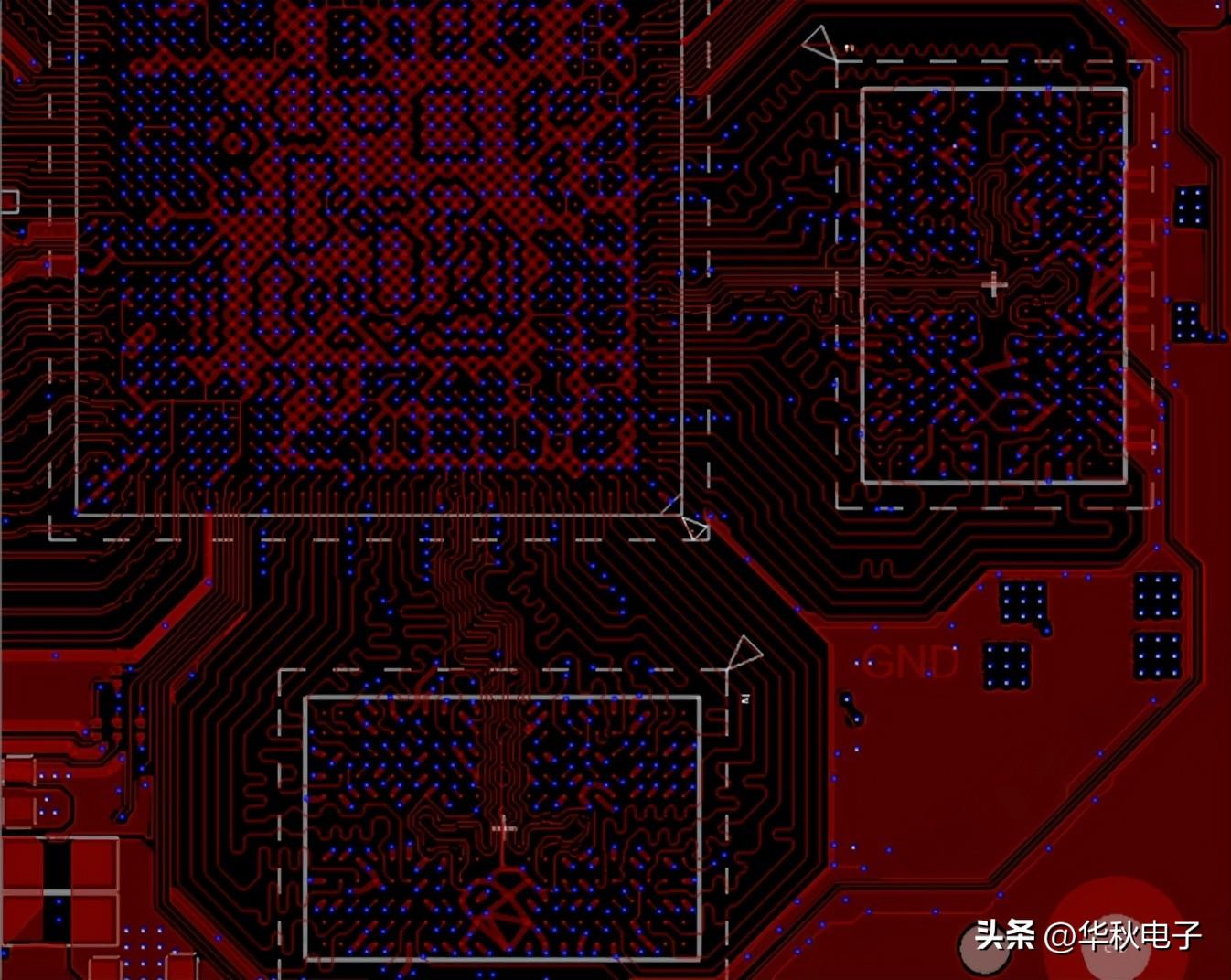

PCB设计空间足够的情况下,优先考虑留出DDR电路模块所需要的布局布线空间,拷贝瑞芯微原厂提供的DDR模板,包含芯片与DDR颗粒相对位置、电源滤波电容位置、铺铜间距等完全保持一致。 如下8张图(从左至右),分别为:L1-L8层DDR电路走线示意图。 如果自己设计PCB,请参考以下PCB设计建

2023-08-18 10:55:43 1702

1702

上期和大家聊的电源PCB设计的重要性,那本篇内容小编则给大家讲讲存储器的PCB设计建议,同样还是以大家最为熟悉的RK3588为例,详细介绍一下DDR模块电路的PCB设计要如何布局布线。 由于

2023-08-21 17:16:50 2037

2037

上期和大家聊的电源PCB设计的重要性,那本篇内容小编则给大家讲讲存储器的PCB设计建议,同样还是以大家最为熟悉的RK3588为例,详细介绍一下DDR模块电路的PCB设计要如何布局布线。 由于

2023-08-24 08:40:05 2815

2815

大家好,为了能够leveling成功,DDR3的布线约束需要规定到每一片DRAM的CLK长度与DQS长度差值不能超过一定范围。但是根据6678或者6670开发板,其中关于DQS和CLK长度差的布线

2019-01-02 15:21:58

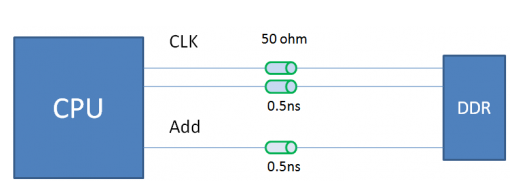

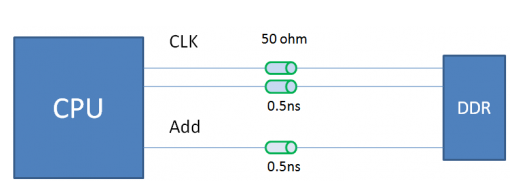

约束来进行布线。所有的DDR差分时钟信号都必须在关键平面上走线,尽量避免层到层的转换。线宽和差分间距需要参考DDR控制器的实施细则,信号线的单线阻抗应控制在50~60 Ω,差分阻抗控制在100~120

2015-01-15 10:39:37

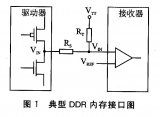

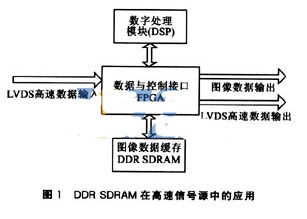

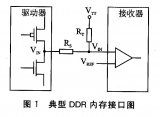

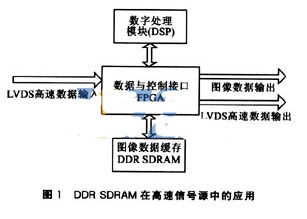

、锁相环等硬件资源。使用这些特性,可以更加容易地设计性能可靠的高速DDRSDRAM存储器控制器。 1 DDR SDRAM 在嵌入式系统中的应用 图1是DDR SDRAM在高速信号源系统中的应用实例

2018-12-18 10:17:15

主要是针对DDR2 667内存的设计。信号分组:DDR2的布线中习惯把信号分成若干组来进行设计,分成同组的信号具有相关或者相似的信号特性。时钟组:差分时钟信号,每一对信号都是同频同相的。ckp0

2011-10-27 14:53:32

共享交流一下,DDR3布线技巧

2016-01-08 08:17:53

这篇帖子跟大家一起来讨论下DDR3布线的那些事:DDR3的设计有着严格等长要求,归结起来分为两类(以64位的DDR3为例): 数据 (DQ,DQS,DQM):组内等长,误差控制在20MIL以内,组间

2016-10-28 10:25:21

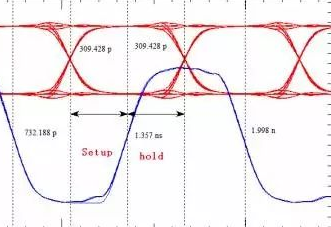

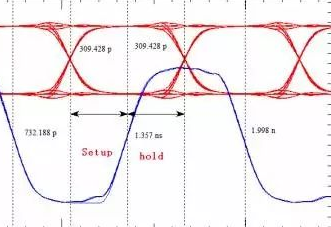

了极大的挑战。 本文主要使用了Cadence公司的时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计,提升信号质量使其可靠性

2014-12-15 14:17:46

DDR2,DDR3等 因频率不同,可以会有不同的要求,就一般而言,DDR布线时,要将DDR的网络分成几个组:地址线,控制线,数据线,时钟等差分线。我的疑问是,在6层板中,需不需要将地址线与数据线分别

2015-11-04 13:40:02

DDR布线参考Hardware and Layout Design Considerations for DDR Memory InterfacesEmbedded systems

2009-11-19 10:08:48

DDR-Topology DDR布线通常是一款硬件产品设计中的一个重要的环节,也正是因为其重要性,网络上也有大把的人在探讨DDR布线规则,有很多同行故弄玄虚,把DDR布线说得很难,我在这里要

2019-05-31 07:52:36

的Layout也就成为了一个十分关键的问题,很多时候,DDR的布线直接影响着信号完整性。下面本文针对DDR的Layout问题进行讨论。(Micron观点)[/url]信号引脚说明VSS为数字地,VSSQ为信号

2012-12-29 19:20:36

低于125MHz),根本上还是要从布线上改善。最好用IBIS模型做一下信号完整性分析。 http://processors.wiki.ti.com/index.php/Main_PageThink

2020-08-14 08:59:56

上期和大家聊的电源PCB设计的重要性,那本篇内容小编则给大家讲讲存储器的PCB设计建议,同样还是以大家最为熟悉的RK3588为例,详细介绍一下DDR模块电路的PCB设计要如何布局布线。

由于

2023-08-16 15:15:53

嵌入式Linux驱动开发(一)DDR内存DDRUARTI2CSPIDDR内存RAM: 随机存储器,可以随时进行读写操作,速度很快,掉电以后数据会丢失。比如内存条、 SRAM、 SDRAM、 DDR

2021-12-16 07:10:10

的[A13-A0],还是用AM3892的DDR_A[13:0]接到两片DDR3芯片的[A13-A0]?

(2)此外能讲述一下DDR3的布线规则吗? AM3892 能否 将 开发板的8片小容量 DDR3换成

2018-06-21 11:19:34

摘要本文档旨在介绍如何让所有设计人员都能简单方便地实现 AM64x\\\\AM243x DDR 系统,并将要求提炼为一组布局和布线规则,使设计人员能够针对 TI 支持的拓扑成功实现稳健的设计。内容1

2023-04-14 17:03:27

请问 在TI 给出的 EVM 参考设计中 DDR 的走线都串入一个22欧姆的电阻,按照SI 的理论这个电阻是保证匹配减少过冲的,在POWER PC 及MIPS 架构的CPU DDR布线中不需要增加这个电阻 ,请问这个电阻在TI ARM 的CPU 中一定需要吗?

2018-05-15 09:35:28

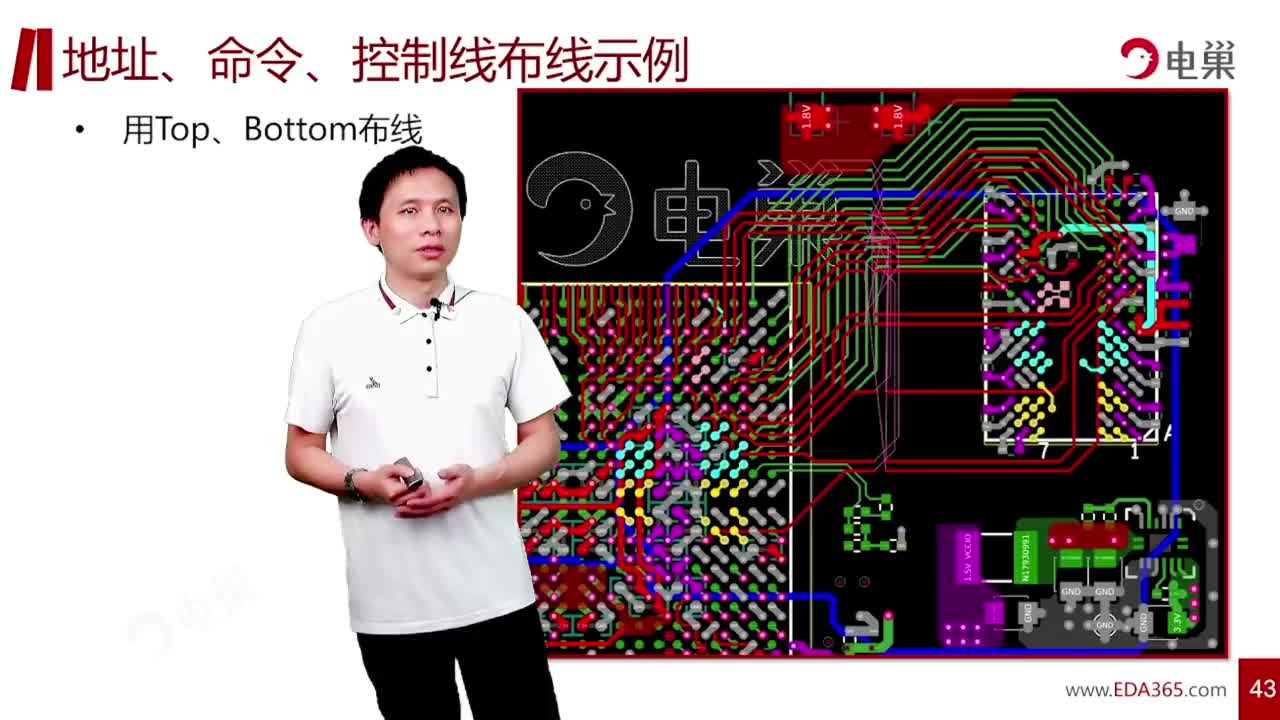

,从DDR一代到DDR四代,全面的去告诉大家应该如何去处理DDR的设计。直播大纲:1、DDR原理信号分析2、DDR布局思路解析(1/2/4片)3、DDR布线思路解析(1/2/4片)4、DDR信号时序

2018-10-10 11:49:20

最近要自己画DM6437的板子,以前师兄画的第一版DDR2的部分有问题,没有找出来中间哪里有问题,所以在这里请教一下DDR2布线有什么要求,如果自己检查哪里有问题一般从哪几方面开始?

2018-05-25 02:49:17

,DDR5 CAC信号的ODT闪亮登场!我猜最激动还是Layout攻城狮:DDR5的CAC信号有了ODT功能,PCB布线约束可以放宽松了吗?毕竟,哪里信号质量差就可以端接哪里,So easy。带着这个

2022-12-28 14:47:13

多年前,无线时代(Beamsky)发布了一篇文章关于DDR布线指导的一篇文章,当时在网络上很受欢迎,有很多同行参与了转载。如今看来,那篇文章写得不够好,逻辑性不强,可操作性也不强。在近几年的硬件产品

2022-08-11 09:07:02

本期讲解的是高速PCB设计中DDR布线要求及绕等长要求。布线要求数据信号组:以地平面为参考,给信号回路提供完整的地平面。特征阻抗控制在50~60 Ω。线宽要求参考实施细则。与其他非DDR信号间距至少

2017-10-16 15:30:56

使用公式分析和理论分析两种方法,以实例证明公式的局限性和两种方法的利弊。本文最后还基于这些实例分析,给出了SDRAM和DDR SDRAM等布线的一般性原则。

2021-05-19 06:52:58

保持时间,同频同相,采样正确。等长只不过可以最简单地实现这个目的罢了。要定量分析线长,必须按照时钟模型公式计算。时钟同步电路的类型在后面有简单介绍,这里只要知道SDRAM是公共时钟同步,DDR是源同步

2010-03-18 15:33:07

1、Zynq MPSoC支持的DDR介绍自己做自己的嵌入式产品一般要选择合适的DDR,而这里开发板给的是4GB的UIMM的DDR4,也就是电脑上用的,所以用不了,只能自己挂载Component,这里

2022-04-19 17:56:03

相关的基础知识和设计及仿真技巧,本系列的大致安排如下图所示。 本系列共分四大部分,分别是基础理论介绍,布局布线规划介绍,设计及仿真分析以及后期的测试及调试上的一些案例介绍。这个是目前的一个规划,其中

2016-08-16 15:57:07

上期和大家聊的电源PCB设计的重要性,那本篇内容小编则给大家讲讲存储器的PCB设计建议,同样还是以大家最为熟悉的RK3588为例,详细介绍一下DDR模块电路的PCB设计要如何布局布线。

由于

2023-08-17 17:23:30

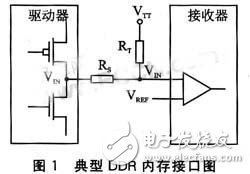

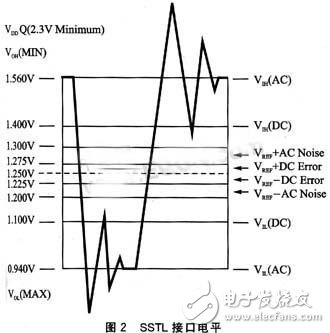

2.5V 的SSTL2 标准B. 关于DDR SDRAMDDR 存储芯片有多种形式,其封装有SOP/BGA/SLOT(插槽);但原理基本是相同的。1. 信号定义说明信号名功能备注CK/CK# 系统时钟

2012-09-17 21:15:33

DDR总线结构是什么嵌入式DDR总线的布线分析

2021-04-25 07:36:29

在DDR的PCB布线中提到,数据线可以分组等长,各组之间可以不等长,那怎样保证32位数据的时序呢?

2023-04-10 16:49:54

在DDR的PCB布线中提到,数据线可以分组等长,各组之间可以不等长,那怎样保证32位数据的时序呢?

2023-04-11 17:36:23

hello,各位大侠,请问如何测试嵌入式系统linux下的CPU及DDR性能,或者类似跑分软件。

2016-07-11 17:11:46

带有DDR的嵌入式系统主板中,设计PCB最难的部分莫过于DDR的走线设计。好的走线就等于有了好的信号完整性和好的时序匹配,总线在高速输入/输出数据过程中就不会出错,甚至能够有更好的抗串扰和EMC能力

2015-10-21 10:37:10

PCB布线设计的好坏直接影响到硬件电路能否正常工作或运行多快的速度。而在高速数字PCB设计中,DDR2是非常常见的高速缓存器件,且其工作频率很高本文将针对DDR2的PCB布线进行讨论。DDR

2016-12-26 16:56:05

DDR SDRAM在嵌入式系统中有哪些应用?DDR SDRAM的工作方式有哪几种?怎样去设计DDR SDRAM控制器?

2021-04-30 07:04:04

DDR3布线时CPU到DDR3的地址线长2037mil ,数据线长1613mil,这样会不会有问题

2019-06-05 03:34:28

本帖最后由 gk320830 于 2015-3-5 12:38 编辑

飞思卡尔的关于DDR内存布线设计资料,主要涉及了内存高频控制线的等长,阻抗匹配的等设计

2013-08-26 13:31:20

本期讲解的是高速PCB设计中,关于DDR布线知识。一.DDR信号功能与网络名了解DDR的各个信号功能与网络名。与DDR相比,DDR2/3最大差别多了功能OTD与OCD。重要信号线1.DQS信号

2017-10-27 10:48:26

嵌入式DDR接口原理及设计

有助于SoC设计取得成功的十条建议

DDR3等DRAM标准是由JEDEC开发的。这个组织已经为许多半导体器件制定过标准,而大多数DR

2010-03-13 11:36:47 88

88 SDRAM与DDR布线指南:ecos应用是与硬件平台无关的,虽然开发板没有涉及到SDRAM和DDR,不过,在某些高端平台上使用ecos可能会遇到内存布线问题,为了完整叙述,这里一并给出说明。 很

2010-03-18 15:29:08 0

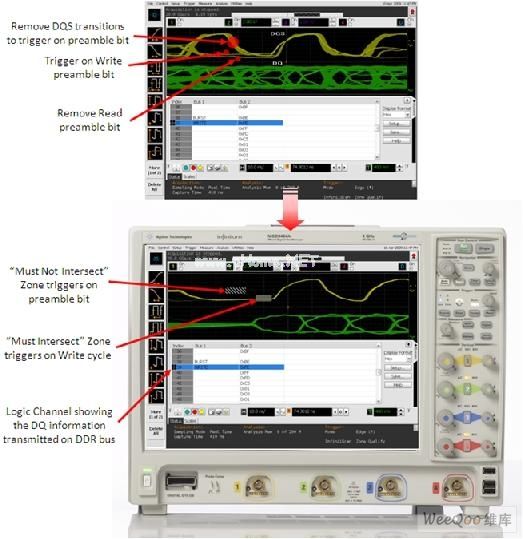

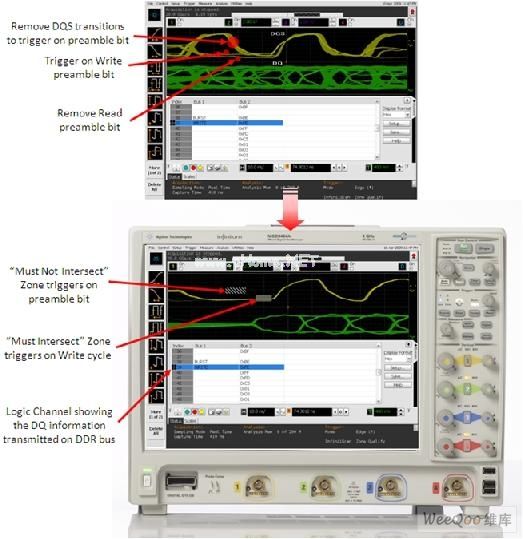

0 不只计算机存储器系统一直需要更大、更快、功率更低、物理尺寸更小的存储器,嵌入式系统应用也有类似的要求。本应用指南介绍了逻辑分析仪在检验DDR, DDR2 和DDR3 SDRAM 命令和

2010-08-06 08:29:49 81

81 用高带宽混合信号示波器进行DDR验证和调试的技巧

DDR存储器,也称双倍数据率同步动态随机存储器,常用于高级嵌入式电路系统的设计,包括计算机、交通运

2010-03-02 11:08:48 929

929

SDRAM, DDR, DDR2, DDR3 是RAM 技术发展的不同阶段, 对于嵌入式系统来说, SDRAM 常用在低端, 对速率要求不高的场合, 而在DDR/DDR2/DDR3 中,目前基本上已经以DDR2 为主导,相信不久DDR3 将全面取代

2012-01-16 14:53:01 0

0 研究了MPC8379E处理器的相关资料和DDR2的特性,以及它们之间PCB布线的规则和仿真设计。由于MPC8379E和DDR2都具有相当高的工作频率,所以他们之间的走线必须满足高速PCB布线规则,还要结

2013-03-12 15:22:26 80

80 PCB的DDR布局布线规则与实例教程说明

2015-11-13 16:13:47 0

0 介绍DDR的起源和发展历史,发展趋势,DDR的布局,参数含义。

2016-05-13 11:28:05 5

5 本文首先列出了DDR2布线中面临的困难,接着系统的讲述了DDR2电路板设计的具体方法,最后给出个人对本次电路设计的一些思考。

2017-09-19 11:27:21 22

22 DDR2_DDR3_SDRAM,PCB布线规则指导

2017-10-31 10:06:48 79

79 随着高速处理器的不断发展,嵌入式系统应用的领域越来越广泛,数字信号处理的规模也越来越大,系统中RAM规模不断增加。现场可编程门阵列(FPGA)已广泛应用于嵌入式系统中。现在很多FPGA都提供了针对

2017-11-24 16:00:22 4671

4671

DDR布线在PCB设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,线长匹配又是一个重要的环节。我们来回顾一下,DDR布线,线长匹配的基本原则是:地址,控制

2017-11-28 11:34:58 0

0 本文通过介绍信号完整性理论,对串扰和反射的成因进行探讨。利用Cadence公司的软件SpecctraQuest,以基于ARM11架构的S3C6410为主处理器嵌入式系统为载体进行信号完整性仿真分析

2017-12-01 17:16:01 1651

1651

DRAM (动态随机访问存储器)对设计人员特别具有吸引力,因为它提供了广泛的性能,用于各种计算机和嵌入式系统的存储系统设计中。本文概括阐述了DRAM 的概念,及介绍了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2018-06-07 22:10:00 95076

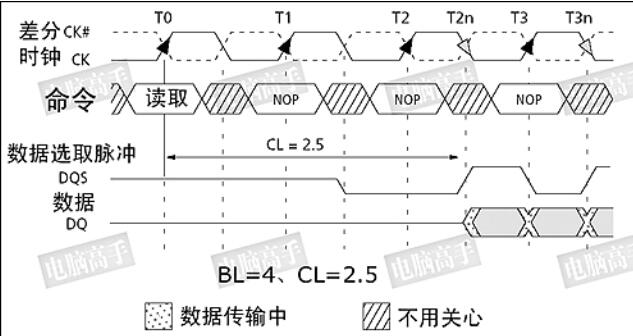

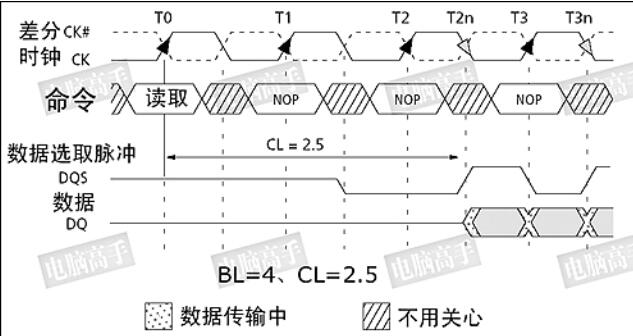

95076 Random Access Memory的缩写,即同步动态随机存取存储器。本文首先介绍了DDR工作原理及结构图,其次阐述了DDR DQS信号的处理,具体的跟随小编一起来了解一下。

2018-05-23 16:07:19 55912

55912

很多嵌入式系统,特别是应用于图像处理与高速数据采集等场合的嵌入式系统,都需要高速缓存大量的数据。DDR(Double Data Rate,双数据速率)SDRAM由于其速度快、容量大,而且价格便宜

2019-07-02 08:03:00 5010

5010

DRAM (动态随机访问存储器)对设计人员特别具有吸引力,因为它提供了广泛的性能,用于各种计算机和嵌入式系统的存储系统设计中。本文概括阐述了DRAM 的概念,及介绍了SDRAM、DDR SDRAM

2018-12-19 08:00:00 82

82 随着现代高速电路设计的发展,DDI腔.因其内存强大的预读取能力成为许多嵌入式系统的选择。然而, DDR2的仿真工作不仅繁琐耗时量大,对EMI的仿真也比较困难,给PCB设计也带来了大量的工作难点。文中

2019-03-04 08:00:00 0

0 在普通印制电路板的布线中由于信号是低速信号,所以在3W原则的基本布线规则下按照信号的流向将其连接起来,一般都不会出现问题。但是如果信号是100M以上的速度时,布线就很有讲究了。由于最近布过速度高达300M的DDR信号,所以仔细说明一下DDR信号的布线原则和技巧。

2019-03-24 10:00:06 8668

8668

在现代高速数字电路的设计过程中,工程师总是不可避免的会与DDR或者DDR2,SDRAM打交道。DDR的工作频率很高,因此,DDR的布线(或者Layout)也就成为了一个十分关键的问题,很多时候,DDR的布线直接影响着信号完整性。下面本文针对DDR的布线问题(Layout)进行讨论。

2019-06-08 14:35:00 5431

5431 Intel已经从服务器到消费级、从高端到低端彻底完成了DDR4内存的转换,AMD这边则直到今天才真正进入DDR4的时代,但首款产品却是面向嵌入式领域的R系列APU/CPU,开发代号“Merlin Falcon”。

2019-06-26 17:07:04 1196

1196 2014年,推出了第四代DDR内存(DDR4),降低了功耗,提高了数据传输速度和更高的芯片密度。 DDR4内存还具有改进的数据完整性,增加了对写入数据的循环冗余检查和片上奇偶校验检测。

2019-07-26 14:34:01 51736

51736 第一步,确定拓补结构(仅在多片DDR芯片时有用) 首先要确定DDR的拓补结构,一句话,DDR1/2采用星形结

2019-08-20 10:02:14 11561

11561 DDR布线在pcb设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的裕量。要保证系统的时序,线长又是一个重要的环节。

2020-01-14 14:46:10 1936

1936 本文档的主要内容详细介绍的是DDR和DDR2与DDR3的设计资料总结包括了:一、DDR的布线分析与设计,二、DDR电路的信号完整性,三、DDR Layout Guide,四、DDR设计建议,六、DDR design checklist,七、DDR信号完整性

2020-05-29 08:00:00 0

0 由于FPGA芯片是有关于DDR的设计指导文档,我司的PCB工程师和客户在投板前也反复确认了该DDR模块的设计是完全按照文档上面每一条细致的指导去布线的。

2021-03-17 15:00:27 4324

4324 采用蛇形设计、差分信号走线等长、等距设计,来尽可能减少电磁辐射(EMI)对主板其余部件和外界的影响。今天,编者就具体以某车机产品的高速 DDR 时钟信号设计为例,跟大家讲解 PCB 布线设计 EMC 整改的具体分析思路、方案设计。

2020-12-08 16:12:00 13

13 DDR4布线之allegro约束规则设置综述

2021-09-08 10:34:29 0

0 在PCB设计时我们在处理DDR部分的时候都会进行一个拓扑的选择,一般DDR有T点和Fly-by两种拓扑结构,那么这两种拓扑结构的应用场景和区别有哪些呢? T点拓扑结构: CPU出来的信号线经过一个

2022-11-27 07:40:01 2423

2423 上期和大家聊的电源PCB设计的重要性,那本篇内容小编则给大家讲讲存储器的PCB设计建议,同样还是以大家最为熟悉的RK3588为例,详细介绍一下DDR模块电路的PCB设计要如何布局布线。 由于

2023-08-17 18:15:02 1870

1870

上期和大家聊的电源PCB设计的重要性,那本篇内容小编则给大家讲讲存储器的PCB设计建议,同样还是以大家最为熟悉的RK3588为例,详细介绍一下DDR模块电路的PCB设计要如何布局布线。由于

2023-08-18 08:09:43 1391

1391

PCB布线对模拟信号传输的影响如何分析,如何区分信号传输过程中引入的噪声是布线导致还是运放器件导致? PCB布线对模拟信号传输的影响是一项非常复杂的任务,需要考虑诸如电容、电感、阻抗、信号完整性

2023-10-31 14:34:18 1654

1654 SDRAM与DDR布线指南

2022-12-30 09:20:50 13

13 再谈DDR内存布线

2022-12-30 09:21:08 5

5 PCB的DDR4布线指南和PCB的架构改进

2023-12-07 15:15:58 4192

4192 如何解决高速信号的手工布线和自动布线之间的矛盾? 高速信号的手工布线和自动布线之间存在矛盾主要是因为高速信号传输需要考虑到许多影响因素,包括信号完整性、时序约束、电磁干扰等。手工布线和自动布线在

2023-11-24 14:38:18 1340

1340 电子发烧友网站提供《了解TI基于PCB布线规则的DDR时序规范.pdf》资料免费下载

2024-10-15 11:47:01 3

3 电子发烧友网站提供《在DSP上实现DDR2 PCB布局布线.pdf》资料免费下载

2024-10-15 09:16:49 3

3

电子发烧友App

电子发烧友App

评论