在三天前SpinalHDL1.8.0正式上线,在这次更新中增加了Scala代码和生成的RTL代码之间的对照功能,也就是说我们可以在生成的RTL代码中看到是哪一行Scala生成的,这就为后续的代码调试增加了灵活性(虽然在调试SpinalHDL的时候也很少看对应的RTL吧)。

更新记录可以从这个网址看到

https://github.com/SpinalHDL/SpinalHDL/pull/985

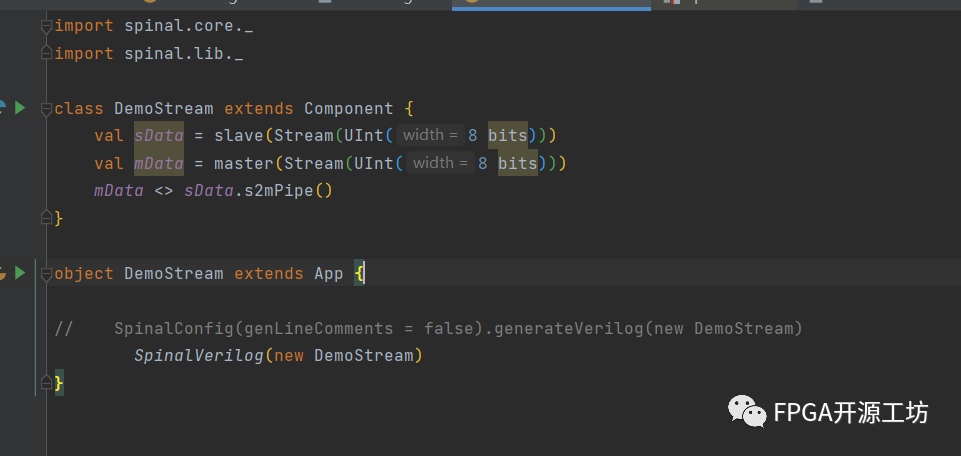

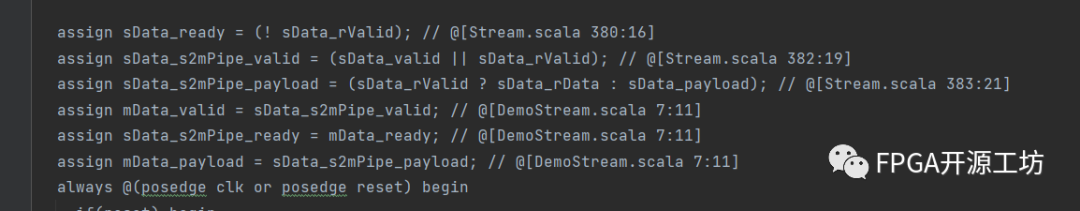

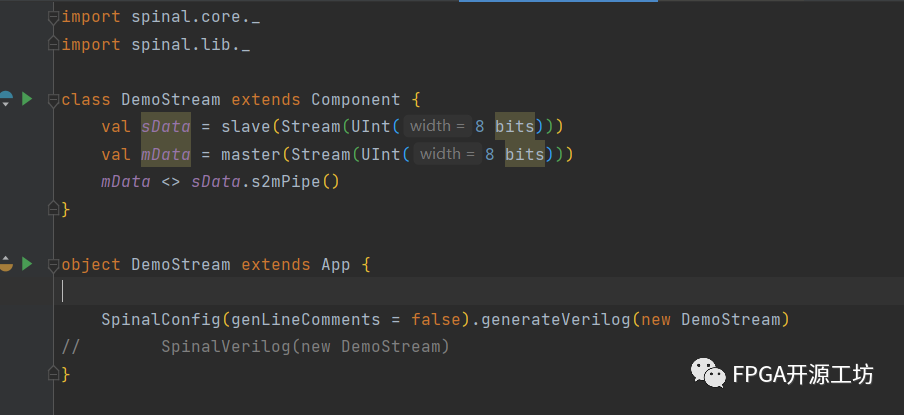

下图是Stream的打拍,在它生成的Verilog里面可以清楚的看到是哪一行Scala代码生成的。

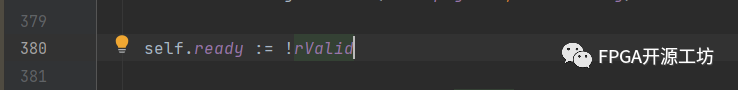

可以看到在生成的Verilog中标记了原始的scala文件和对应的代码行数,以sData_ready为例可以看到它是Stream.scala这个文件中第380行代码生成的。也就是下面这一行代码。

通过新更新的这个功能就能从生成的Verilog、VHDL等文件中追踪原始的Scala文件。

如果不想启用这个功能可以在配置中将genLineComments设置为false,这样就不会生成追踪的代码注释了。使用方法如下。

import spinal.core._ import spinal.lib._ class DemoStream extends Component { val sData = slave(Stream(UInt(8 bits))) val mData = master(Stream(UInt(8 bits))) mData <> sData.s2mPipe() } object DemoStream extends App { SpinalConfig(genLineComments = false).generateVerilog(new DemoStream) // SpinalVerilog(new DemoStream) }

审核编辑:汤梓红

-

RTL

+关注

关注

1文章

393浏览量

62382 -

代码

+关注

关注

30文章

4940浏览量

73119 -

scala

+关注

关注

0文章

42浏览量

6820

原文标题:从RTL追踪到Scala

文章出处:【微信号:FPGA开源工坊,微信公众号:FPGA开源工坊】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Scala入门到精通——第三十节 Scala脚本编程与结束语

SpinalHDL如何把名字从scala代码传递到产生的硬件中

从ESL到RTL,低功耗设计再下一城

scala语言主要应用领域详解

一文看懂scala和java的区别

从RTL追踪到Scala

从RTL追踪到Scala

评论