UltraRAM 是 UltraScale + 系列中最新的存储器模块,能实现高达 500Mb 的总片上存储容量,相当于赛灵思 28nm FPGA 片上存储器容量的 6 倍。

传统的 FPGA 和 SoC 包含的片上存储器以 block RAM 和分布式 RAM 的形式存在。由于器件能以更高数据速率处理更多数据,因此越发需要将数据缓冲或存储在靠近处理器的位置。

UltraScale+ 系列中的新产品是一款容量更大的称为 UltraRAM 的灵活存储器模块。UltraRAM 模块可级联在一起构成更大的片上存储器。

在设计中使用 UltraRAM 很简单,因为赛灵思提供了所有必要工具,利用这些工具可以在设计中集成功能强大的最新模块。

缓冲与存储的需求增加

UltraScale+ FPGA 和 MPSoC 能够传输和处理的数据比前一代器件多得多。灵活的级联功能使得 UltraRAM 模块能够采用多种配置——既可单独使用,也可在器件中将所有模块连 接在一起使用。这使得用户能够构建大小适合应用需求的存储器阵列,并省去一些 PCB 上的外部存储器 组件,例如 QDR SRAM。

UltraRAM 细节与特性

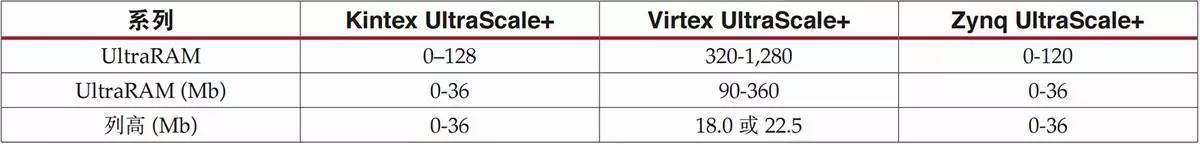

大多数 Kintex UltraScale+ 和 Zynq UltraScale+ 器件都包含一列 UltraRAM ;高端 Virtex UltraScale+ FPGA 则包含多达 5 列 UltraRAM。在 Kintex UltraScale+ 和 Zynq UltraScale+ 器件中,级联得到的 RAM 阵列可高达 36Mb,在 Virtex UltraScale+ 器件中可达到 22.5Mb。Virtex UltraScale+ 系列中,所有 UltraRAM 列都 可通过光纤路由连接在一起,在最大器件中可构成容量达 360Mb 的存储器阵列。

功耗降低

UltraRAM 提供各种内置功能以最大化功率效率,通常无需用户干预。这些功能包括 :

将设计中不用的 UltraRAM 断电

自动对不使用的流水线寄存器进行时钟门控

当 UltraRAM 长时间不使用时,使其进入休眠模式

在设计中使用 UltraRAM

UltraScale+ 产品组合使用赛灵思的 Vivado Design Suite。设计工具提供一系列代码模板,可帮助用户 成功锁定器件内的可用资源。有三种方法可以在 RTL 设计中使用 UltraRAM :

编写代码以调用存储器 ;

实例化器件原语 ;

使用最近添加的赛灵思参数化宏 (XPM)。

创建存储器阵列

UltraRAM 架构扩展性非常强,允许很多个 UltraRAM 模块高效地连接在一起,以构成深逻辑存储器, 仅使用很少甚至无需架构资源,而且访问时延相对较短。

寄存器和流水线化

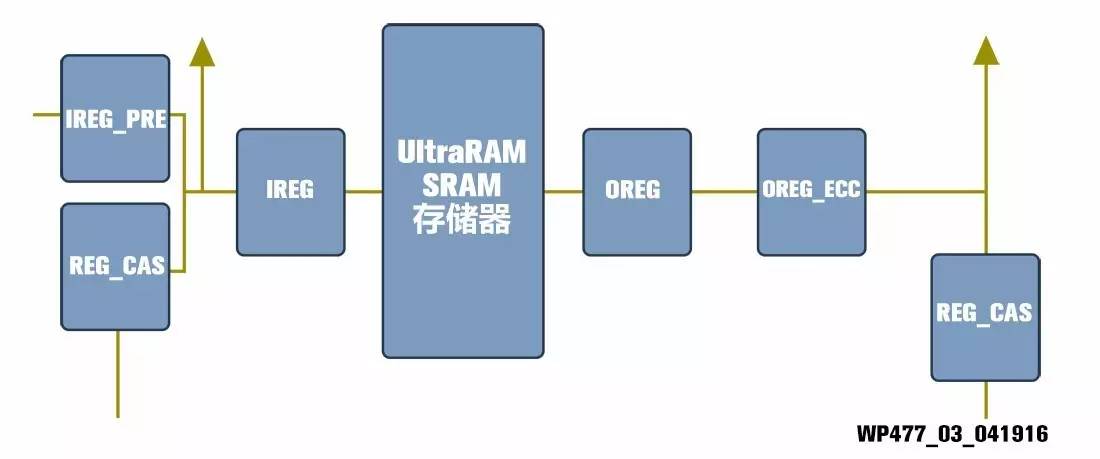

每个 UltraRAM 包含多个输入和输出寄存器,如图 3 所示,其中有一些是可选的,取决于配置情况和所 需的功能。

图3:UltraRAM 寄存器

迁移到 UltraRAM

在做这个步骤之前,用户一定要知道所选目标器件中不同存储器资源的数量。表 1 给出了不同 UltraScale+ 系列中 UltraRAM 的数量。在 Virtex UltraScale+ 器件中,可将所有 UltraRAM 连在一起,以构成容量高达 360Mb 的多列阵列 ;不过,也可实现更为常用的 10Mb-144Mb 范 围的多实例使用模型。

表1:UltraScale+ 产品组合中的 UltraRAM 资源

替代外部存储器组件

高达 360Mb 的 UltraRAM 几乎可配置成无数种方式,因此会有很多种使用模式。常见的 UltraRAM 使用模式是如果不实现在外部存储器中,则可以将存储器整合在 FPGA 或 MPSoC 中。

输入多播

每个 UltraRAM 端口都可确定级联模式中的事务处理是否属于局部存储器阵列。该功能可用来实现动态 的事务处理级写单播、多播和广播存储器结构。这种结构可以构成高效输出缓冲存储器开关的基础。

结论

每个设计都需要和使用这样或那样的存储器。将大容量、灵活的 UltraRAM 模块添加到 UltraScale+ 产品 系列后,为用户提供的片上存储器容量比以往任何器件或竞争器件都要大。由于模块可连接在一起构成 不同大小的存储器阵列,这样用户就能在设计中在需要的位置构建理想的存储器解决方案,消除了使用 外部 SRAM 组件所带来的功耗和电路板复杂性。

-

赛灵思

+关注

关注

33文章

1798浏览量

133641 -

嵌入式存储器

+关注

关注

0文章

24浏览量

12696

发布评论请先 登录

如何实现嵌入式ASIC和SoC的存储器设计?

嵌入式存储器的设计方法是什么?

FPGA中嵌入式存储器模块的设计

嵌入式存储器发展现状

嵌入式存储器内建自修复技术

嵌入式芯片的存储器映射

平板电脑如何选用嵌入式存储器

嵌入式存储器设计方案汇总

MRAM如何在嵌入式存储器建立桥头堡?

嵌入式硬件系统教程之嵌入式存储技术的详细资料说明

FPGA中嵌入式块存储器的设计

嵌入式存储器的巨大优势

嵌入式存储器的巨大优势

评论