IC集成电路可以说是20世纪后半年最重要的科技之一,我们现在使用的CPU、GPU以及其他芯片都受益于IC产业,50多年前Intel创始人之一的戈登·摩尔提出的摩尔定律成为指导IC发展的黄金定律。

但是在半导体工艺进入10nm之后,芯片制造难度越来越大,性能提升也越来越不明显了,摩尔定律也多次被人质疑了,IC产业会不会就此终结在10nm以下节点了?谁能回答这个问题?

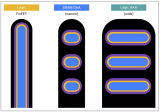

美国工程院院士、中科院外籍院士、IEEE会士、加州大学伯克利分校教授、前台积电CTO胡正明教授也许是最资格谈IC产业未来的人,因为他还是FinFET工艺、FD-SOI工艺的发明人,这两项半导体工艺是当今IC产业的支柱。

日前在概伦电子技术研讨会上,胡正明教授发表了《FinFET与未来IC技术》的演讲,介绍了他对IC产业未来的看法,他认为IC产业还能再发展100年,对于IC产业前景还是很乐观的。

根据胡教授所说,IC产业之所以还能继续发展是因为两个因素,一是因为硅是地球上含量第二多的元素,几乎取之不尽。

大家都说芯片是沙子做的,这话虽然是调侃,但确实有道理,储量丰富是保证硅基半导体成本降低的重要因素,目前也有非硅基的半导体材料,比如氮化镓、砷化镓、磷化铟等等,但是他们的成本不便宜,制造工艺也没有现在的硅基半导体成熟,主要用于特殊市场。

胡正明教授提出的第二个因素则是关于芯片功耗,他认为芯片功耗还能再降低1000倍。换句话说,胡正明教授也是同意摩尔定律终结的,芯片性能可能不会有大规模提升了,但是能效方面还大有可为,功耗还有足够多的降低空间。

胡正明教授有关芯片功耗降低1000倍的说法也不是第一次提起了,过去两年中他在不同的场合也多次表达过类似的说法,去年接受中国电子报采访时就有过表态

“集成电路的发展路径并不一定非要把线宽越做越小,现在存储器已经朝三维方向发展了。当然我们希望把它做得更小,可是我们也可以采取其他方法推进集成电路技术的发展,比如减少芯片的能耗。这个方向芯片还有1000倍的能耗可以降低。线宽的微缩总是有一个极限的,到了某种程度,就没有经济效应,驱动人们把这条路径继续走下去。但是我们并不一定非要一条路走到黑,我们也可以转换一个思路,同样可能实现我们想要达到的目的。”——胡正明

-

IC

+关注

关注

36文章

6465浏览量

186295 -

摩尔定律

+关注

关注

4文章

640浏览量

81144

发布评论请先 登录

沐曦股份参与编撰的超节点技术体系白皮书正式发布

芯片制造中硅片的表面抛光加工工艺介绍

工作流节点说明---工作流节点

蓝牙的Mesh会不会和ble功能有冲突

脉锐光电980nm波段ASE宽带光源产品介绍

0.2nm工艺节点的背后需要“背面供电”支撑

影响SerDes架构发展的三大关键趋势

【「AI芯片:科技探索与AGI愿景」阅读体验】+半导体芯片产业的前沿技术

浪涌多次作用后,TVS参数会不会漂移?

电子束检测:攻克5nm以下先进节点关键缺陷的利器

深度解析10BASE-T1S PLCA的多节点通信效率

如果光缆是双芯只接1芯会不会影响传输质量

三防漆与散热的关系:涂层会不会影响设备散热?

在WIN10下怎么搭建CY7C68013的开发环境?

跨越摩尔定律,新思科技掩膜方案凭何改写3nm以下芯片游戏规则

IC产业会不会终结在10nm以下节点

IC产业会不会终结在10nm以下节点

评论