时序分析基础

1. 时钟相关

时钟的时序特性主要分为抖动(Jitter)、偏移(Skew)、占空比失真(Duty Cycle DistorTIon)3点。对于低速设计,基本不用考虑这些特征;对于高速设计,由于时钟本身的原因造成的时序问题很普遍,因此必须关注。

1. 时钟抖动 (clock jitter)

理想的时钟信号应该是理想的方波,但是现实中的时钟的边沿变化不可能是瞬变的,它有个 从低到高 / 从高到低 的变化过程,如图1所示。

常见的抖动参数有3种:

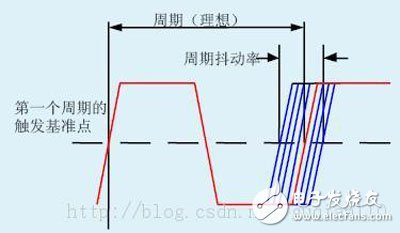

周期抖动(Period Jitter):

周期抖动率(Period Jitter)测量时钟输出传输偏离其理想位置的最大偏离。Period Jitter代表周期差抖动的上下边界。

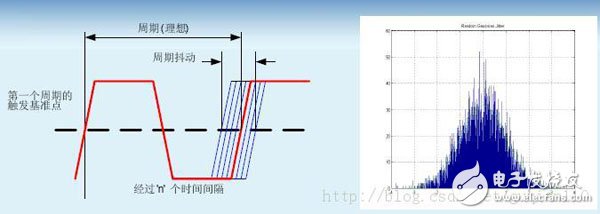

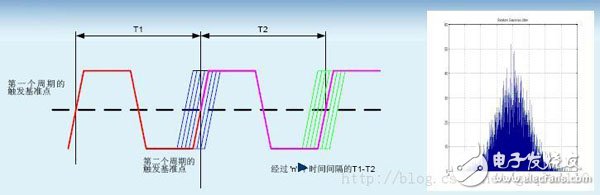

周期差抖动(cycle-to-cycle Jitter):

周期差抖动率(cycle-to-cycle jitter)是两个相邻周期的时间偏差。它总是小于周期抖动(period jitter)

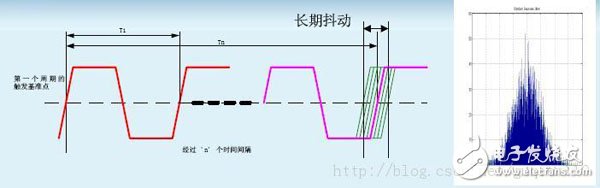

长期抖动(Long-term Jitter):

长期抖动率如下图(Long-Term Jitter)定义为一个时钟沿相对于基准周期时钟沿经过一段时间的延时之后,与其理想位置的偏离。此测量可以捕获锁相环低频周期变化(缓慢的,频率很低的)。长期抖动对图形、串行连接通讯系统、打印机和任何光栅扫描操作非常重要。

时钟抖动的原因就是噪声。时钟抖动是永远存在的,当其大到可以和时钟周期相比拟的时候,会影响到设计,这样的抖动是不可接受的。

2. 时钟偏斜 (clock skew)

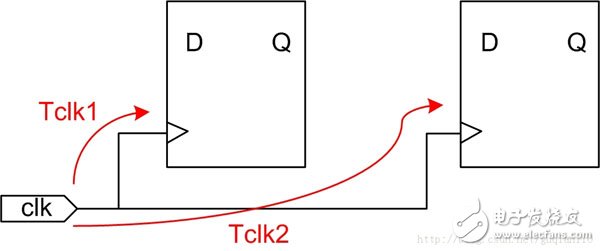

时钟信号要提供给整个电路的时序单元,所以时钟信号线非常长,并构成分布式的RC网路。它的延时与时钟线的长度、时序单元的负载电容、个数有关,所以产生所谓的时钟偏移。时钟偏移是指同一个时钟信号到达两个不同的寄存器之间的时间差值,根据差值可以分为正偏移和负偏移。

时钟偏移的计算公式: Tskew = Tclk2 - Tclk1

时钟偏移是永远存在的,当其大到一定程度会影响电路的时序。解决方法就是在FPGA的设计中让主要的时钟信号走全局时钟网络。该网络采用全铜工艺和树状结构,并设计了专用时钟缓冲和驱动网络,到所有的IO单元、CLB和块RAM的偏移非常小,可以忽略不计。

3. 占空比失真DCD (Duty Cycle DistorTIon)

即时钟不对称,时钟的脉冲宽度发生了变化。DCD会吞噬大量的时序裕量,造成数字信号的失真,使过零区间偏离理想的位置。DCD通常是由信号的上升沿和下降沿之间时序不同而造成的。

2. 信号扇入/扇出 (fan-in/fan-out)

The number of circuits that can be fed input signals from an output device. 扇出,输出可从输出设备输入信号的电路的数量。

扇出(fan-out)是定义单个逻辑门能够驱动的数字信号输入最大量的术语。大多数TTL逻辑门能够为10个其他数字门或驱动器提供信号。因而,一个典型的TTL逻辑门有10个扇出信号。

在一些数字系统中,必须有一个单一的TTL逻辑门来驱动10个以上的其他门或驱动器。这种情况下,被称为缓冲器(buf)的驱动器可以用在TTL逻辑门与它必须驱动的多重驱动器之间。这种类型的缓冲器有25至30个扇出信号。逻辑反向器(也被称为非门)在大多数数字电路中能够辅助这一功能。

模块的扇出是指模块的直属下层模块的个数。一般认为,设计得好的系统平均扇出是3或4。一个模块的扇出数过大或过小都不理想,过大比过小更严重。一般认为扇出的上限不超过7。扇出过大意味着管理模块过于复杂,需要控制和协调过多的下级。解决的办法是适当增加中间层次。一个模块的扇入是指有多少个上级模块调用它。扇人越大,表示该模块被更多的上级模块共享。这当然是我们所希望的。但是不能为了获得高扇人而不惜代价,例如把彼此无关的功能凑在一起构成一个模块,虽然扇人数高了,但这样的模块内聚程度必然低。这是我们应避免的。

设计得好的系统,上层模块有较高的扇出,下层模块有较高的扇人。其结构图像清真寺的塔,上面尖,中间宽,下面小。

3. launch edge

时序分析起点(launch edge):第一级寄存器数据变化的时钟边沿,也是静态时序分析的起点。

4. latch edge

时序分析终点(latch edge):数据锁存的时钟边沿,也是静态时序分析的终点。

-

时序

+关注

关注

5文章

403浏览量

38629 -

时序分析

+关注

关注

2文章

128浏览量

24152

发布评论请先 登录

Chroma 80611 电源时序/安规综合分析仪:电器安全与性能的自动化验证专家

vivado时序分析相关经验

改进wallance树乘法器优化方法

EDA是什么,有哪些方面

普源示波器MSO5074在嵌入式系统联合调试中的高效实践

芯片前端设计中常用的软件和工具

是德DSOX4034A示波器I2C总线信号分析

高分辨率示波器的功能与作用:以麦科信MHO6为例

集成电路设计中静态时序分析介绍

使用机器学习改善库特征提取的质量和运行时间

时序分析基础

时序分析基础

评论