物理层是OSI分层结构体系中最基础的一层,它建立在通信媒体的基础上,实现系统和通信媒体的物理接口。物理层为数据链路实体之间进行透明传输,为建立、保持和拆除计算机和网络之间的物理连接提供服务。

物理层的故障主要表现在设备的物理连接方式是否恰当,利用线缆测试仪检查各芯线的连接线路是否正确,并检查MODEM、CSU/DSU等设备的配置及操作是否正确。确定路由器端口物理连接是否完好的最佳方法是使用Show interface命令,检查每个端口的状态,解释屏幕输出信息,查看端口状态、协议建立状态等。

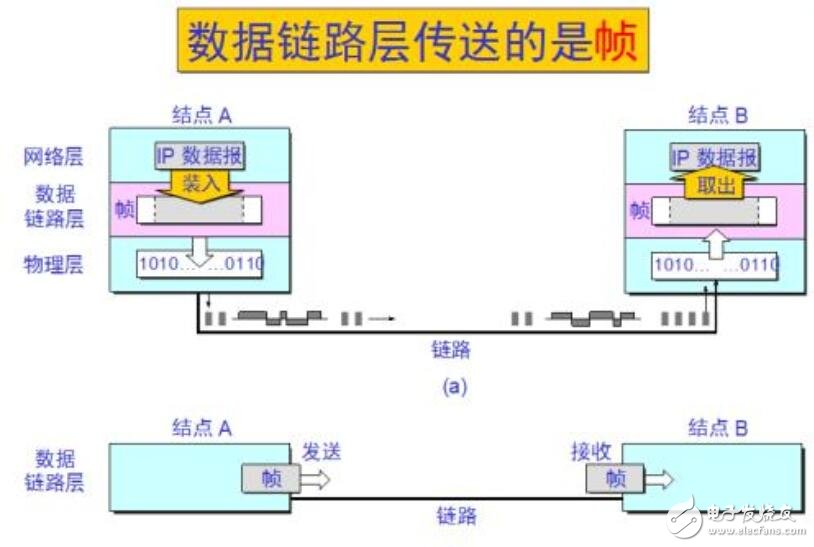

数据链路层的主要任务是使网络层无需了解物理层的特征而获得可靠的传输。数据链路层将通过链路层的数据进行打包和解包、差错检测和校正,并协调共享介质。

查找和排除数据链路层的故障,需要查看路由器的配置,检查连接端口的共享同一数据链路层的封装情况。每对接口要和与其通信的其他设备有相同的封装,这可通过Route命令来测试路由路径是否正确,或者使用Show命令查看相应接口的封装情况。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

数据链路层

+关注

关注

0文章

63浏览量

12440

发布评论请先 登录

相关推荐

热点推荐

ADMV9613:60GHz毫米波短数据链路解决方案

ADMV9613:60GHz毫米波短数据链路解决方案 在电子工程师的日常工作中,寻找高性能、小尺寸的无线连接解决方案是一项持续的挑战。今天,我们就来深入了解一款名为ADMV9613的产品,它为

ADMV9623:60GHz毫米波短数据链路解决方案

ADMV9623:60GHz毫米波短数据链路解决方案 在当今的电子科技领域,毫米波技术凭借其高速数据传输和低延迟的特性,在工业和医疗等众多领域展现出巨大的应用潜力。今天,我们就来深入了解一款名为

ADMV9615:60 GHz无线数据链路的理想之选

ADMV9615:60 GHz无线数据链路的理想之选 在当今高速发展的科技时代,无线数据传输技术的需求日益增长。对于电子工程师而言,寻找一款性能卓越、易于集成的无线数据链路解决方案至关重要。今天

ADMV9611:60 GHz毫米波短数据链路解决方案

ADMV9611:60 GHz毫米波短数据链路解决方案 在电子工程师的设计工作中,寻找高性能、小尺寸的无线连接解决方案是一项持续的挑战。今天,我们来深入了解一款名为ADMV9611的产品,它为60

ADMV9625:60 GHz无线数据链路的理想之选

ADMV9625:60 GHz无线数据链路的理想之选 在当今的电子科技领域,高速、稳定的无线数据传输需求日益增长。60 GHz频段凭借其高带宽、低干扰等优势,成为了众多应用场景的热门选择

[EtherCAT] CoE协议与服务数据(SDO)和过程数据(PDO)

一、EtherCAT通信模型EtherCAT主从站间的数据通信在数据链路层分为3种方式:寄存器访问,邮箱模式访问(MailBox),Buffer模式访问(ProcessData)。邮箱模式和Buffe

![[EtherCAT] CoE协议与服务<b class='flag-5'>数据</b>(SDO)和过程<b class='flag-5'>数据</b>(PDO)](https://file1.elecfans.com/web3/M00/52/7C/wKgZPGnPa56AOOAmAANhL9yPdmI804.png)

探索TSB12LV32:高性能IEEE 1394a-2000链路层控制器

探索TSB12LV32:高性能IEEE 1394a-2000链路层控制器 在电子设备不断发展的今天,高性能的链路层控制器对于计算机外设和消费类音视频电子设备的稳定运行至关重要。德州仪器

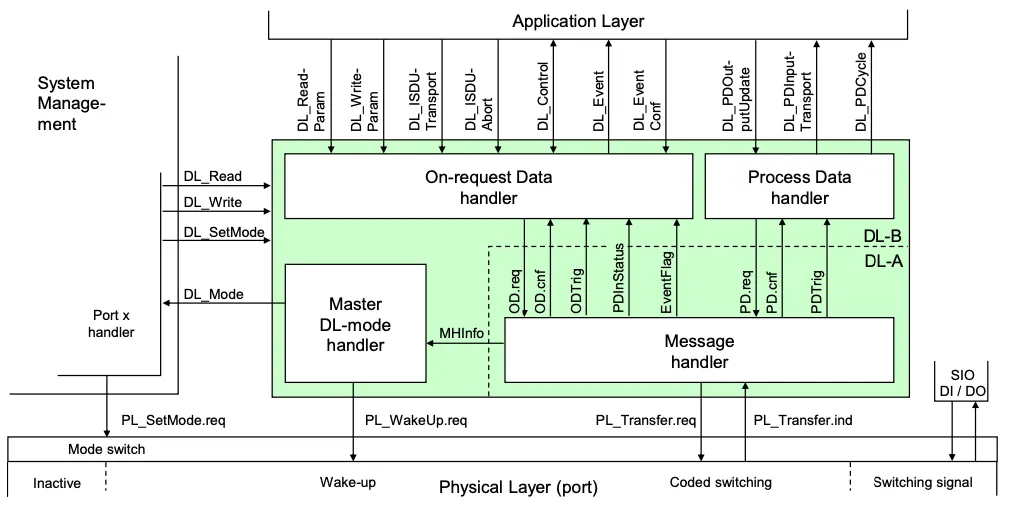

IO-Link规范解读(五):数据链路层解析

前言 本篇就来讲讲IO-Link的数据链路层。 01 链路层总览 数据链路层(Data Link Layers)在整个IO-Link协议栈起到承上启下的作用,通过物理链路在主从站之间传递 消息,其

请问rt-thread有没有链路层通信的方法?

与开发板通信上。

我尝试过使用UDP广播,但在IP地址为0.0.0.0,子网掩码0.0.0.0,网关为0.0.0.0无法通信上。

我也尝试了一下raw原始套接字,但也没有用。

在Linux中有一个sockaddr_ll结构体可以使用链路层通信,但rt-thread好像没有。

发表于 09-02 08:00

NVMe高速传输之摆脱XDMA设计23:UVM验证平台

Under Test,DUT)中剥离,以 PCIE 集成块接口作为 DUT 接口执行仿真。一方面,因为 PCIe 接口采用 PCIE 集成块作为物理层和数据链路层驱动,而 PCIe 物理层和数据链路层的仿真

发表于 08-26 09:49

FTTR-B主网关二层透传配置过程

二层透传(Layer 2 Transparent Transmission)指在数据链路层(OSI第二层)上,数据帧在传输过程中保持原始的二层信息(如MAC地址、VLAN标签等)不变,直接被转发的过程。

NVMe高速传输之摆脱XDMA设计17:PCIe加速模块设计

内部信号做进一步处理,如果需要应答,将应答事务通过axis完成方完成接口(axis_cc)发送给PCIE硬核。图1 PCIe加速模块系统框图

PCIe加速模块在系统中作为NVMe层到PCIe数据链路层

发表于 08-07 18:57

NVMe高速传输之摆脱XDMA设计之12:PCIe请求模块设计(上)

Cfg_mgmt接口发送给PCIE硬核,当配置请求的总线号不为0时,请求以PCIe配置请求TLP的格式从axis_rq接口发送到PCIE硬核,然后由硬核驱动数据链路层和物理层通过PCIe3.0X4接口

发表于 08-03 22:00

NVMe高速传输之摆脱XDMA设计18:UVM验证平台

Under Test,DUT)中剥离,以 PCIE 集成块接口作为 DUT 接口执行仿真。一方面,因为 PCIe 接口采用 PCIE 集成块作为物理层和数据链路层驱动,而 PCIe 物理层和数据链路层的仿真

发表于 07-31 16:39

nvme IP开发之PCIe上

,获取其它设备的响应。

PCIe层次结构

PCIe 总线是一种分层协议总线,采用数据包进行数据传输。数据包在收发过程中需要经过事务层、数据链路层和物理层三个层次的处理和转发。PCIe总

发表于 05-17 14:54

数据链路层的任务

数据链路层的任务

评论