如果嵌入式 IP 目录以及 AXI USB 2.0 器件 IP 对您来说比较陌生的话,此视频将向您详细地介绍这两者。通过本次培训您将学习到 AXI USB2.0器件的关键性能、配置选项以及基本架构,同时还包括有如何在大容量存储应用中使用AXI USB 2.0器件IP的典型应用案例。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

usb

+关注

关注

60文章

8372浏览量

281675 -

赛灵思

+关注

关注

33文章

1797浏览量

133147 -

IP

+关注

关注

5文章

1849浏览量

154909

发布评论请先 登录

相关推荐

热点推荐

使用AXI4接口IP核进行DDR读写测试

本章的实验任务是在 PL 端自定义一个 AXI4 接口的 IP 核,通过 AXI_HP 接口对 PS 端 DDR3 进行读写测试,读写的内存大小是 4K 字节。

Xilinx高性能NVMe Host控制器IP+PCIe 3.0软核控制器IP,纯逻辑实现,AXI4和AXI4-Stream DMA接口,支持PCIe 3.0和4.0

NVMe AXI4 Host Controller IP1介绍NVMe AXI4 Host Controller IP可以连接高速存储PCI

发表于 11-14 22:40

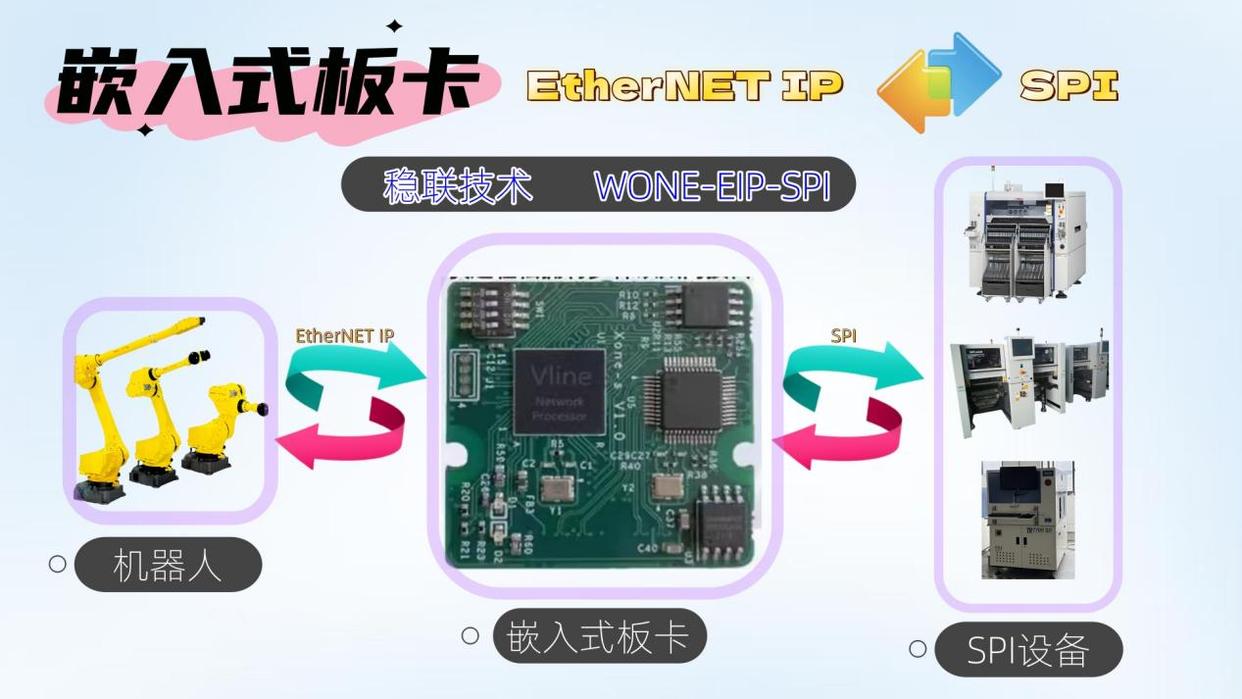

Ethernet ip转SPI嵌入式板卡-让机器人与单片机互相联动

发那科机器人通过EtherNet/IP主站与SPI嵌入式板卡联动,实现远程控制SPI设备与数据采集,涵盖硬件连接、IP配置、数据映射及通信验证,适用于机器人工作站集成SPI传感器/执行器的场景。

VDMA IP核简介

VDMA端口信号

S_AXI_LITE:PS端可以通过AXI_LITE协议对IP核进行控制;

S_AXIS_S2MM:视频流(AXI STREAM)输入到

发表于 10-28 06:14

基于E203的DMA ip的使用

1.BD设计

2.AXI DMA寄存器

编写SDK代码,需要根据xilinx的官方例程和dma ip使用手册进行寄存器的配置。

重要寄存器:

MM2S

S2MM

发表于 10-22 06:00

创飞芯40nm eNT嵌入式eFlash IP通过可靠性验证

珠海创飞芯科技有限公司在非易失性存储技术领域再获突破——基于40nm标准工艺平台开发的eNT嵌入式eFlash IP已通过可靠性验证!这一成果进一步展现了创飞芯科技有限公司在先进工艺节点上的技术实力与工程化能力。

一站式定制芯片及IP供应商灿芯半导体推出PCIe 4.0 PHY IP

2025年8月14日,一站式定制芯片及IP供应商——灿芯半导体(上海)股份有限公司(灿芯股份,688691)宣布推出基于28HKC+ 0.9V/1.8V平台的 PCIe 4.0 PHY IP 。该

MicroBlaze处理器嵌入式设计用户指南

*本指南内容涵盖了在嵌入式设计中使用 MicroBlaze 处理器、含存储器 IP 核的设计、IP integrator 中的复位和时钟拓扑结构。获取完整版《 MicroBlaze 处理器嵌入

如何使用AMD Vitis HLS创建HLS IP

本文逐步演示了如何使用 AMD Vitis HLS 来创建一个 HLS IP,通过 AXI4 接口从存储器读取数据、执行简单的数学运算,然后将数据写回存储器。接着会在 AMD Vivado Design Suite 设计中使用此 HLS

NVMe IP之AXI4总线分析

广泛应用 。随着时间的推移,AXI4的影响不断扩大。目前,由Xilinx提供的大部分IP接口都支持AXI4总线,使得系统中不同模块之间的互连更加高效。这也让基于这些IP的开发变得更加快

发表于 06-02 23:05

NVMe控制器IP设计之接口转换

这是NVMe控制器IP设计系列博客之一,其他的见本博客或csdn搜用户名:tiantianuser。相关视频见B站用户名:专注与守望。

接口转换模块负责完成AXI4接口与控制器内部的自定义接口之间

发表于 05-10 14:33

一文详解Video In to AXI4-Stream IP核

Video In to AXI4-Stream IP核用于将视频源(带有同步信号的时钟并行视频数据,即同步sync或消隐blank信号或者而后者皆有)转换成AXI4-Stream接口形式,实现了接口转换。该

ZYNQ基础---AXI DMA使用

Xilinx官方也提供有一些DMA的IP,通过调用API函数能够更加灵活地使用DMA。 1. AXI DMA的基本接口 axi dma IP的基本结构如下,主要分为三个部分,分别是控制

AXI USB 2.0器件IP及嵌入式IP目录介绍

AXI USB 2.0器件IP及嵌入式IP目录介绍

评论