PG080中文文档简介

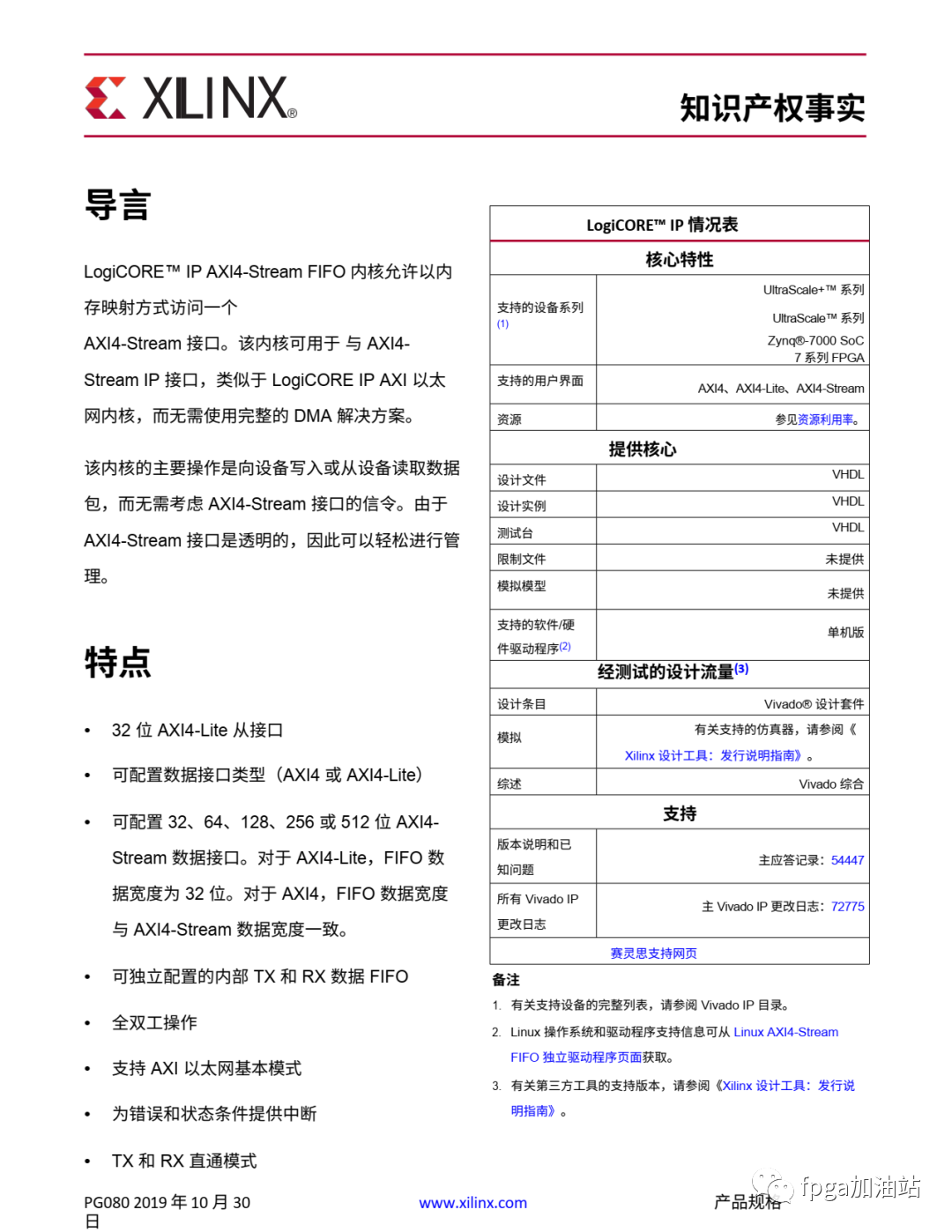

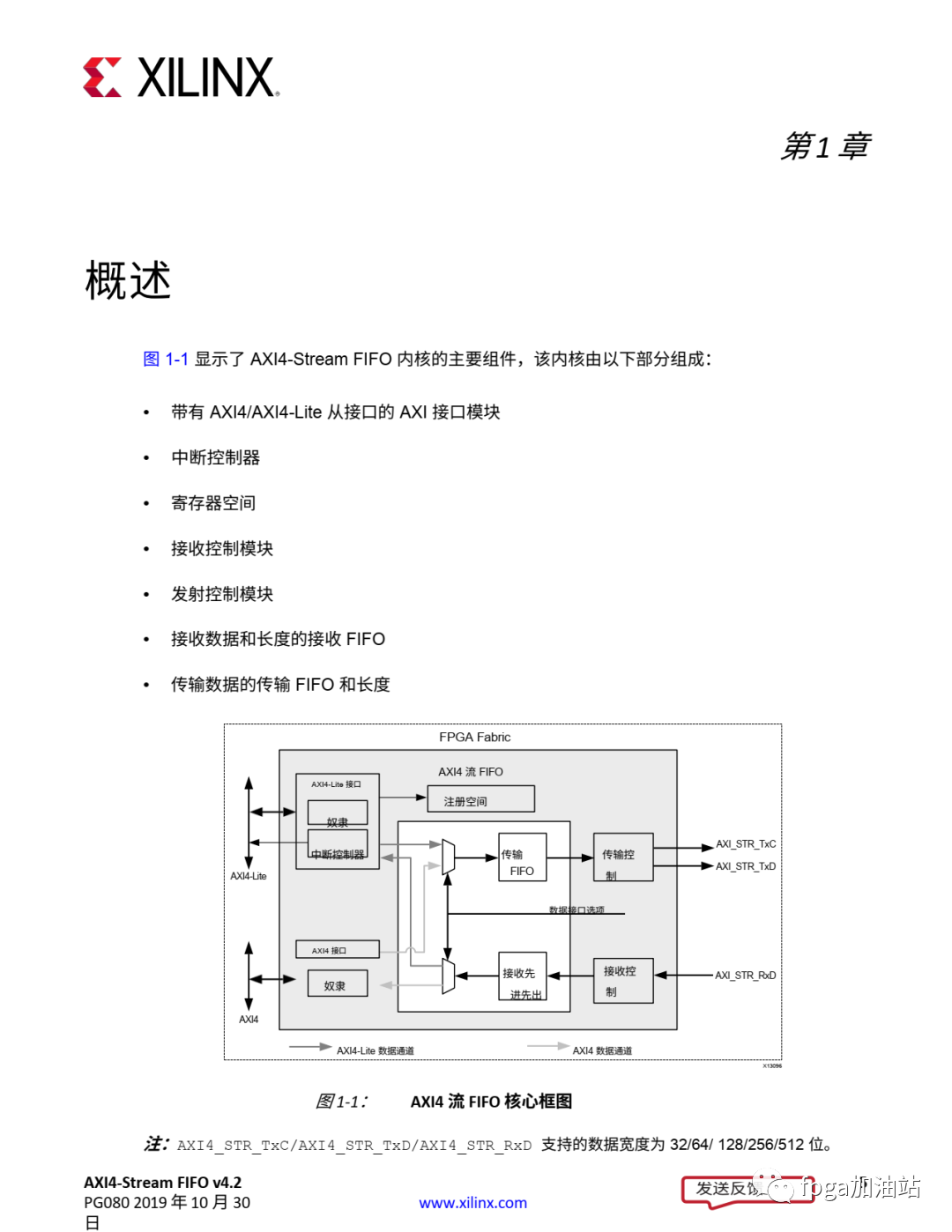

LogiCORE IP AXI4-Stream FIFO内核允许以内存映射方式访问一个AXI4-Stream接口。该内核可用于与AXI4-Stream IP接口,类似于LogiCORE IP AXI以太网内核,而无需使用完整的DMA解决方案。

该内核的主要操作是向设备写入或从设备读取数据包,而无需考虑AXI4-Stream接口的信令。由于AXI4-Stream接口是透明的,因此可以轻松进行管理。

协议说明

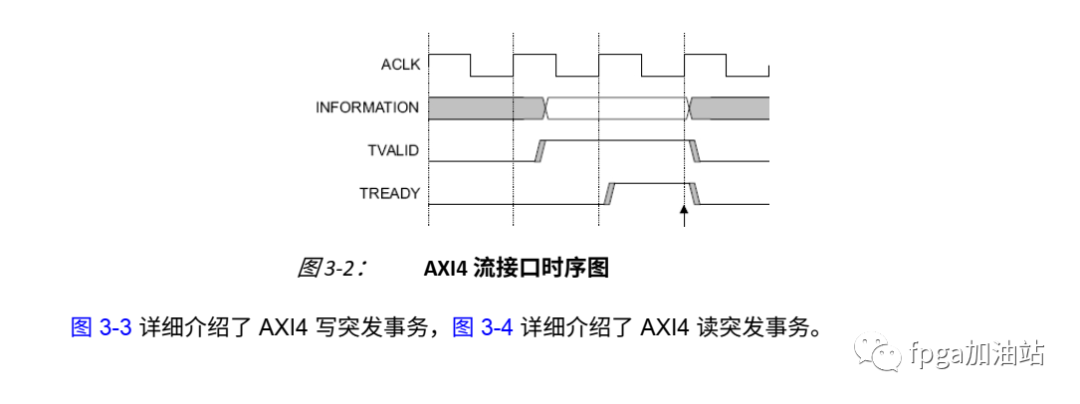

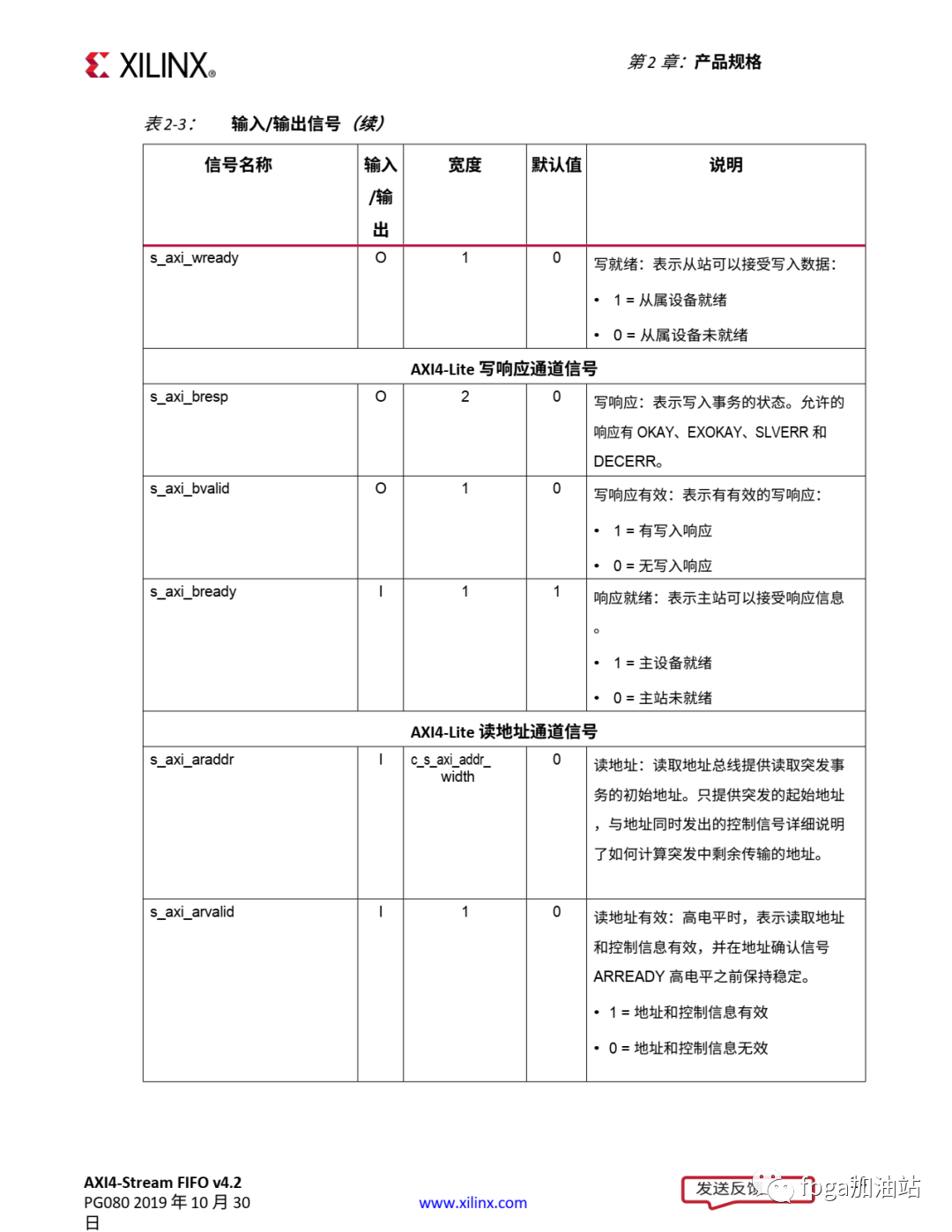

AXI4-Stream FIFO内核使用行业标准AMBA AXI4-Stream和AXI4协议规范。图3-2详细介绍了AXI4-Stream接口,其中INFORMATION表示除TVALID/TREADY以外的所有AXI4-Stream信号。

本节以 AXI 以太网内核为例,通过寄存器访问介绍 AXI4-Stream FIFO 内核的运行。

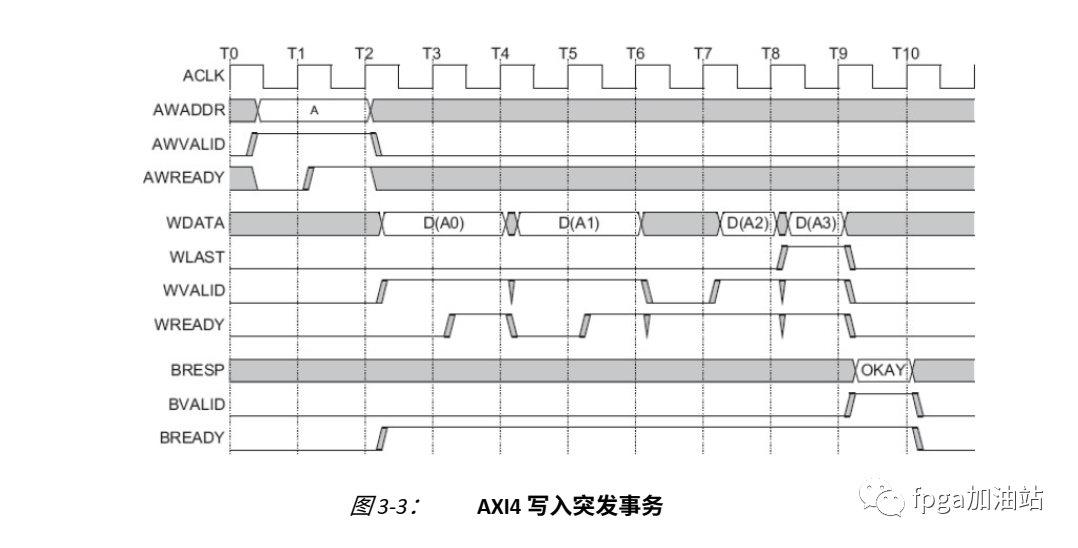

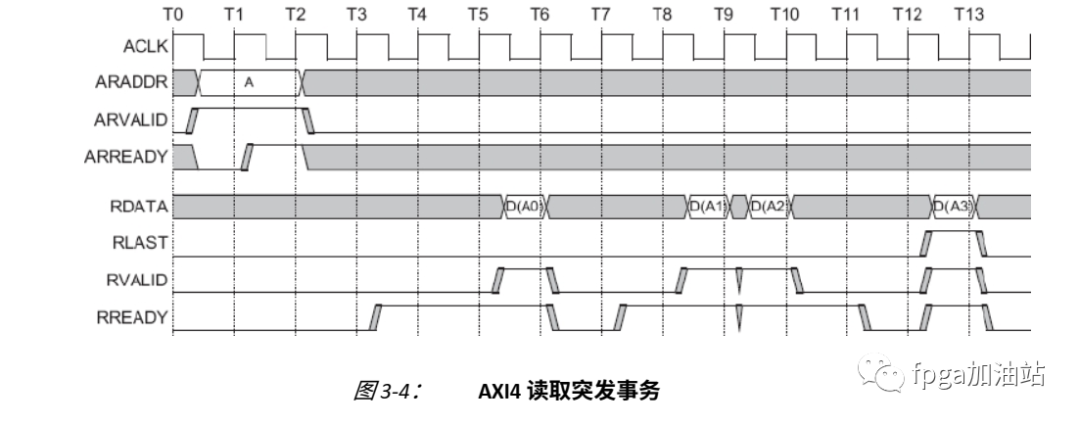

根据数据接口选项的不同,先进先出设备访问可使用 AXI4 或 AXI4-Lite。选择 AXI4-Lite 时,寄存器访问和 FIFO 访问由 AXI4-Lite 接口处理。选择 AXI4 时,寄存器访问由 AXI4-Lite 接口处理,FIFO 访问由 AXI4 接口处理。当数据接口选项为 AXI4 时,数据突发是可能的。

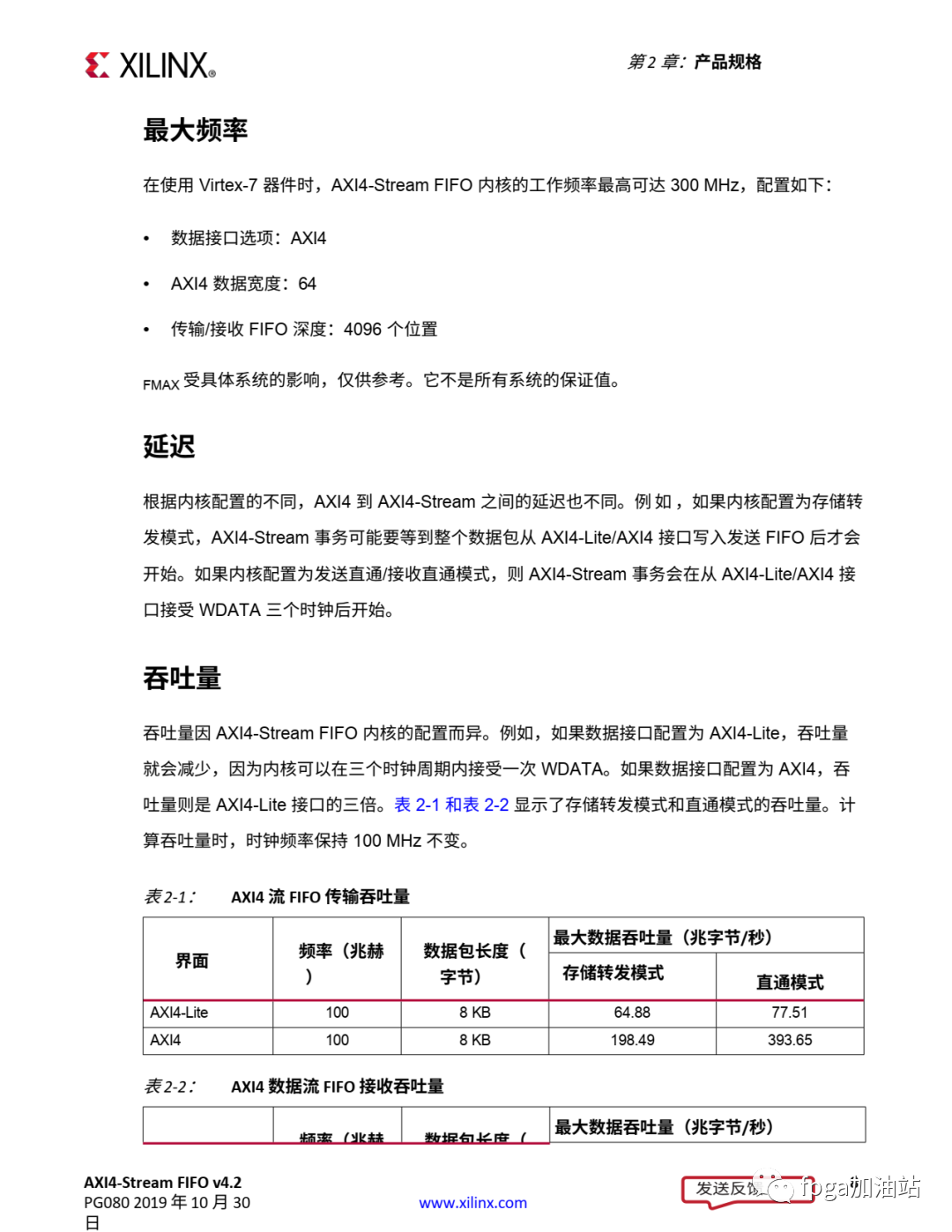

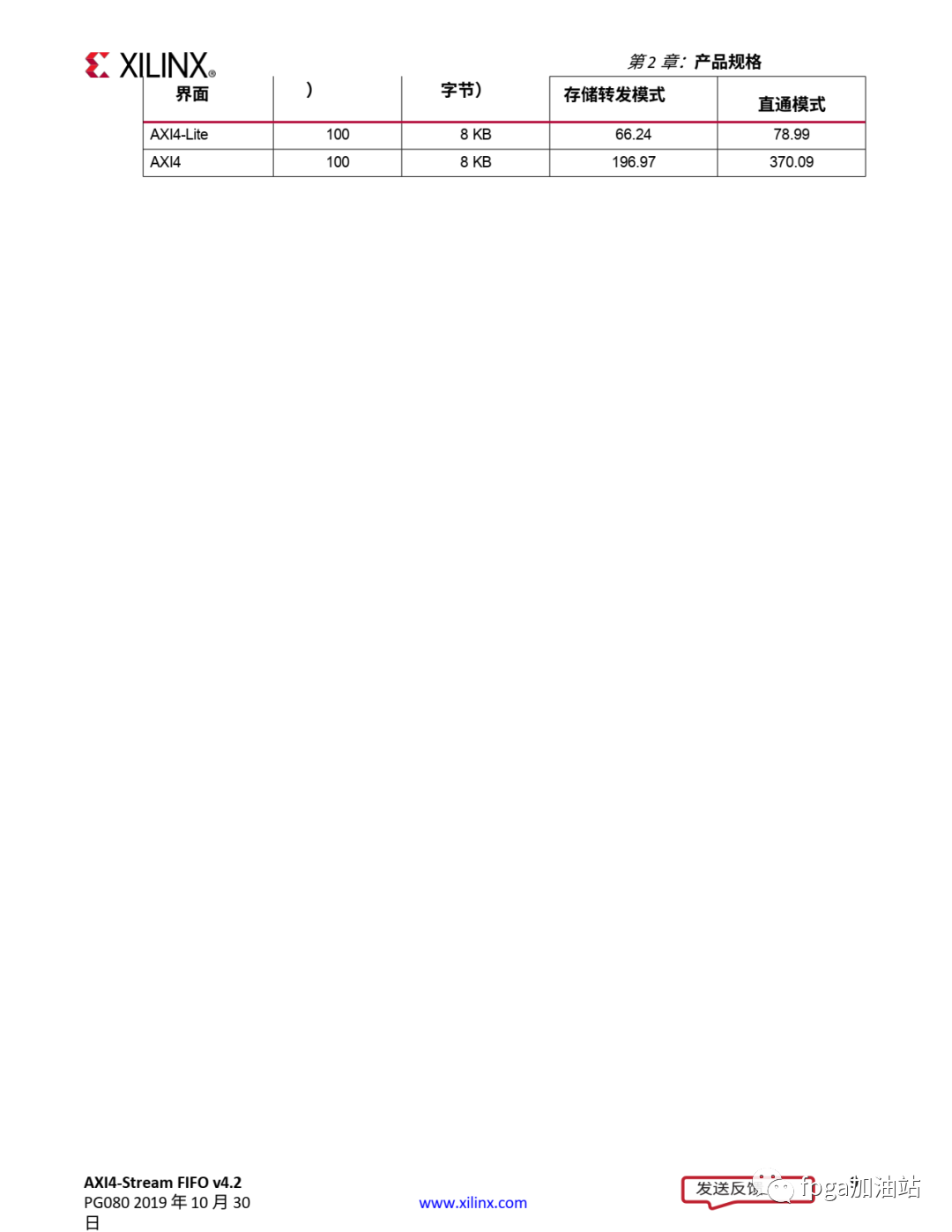

AXI4-Stream FIFO 支持两种数据包传输模式:存储转发模式和直通模式。

• 在存储转发模式下,数据包传输在以下情况下从 AXI4-Stream 接口开始: ° 当完整数据包写入 FIFO 时

° 数据包长度写入 TX 长度寄存器。

在这种模式下, FIFO 的大小必须足以容纳完整的数据包。

• 在直通模式下,当 FIFO 中有足够的数据时, AXI4-Stream 接口上就开始传输数据包。在这种模式下,先进先出存储器无需保存完整的数据包。不过,要确保 AXI4-Stream 接口不会运行不足。

部分翻译截图(上下滑动查看)

审核编辑:汤梓红

-

内核

+关注

关注

3文章

1309浏览量

39862 -

fifo

+关注

关注

3文章

369浏览量

43075 -

dma

+关注

关注

3文章

536浏览量

99070 -

AXI4

+关注

关注

0文章

18浏览量

8836

原文标题:中文文档PG080|AXI4-Stream FIFO

文章出处:【微信号:fpga加油站,微信公众号:fpga加油站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

有人有经验AXI4-Stream到视频输出IP核吗?

请问我对AXI4-Stream FIFO的理解不正确吗?

请问AXI4-Stream到Video核心的技巧有什么?

如何将AXI4-Stream与CH7301接口?

如何吧AXI4-stream时钟转换器tkeep设置为null?

axi4-stream互连问题如何解决

axi4-stream combiner问题的解决办法?

AXI-stream数据传输过程

AXI FIFO和AXI virtual FIFO这两个IP的使用方法

Xilinx的LogiCORE IP Video In to AXI4

AXI STREAM FIFO如何设置双时钟

关于AXI4-Stream协议总结分享

AXI4-Stream Video 协议和AXI_VDMA的IP核介绍

AXI4 、 AXI4-Lite 、AXI4-Stream接口

Video In to AXI4-Stream IP核知识介绍

LogiCORE IP AXI4-Stream FIFO内核解决方案

LogiCORE IP AXI4-Stream FIFO内核解决方案

评论