了解连接域特定目标设计平台如何使您能够创建具有DMA和DDR3内存支持的先进PCIe,千兆以太网设计。Spartan®-6 FPGA 连接功能套件是一款全面的开发和演示平台,可用于在多个市场领域内进行基于标准协议 - PCIe、以太网 - 的设计,实现低成本协议桥接,还能为 LVDS 通信提供更高效的替代设计。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

以太网

+关注

关注

41文章

5923浏览量

179523 -

赛灵思

+关注

关注

33文章

1797浏览量

133148 -

PCIe

+关注

关注

16文章

1420浏览量

87546

发布评论请先 登录

相关推荐

热点推荐

【PCIE715】青翼凌云科技基于复微青龙 JFMQL100TAI 的高性能智能异构计算平台 (完全兼容悟空开发板))

该平台的PL端具有1个FMC(HPC)接口,1路PCIe x4主机接口,支持1组64位DDR3 SDRAM大容量缓存、支持1路1000BAS

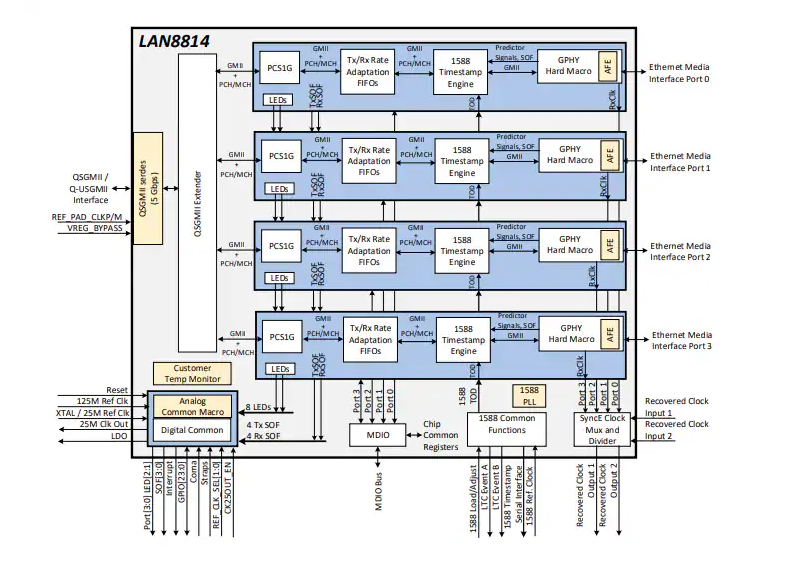

LAN8814 4端口千兆以太网收发器数据手册总结

),可通过标准的CAT-5、CAT-5e和CAT-6非屏蔽双绞线(UTP)电缆传输和接收数据。LAN8814支持行业标准四路串行千兆位介质独立接口 (QSGMII) 和四路通用串行千兆位介质独立接口 (Q-USGMII) 这些接

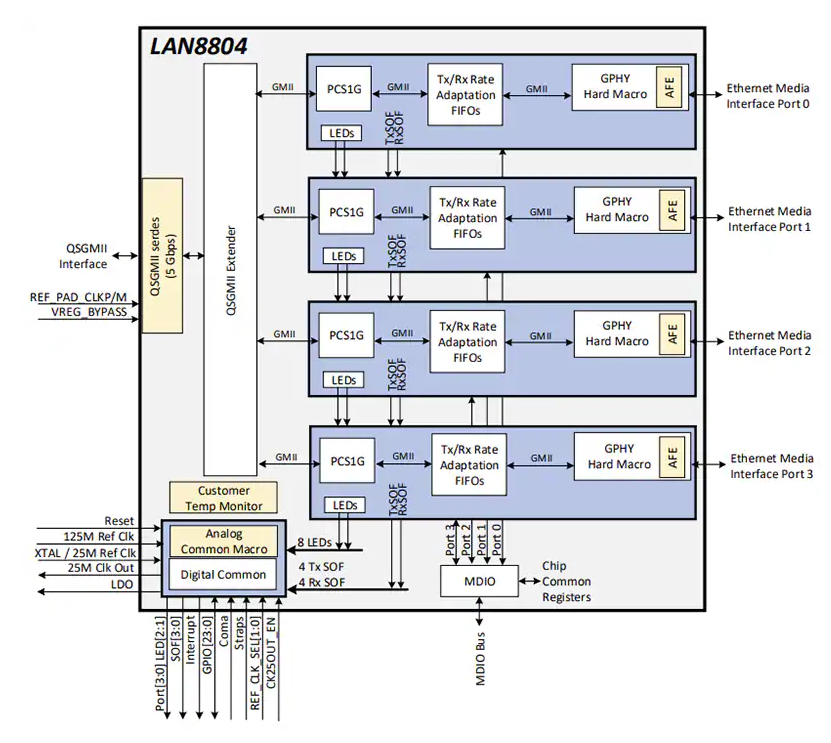

LAN8804四端口千兆以太网收发器技术解析

Microchip Technology LAN8804 4端口千兆位以太网收发器是低功耗、四端口、三速(10BASE-T/100BASE-TX/1000BASE-T)以太网物理层收发器(PHY

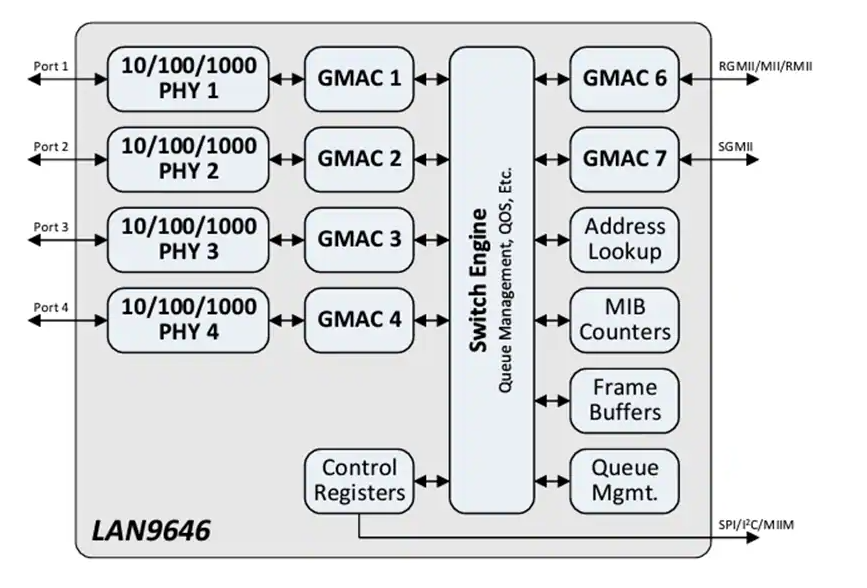

Microchip推出面向工业应用的灵活新型千兆以太网交换机系列 支持TSN/AVB与冗余功能

新一代 LAN9645xF和LAN9645xS 千兆以太网交换机具备高可配置性, 支持多端口与先进功能 以太网技术为工业设备的实时连接与控制

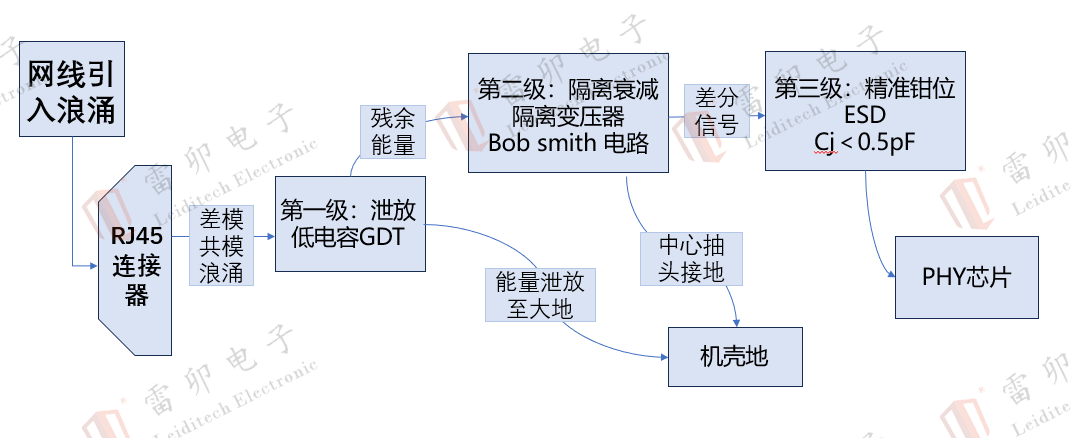

千兆以太网防护:3 步搞定电涌威胁

EMC 小哥围绕以太网接口核心威胁,提供三层防护方案,助力千兆设备实现 “电涌 + 静电可靠防护”。 一、 以太网接口面临的三类威胁 以太网接口在运行中易受多种电磁干扰影响,不同干扰

AD设计DDR3时等长设计技巧

的讲解数据线等长设计。 在另一个文件《AD设计DDR3时等长设计技巧-地址线T型等长》中着重讲解使用AD设计DDR地址线走线T型走线等长处理的方法和技巧。

发表于 07-28 16:33

•4次下载

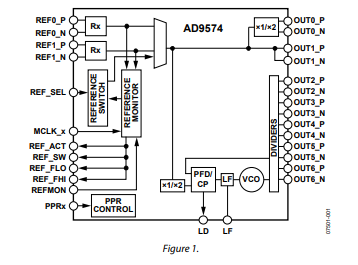

AD9574以太网 千兆以太网时钟发生器技术手册

AD9574具有多路输出时钟发生器功能,内置专用锁相环(PLL)内核,针对以太网和千兆以太网线路卡应用进行了优化。 整数N PLL设计基于ADI公司成熟的高性能、低抖动频率合成器产品系

DDR3 SDRAM配置教程

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynamic Random Access Memory)是DDR SDRAM的第三代产品,相较于DDR2,

灿芯半导体推出DDR3/4和LPDDR3/4 Combo IP

灿芯半导体(上海)股份有限公司(灿芯股份,688691)宣布推出基于28HKD 0.9V/2.5V 平台的DDR3/4, LPDDR3/4 Combo IP。该IP具备广泛的协议兼容性,支持D

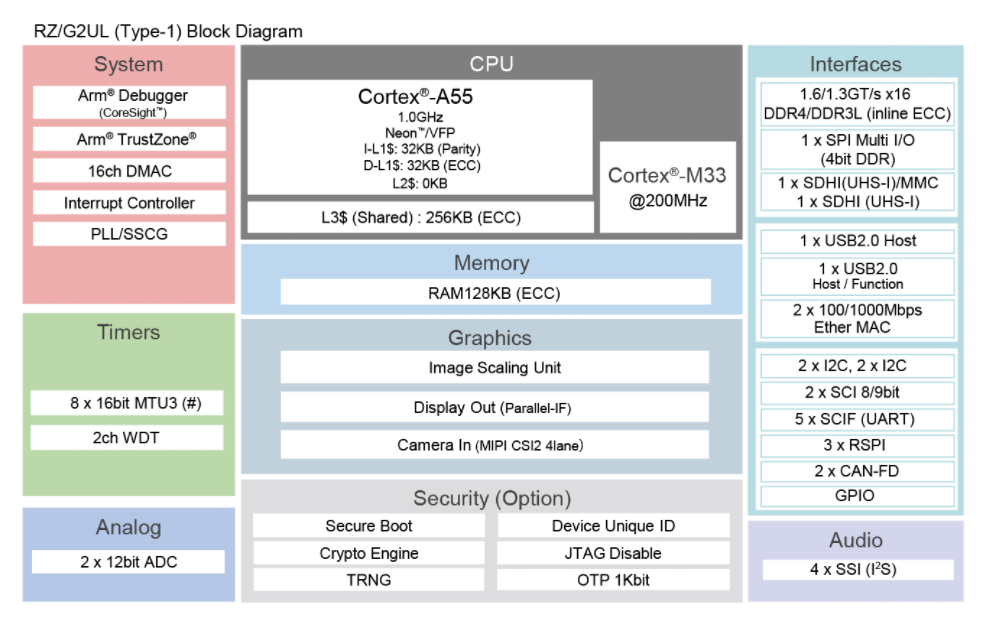

带双通道千兆以太网RZ/G2UL通用型微处理器数据手册

、显示输出、USB 2.0 和千兆以太网,因此特别适用于入门级工业网关控制器和具有简单 GUI功能的嵌入式设备等应用。此外,RZ/G2UL 还有两种类型。 Type-1 支持所有功能,

以太网带宽总是跑不满,是什么原因?

以太网理论速率可以达到1000Mbps,实际考虑到通信各个环节的损耗,也应在800Mbps以上。而实际上却有很多板卡,按照参考电路设计的千兆以太网实测只却只能跑到3

如何创建具有DMA和DDR3内存支持的先进PCIe,千兆以太网设计

如何创建具有DMA和DDR3内存支持的先进PCIe,千兆以太网设计

评论