声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

dsp

+关注

关注

559文章

8214浏览量

363975 -

赛灵思

+关注

关注

33文章

1797浏览量

133148 -

时钟

+关注

关注

11文章

1953浏览量

134543

发布评论请先 登录

相关推荐

热点推荐

基于DSP与FPGA异构架构的高性能伺服控制系统设计

DSP+FPGA架构在伺服控制模块中的应用,成功解决了高性能伺服系统对实时性、精度和复杂度的多重需求。通过合理的功能划分,DSP专注于复杂算法和上层控制,FPGA处理高速硬件任务,两者协同实现了传统

利用DMA如何降低MCU功耗?

利用DMA(直接内存访问)降低MCU功耗的核心在于最小化CPU介入,通过硬件自动完成数据传输任务,使CPU能尽可能长时间处于休眠状态。

CPU休眠时间最大化

DMA接管数据搬运(如外设↔内存、内存

发表于 11-18 07:34

DSP芯片与800G光模块的核心关系:Transmit Retimed DSP、LPO与LRO方案的探讨

本文深入探讨DSP芯片在800G光模块中的核心作用,包括Transmit Retimed DSP架构与新兴LPO/LRO方案的对比分析。DSP在信号均衡、误码控制与长距离传输中不可或缺

璞致电子 UltraScale+ RFSoC 架构下的软件无线电旗舰开发平台

璞致电子 PZ-ZU49DR-KFB 开发板基于 Xilinx ZYNQ UltraScale+ RFSoC XCZU49DR 主控制器,以 "ARM+FPGA 异构架构" 为

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 异构架构下的智能边缘计算标杆

璞致电子推出PZ-ZU15EG-KFB异构计算开发板,搭载Xilinx ZYNQ UltraScale+ XCZU15EG芯片,整合四核ARM Cortex-A53、双核Cortex-R5F

CYBT-213043-MESH如何降低低功耗节点的电流消耗?

LOW_POWER_NODE 之外 \"Mesh_Demo_Temperure_Sensor \" 的最佳设置是什么?\"= 1 \" 以尽可能降低低功耗节点的电流消耗。

发表于 07-04 06:21

Xilinx Ultrascale系列FPGA的时钟资源与架构解析

Ultrascale是赛灵思开发的支持包含步进功能的增强型FPGA架构,相比7系列的28nm工艺,Ultrascale采用20nm的工艺,主要有2个系列:Kintex和Virtex

光模块DSP,迈入低功耗

电子发烧友网报道(文/梁浩斌) 随着光模块往800G、1.6T的高速方向发展,DSP也正在迎来越来越大的挑战,包括性能、功耗等。由于光模块体积小,散热困难,高性能DSP的功耗决定了在

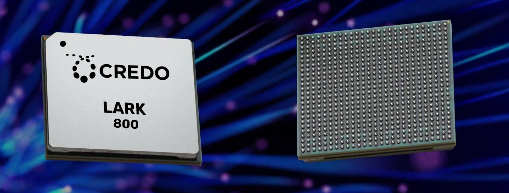

Credo发布Lark系列——为低功耗800G光学DSP树立新标杆

荣幸地宣布:推出其超低功耗的Lark系列光DSP产品。 Lark系列包含两款创新光DSP产品。Lark 800是一款高性能、高可靠性、低功耗的DSP

如何使ADS1247功耗降低?

请问如何使ADS1247功耗降低,我用CC2530控制1247,现在整体功耗在休眠时候是5V0.45mA,但是1247说明上有一句说是:在睡眠模式下功耗只有0.1-0.5uA,我已经

发表于 01-10 07:58

如何降低AFE4400的功耗?

用AFE4400做血氧采集的前端,因为设备的功耗要求比较严格,现有的AFE4400的功耗为1.18Ma。请问能不能再把功耗降低?是否还有可降低

发表于 01-10 07:17

如何降低电子开关的功耗

电子开关是现代电子系统中不可或缺的组成部分,它们控制电流的流动,实现设备的开启和关闭。然而,随着电子设备功能的增强和集成度的提高,功耗问题也日益突出。降低电子开关的功耗不仅有助于节约能源,还能

如何降低AD1247的功耗?

为了使AD1247进入睡眠模式以降低功耗尝试了以下两种方法:

1、将START置为低电平 ,但是至低电平后电流没有变化;

2、通过SLEEP指令,这个进入睡眠后AD1247的确不工作了,唤醒之后

发表于 12-24 07:51

了解UltraScale DSP架构如何降低设计功耗

了解UltraScale DSP架构如何降低设计功耗

评论