Xilinx为Zynq-7000 SoC提供了一个稳健而广泛的支持基础,让用户基于Zynq的开发设计更加高效,同时也帮助客户更快地把设计推向市场.Zynq-7000 SoC的用户对Vivado HLS(高 层次综合)工具特别感兴趣,这是一个非常强大的工具,可以帮助设计者快速地找到Zynq-7000设计架构的平衡点,并开发出高度优化的系统.Zynq平台支持目前最流行的所有软件设计 环境,领先竞争对手整整一代发货,赛灵思还提供了一整套的业经验证的IP,设计工具包以及参考设计,以加速客户的设计

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

33文章

1798浏览量

133651 -

soc

+关注

关注

40文章

4623浏览量

230165 -

Zynq

+关注

关注

10文章

633浏览量

49570

发布评论请先 登录

相关推荐

热点推荐

如何在Zynq UltraScale+ MPSoC平台上通过JTAG启动嵌入式Linux镜像

在之前文章中,我们介绍了如何使用 XSCT 工具通过 JTAG 在 Zynq SoC 上启动嵌入式 Linux 镜像(从 JTAG 启动 Zynq-7000 嵌入式 Linux:使用 XSCT 全

利用蜂鸟E203搭建SoC【1】——AXI总线的配置与板级验证

由于Vivado中Block Design的友好的ui界面以及丰富的IP资源,在FPGA上实现SoC大多会采用Block Design进行设计与实现。对于基于蜂鸟e203内核的SoC设计,为了使其

发表于 10-30 07:35

AMD Vivado IP integrator的基本功能特性

我们还将带您了解在 AMD Zynq UltraScale+ MPSoC 开发板与 AMD Versal 自适应 SoC 开发板上使用 IP integrator 时,两种设计流程之间存在的差异。

Zynq7100 BSP移植,MSH终端不能正确显示是为什么?

由于新版本的RT Thread的BSP不再提供Zynq7000的支持。所以同事从RT Thread(4.0.3)中的Zynq7000移植了一份Zynq 7100的BSP。但是MSH终

发表于 09-19 06:26

灿芯半导体亮相IP-SoC Days 2025

近日,Design & Reuse在上海和首尔分别举办了两场IP-SoC Day研讨会,灿芯半导体(灿芯股份,688691)作为领先的一站式定制芯片及IP供应商,受邀参加两次活动并在上海场研讨会上发表演讲。

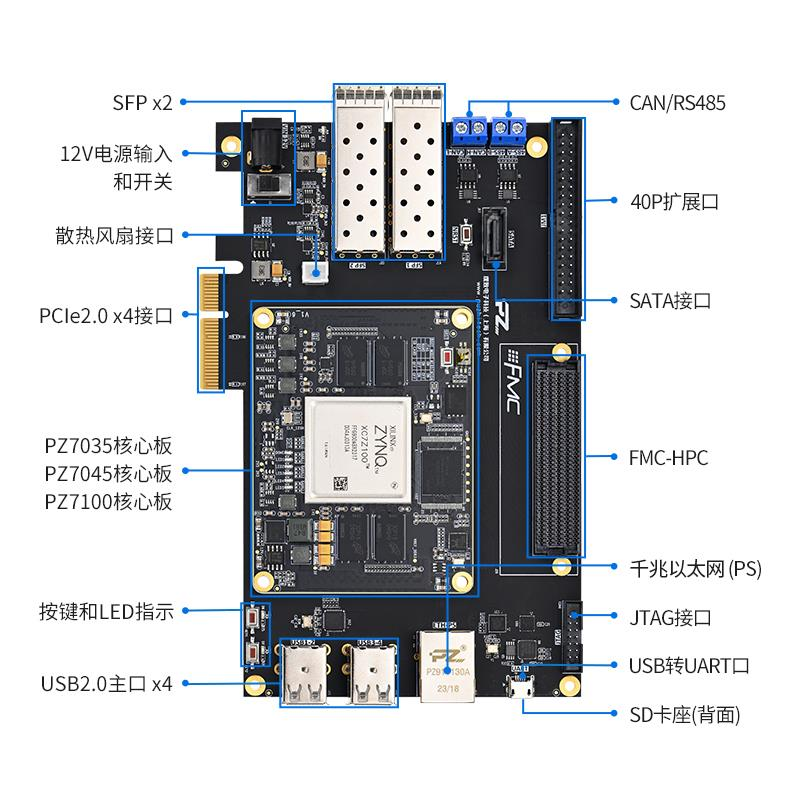

fpga开发板 璞致ZYNQ 7000 系列之 PZ7035/PZ7045/PZ7100-FH 核心板与开发板用户手册

本文介绍了Xilinx Zynq-7000系列可扩展处理平台及其开发板应用。Zynq-7000采用双核ARM Cortex-A9处理器与28nm FPGA架构,支持高性能嵌入式开发。开发板采用核心板

Cadence受邀参加IP SoC China 2025

2025 年 9 月 11 日,由 Design & Reuse 主办的 IP SoC China 2025 将在上海淳大万丽酒店举办。

Zynq-7000 SoC与7系列设备内存接口解决方案数据手册

技术手册,适用于使用LogiCORE IP核(如DDR3/DDR2 SDRAM、RLDRAM II、QDRII+)进行存储器接口设计26。核心功能:IP核配置与时序:详细说明Xilinx MIG(Memory Interface Generator)

发表于 07-28 16:17

•3次下载

Veloce Primo补全完整的SoC验证环境

0 1 简介 SoC 设计团队的任务是在创建昂贵的生产掩膜之前完成完整的系统级验证。这意味着彻底审核所有硬件模块、这些模块之间的所有交互以及为最终应用创建的所有专用软件,而且所有这些任务都要

IP5320 多功能电源管理 SOC中文资料

IP5320 是一款集成升压转换器、锂电池充电管理、电池电量指示的多功能电源管理 SOC,为数码管显示移动电源提供完整的电源解决方案。 IP5320 的高集成度与丰富功能,使其在应用时

发表于 06-11 15:31

•0次下载

IP5316 多功能电源管理 SOC中文资料

IP5316 是一款集成升压转换器、锂电池充电管理、电池电量指示的多冟能电源管理 SOC,为移冨电源提供完整的电源解决方案

发表于 06-11 15:30

•5次下载

灿芯半导体受邀参加IP-SoC Silicon Valley 2025

近日,由Design & Reuse主办的IP-SoC Silicon Valley 2025 Day在美国硅谷成功举办,活动专注于为IP/SoC供应商提供展示创新

Zynq-7000 AP SoC提供业经验证的IP及参考设计

Zynq-7000 AP SoC提供业经验证的IP及参考设计

评论