了解使用Vivado 2016.1中引入的增量编译流程进行调试的好处,以及在使用增量编译实现时添加/删除/修改ILA内核所需的步骤。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

33文章

1798浏览量

133658 -

调试

+关注

关注

7文章

653浏览量

35881 -

Vivado

+关注

关注

19文章

860浏览量

71400

发布评论请先 登录

相关推荐

热点推荐

变频器的静态调试步骤

变频器的“静态调试”通常有两种理解:一种是指电机 不旋转 的情况下,让变频器自动测量电机电气参数的 “静态自学习” (或静态辨识);另一种更广泛的含义是指变频器在 带电机但不带负载 的情况下,进行

GCC -O0 编译内核:调试党的 “救命神器”,这些优势 90% 开发者没吃透!

在 Linux 内核开发、驱动调试或内核问题定位的场景中,“编译优化等级” 是个容易被忽略却影响巨大的选择。GCC 的优化等级从 O0 到 O3、Os、Ofast 各有侧重,而 O0(默认优化等级

基于安路DR1M90 FPSoC的Linux系统全流程开发指南(4)

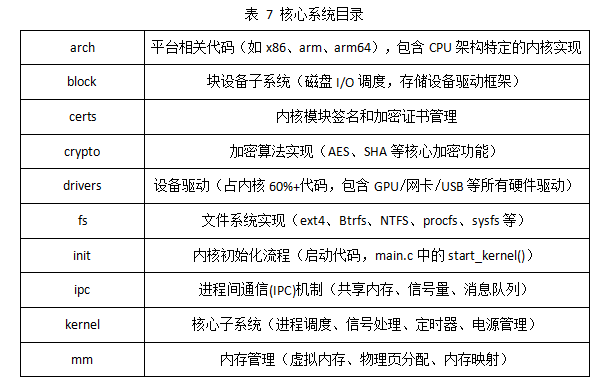

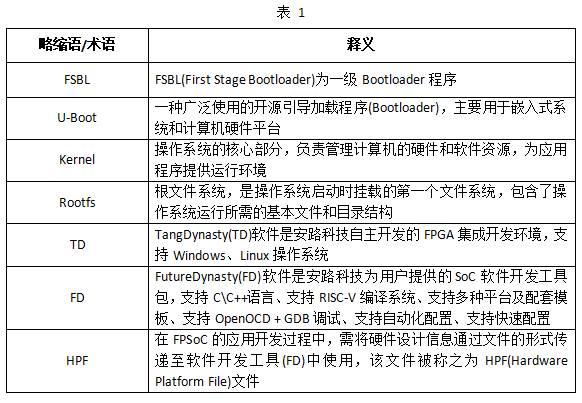

本手册由创龙科技研发,针对安路飞龙 DR1M90,详述 Linux 系统开发流程:LinuxSDK 配置编译、BOOT.bin(FSBL+U-Boot)开发、Kernel 与 Rootfs 开发

基于安路DR1M90 FPSoC 的Linux 系统全流程开发指南(3)

本手册由创龙科技研发,针对安路飞龙 DR1M90,详述 Linux 系统开发流程:LinuxSDK 配置编译、BOOT.bin(FSBL+U-Boot)开发、Kernel 与 Rootfs 开发

基于安路DR1M90 FPSoC 的Linux 系统全流程开发指南(1)

本手册由创龙科技研发,针对安路飞龙 DR1M90,详述 Linux 系统开发流程:LinuxSDK 配置编译、BOOT.bin(FSBL+U-Boot)开发、Kernel 与 Rootfs 开发

利用Verdi调试协处理器的实现步骤

内部信号的执行情况。

1、环境准备

调试过程在Ubuntu系统下进行,需准备好vcs和Verdi软件。另外需要按照《RISC-V架构与嵌入式开发快速入门》一书中的方法,将写好的软件代码进行编

发表于 10-30 08:26

Nuclei Studio 编译调试工程

一.队伍介绍

本文介绍Nuclei Studio 如何编译调试工程。

二.具体方法与步骤

1.每次修改代码后要先保存,再编译。

2.为保险起见,可先“Clean Project”,再

发表于 10-30 06:31

FPGA板下载运行调试流程

今天主要介绍一下整个FPGA板下载运行调试流程。

1、首先,参考网址https://doc.nucleisys.com/hbirdv2/soc_peripherals/ips.html#gpio 第

发表于 10-29 06:57

FPGA板下载调试流程

今天主要介绍一下整个FPGA板下载运行调试流程。

1、首先,参考网址https://doc.nucleisys.com/hbirdv2/soc_peripherals/ips.html#gpio 第

发表于 10-29 06:37

使用DAP miniWiggle在ADS中进行对代码的工程下载以及进入调试模式进行调试,需要安装配置什么环境?

如题,现在想使用DAP miniWiggle在ADS中进行对代码的工程下载以及进入调试模式进行调试,请问需要安装配置什么环境以及相关的有什么操作步骤

发表于 07-31 06:08

如何使用VSCode+gdbserver远程调试ZMC900E

由于嵌入式设备资源受限,通常无法在其上安装庞大的IDE调试程序,且许多嵌入式系统并无桌面环境。为了方便调试自开发程序,本文介绍利用VSCode与gdbserver进行嵌入式设备上程序的远程调试

引入增量编译流程进行调试的好处与步骤

引入增量编译流程进行调试的好处与步骤

评论