在设计中,所有的算数运算符都是按照无符号数进行的。如果要完成有符号数计算,对于加、减操作通过补码处理即可用无符号加法完成。对于乘法操作,无符号数直接采用“*”运算符,有符号数运算可通过定义输出为 signed 来处理。

通过“*”运算符完成有符号数的乘法运算。

module ceshi (out, clk, a, b);

output [15:0] out;

input clk;

//通过 signed 关键字定义输入端口的数据类型为有符号数

input signed [7:0] a;

input signed [7:0] b;

//通过 signed 关键字定义寄存器的数据类型为有符号数

reg signed [7:0] a_reg;

reg signed [7:0] b_reg;

reg signed [15:0] out;

wire signed [15:0] mult_out;

//调用*运算符完成有符号数乘法

assign mult_out = a_reg * b_reg;

always@(posedge clk)

begin

a_reg <= a;

b_reg <= b;

out <= mult_out;

end

endmodule

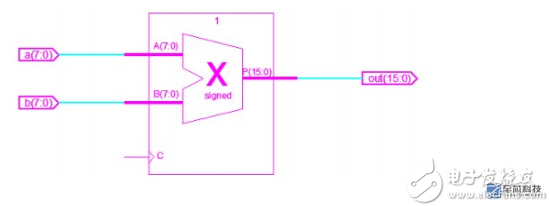

上述程序在 ISE 中的综合结果如下图所示,从其 RTL 结构图可以看到乘法器标注为“signed” ,为有符号数乘法器。

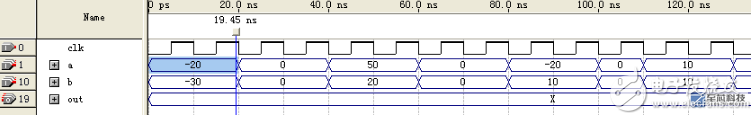

仿真结果图

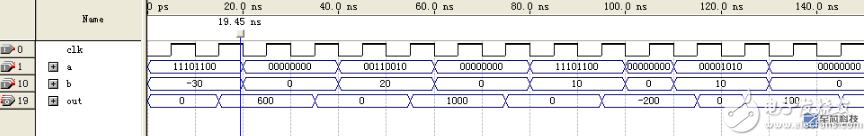

二进制显示的结果

-

FPGA

+关注

关注

1664文章

22518浏览量

639730

发布评论请先 登录

探索LM12454/LM12458/LM12H458:12位+符号数据采集系统的卓越性能

一文读懂电子元件符号:新手也能轻松识别,避坑不踩雷

传递一个无符号的 long 型指针给函数

工控人必备的30个字母符号

位操作的常见错误与应对策略

一个提升蜂鸟E203性能的方法:乘除法器优化

对于指令集中back2back情况的简单介绍

Booth编码的原理及选择

e203除法器算法改进(一)

RISC-V M扩展介绍

rt-thread studio怎么设置才能让char变量是真正的有符号类型?

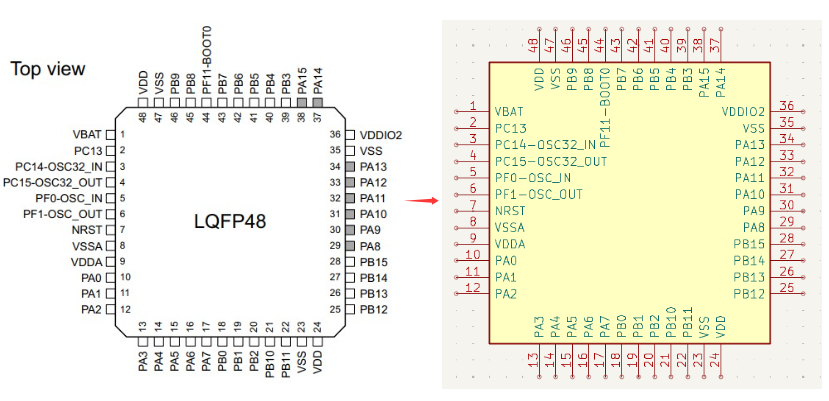

Copilot操作指南(一):使用图片生成原理图符号、PCB封装

fpga 有符号数、无符号数

fpga 有符号数、无符号数

评论