记得刚工作那会儿,师父让我画一块控制板,上面有几十MHz的时钟和几百兆的DDR。那是我第一次意识到,同样是"能通就行"的走线,100MHz和1GHz的设计完全是两码事。板子回来调试的时候,DDR跑不稳,时钟抖动大,查来查去,最后发现是走线没控阻抗、长度匹配也没做。

这个问题我当时踩得挺痛的,所以今天想把这些年摸爬滚打出来的经验整理一下,跟大家聊聊:从100MHz到1GHz,高速接口的PCB设计到底有哪些本质区别?哪些地方必须较真,哪些地方可以稍微松口气?

先搞清楚:什么时候开始要"认真对待"走线?

很多新手有个误解,觉得频率高才需要重视PCB设计。其实关键不在于信号频率本身,而在于信号的上升时间。

说起来有个简单的判断准则:当信号的上升时间小于等于6倍传输延时的时候,这条走线就得当成传输线来处理了。换句话说,走线的物理长度开始"变得重要"了。

拿FR4板材来算,信号传播速度大概是15cm/ns(也就是6英寸/ns)。100MHz的方波信号,如果上升沿是1ns,那临界长度大约是15cm左右。1GHz的信号呢?上升沿可能只有100ps,临界长度直接掉到1.5cm。

说白了:频率越高,允许的"自由走线"长度就越短,等长匹配的要求也越严格。100MHz的时候你还能"差不多就行",到了1GHz,每1mm的误差都可能要命。

阻抗控制:从"差不多"到"锱铢必较"

先说阻抗控制这个话题。我见过不少人画板子,阻抗匹配随便估摸一下就完事了,低频确实没事,但到了高速那就是灾难。

在低速领域,走线更像是根导线,电流流过去就流过去了,不用太操心。但高速信号就不一样了——这时候走线是个"波",得有合适的"管道"让它传过去,管道太粗太细都不行。

从数值要求来看,100MHz和1GHz的差异大概是这样的:

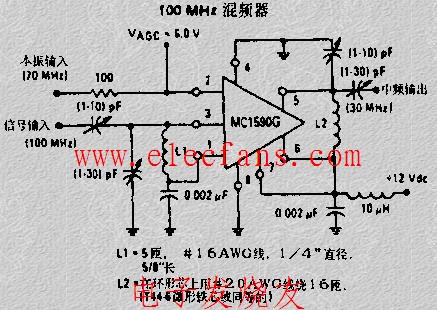

图1:阻抗容差要求随速率提升而收紧(左);不同PCB材料的损耗因子对比(右)

| 参数 | 100MHz级别 | 1GHz级别 |

|---|---|---|

| 阻抗容差 | ±10%~±15% | ±5%~±3% |

| 参考平面 | 基本完整即可 | 必须完整,禁跨分割 |

| 板材要求 | 普通FR-4 | 高频低损耗板材 |

| 阻抗计算 | 大概估算就行 | 必须用SI9000等工具精确计算 |

实际上我自己画板的时候,1GHz以上的设计基本上都会用Polar SI9000先跑一遍仿真,确认线宽、介质厚度、介电常数这些参数,然后再跟板厂反复沟通,确认他们能做到的公差范围。

还有个容易被忽略的点——板材本身。普通FR-4的介电常数(Dk)大概是4.2~4.5,听起来好像差别不大,但到了高频就不一样了。FR-4在1GHz下Dk大概4.5,到了10GHz可能就只有4.2了,±10%的批次波动更是常见。高速板材比如Rogers RO4350B,Dk稳定在3.48左右,波动能控制在±0.02以内,损耗因子(Df)也从FR-4的0.02降到了0.0037。

个人经验:如果你的产品工作在5GHz以上,或者速率超过10Gbps,别省板材的钱。一块Rogers板的成本可能只比FR-4贵30%,但能省掉你后面大量的调试时间和返工成本。

走线长度匹配:精度要求天差地别

长度匹配这个话题,估计每个画过DDR或PCIe的工程师都能倒出一肚子苦水。我自己也踩过不少坑,尤其是早期不懂的时候。

先说原理吧。信号在PCB上传输的速度是固定的,在FR-4里大概是15cm/ns。如果两根并行的信号线长度差了1mm,那到达接收端的时间就差了大概6.5ps。100MHz的时候,一个时钟周期是10ns,6.5ps的偏差只占0.065%,几乎可以忽略。但到了1GHz呢?周期只剩1ns,6.5ps就变成了6.5%,这个影响就非常可观了。

图2:不同信号频率下的走线长度匹配要求(mm和mil双坐标)

具体到差分对的长度匹配,不同协议的差别挺大的:

图3:典型高速接口的数据速率(左);长度匹配要求随速率提升而急剧收紧(右)

| 接口类型 | 典型速率 | 对内长度差要求 |

|---|---|---|

| CAN/RS485 | <100Mbps | ≤2.5mm(100mil) |

| USB 2.0 | 480Mbps | ≤3.8mm(150mil) |

| USB 3.0/3.1 | 5Gbps | ≤0.13mm(5mil) |

| PCIe 4.0 | 16GT/s | ≤0.13mm(5mil) |

| PCIe 5.0 | 32GT/s | ≤0.05mm(2mil) |

| DDR4-3200 | 3200Mbps | 组内≤0.64mm(25mil) |

| DDR5-6400 | 6400Mbps | 组内≤0.05mm(2mil) |

看到没?从USB 2.0到USB 3.0,长度匹配要求直接提升了30倍。PCIe 5.0和DDR5更是到了"变态"的级别,2mil的误差,换算成时间大概只有0.3ps。这个精度要求,没点真本事还真搞不定。

过孔设计: Stub这个"隐形杀手"不可忽视

过孔设计是我觉得最容易出问题、也最容易被新手忽略的地方。走线换层打个孔,看起来简单,实际上对高速信号的影响特别大。

先说一个概念——Stub。打个比方,你从1楼走到10楼,但电梯只用到5楼,剩下的5层就是"残桩"。这个残桩在高频下会形成谐振,吸掉信号能量,严重的还会导致信号直接挂掉。

图4:过孔Stub长度与谐振频率的关系;10Gbps信号约在6GHz处产生谐振

有个经验公式:Stub长度(英寸)× 谐振频率(GHz)≈ 0.3。比如一个Stub长度是1.27mm(约0.05英寸),那它大概在6GHz左右会产生谐振。

踩坑案例:之前做一个10Gbps的光模块设计,板子回来测试发现眼图一直开不好。查了半天,最后用TDR发现是过孔Stub的问题——信号从表层换到内层,但孔一直穿到背面,多出来的残桩在6GHz附近形成了谐振。后来改成背钻工艺,把Stub削掉,眼图瞬间就开了。

到了1GHz以上,过孔设计的规矩就多了几条:

高速信号换层时,必须在附近加回流地孔,给信号提供最短的回流路径

过孔数量能少则少,能不换层就别换层

如果必须换层,差分对的两根线过孔要对称,位置要一致

Stub长度越短越好,高频场景下尽量控制在5mil以内

必要时采用背钻工艺,从根本上消除Stub

串扰控制:从"隔开就行"到"精确算间距"

串扰这个问题,在低速设计中基本不用操心,但在高速领域就不得不认真对待了。

我记得有个"3W原则",说的是走线中心到中心之间的距离要大于3倍线宽,这样可以避免90%的耦合问题。这个原则在100MHz以下确实挺好用的,简单粗暴又有效。

但到了1GHz级别,3W原则就不够用了。我自己总结的高速串扰控制要点:

同组信号尽量紧耦合:差分对两根线之间的距离要"近",这样共模噪声才能更好地抵消

不同组之间要保持足够间距:4W、5W甚至更宽,间距越大串扰越小

关键信号要包地:敏感信号两侧铺铜皮并打上密集的地孔,形成电磁屏蔽

避免不同速率的信号平行走线:高速线和低速线尽量分层,实在要平行就隔开

到了DDR5这种并行总线的场景,串扰控制就更讲究了。JEDEC规范里对DQ-DQS的关系有非常明确的定义,组内间距可以缩到2W,但前提是必须有完整的地平面做参考。

电源完整性:PDN设计必须认真对待

说到电源完整性,这个话题在100MHz时代可能还不是主角,但到了GHz级别就变成"一号玩家"了。

芯片工作需要稳定的供电,但电流消耗是动态的,会有波动。如果电源分配网络(PDN)设计得不好,电压就会跳动,表现为"噪声"。对于低速电路来说这点噪声不算什么,但高速电路的噪声裕量本来就很小,电源噪声稍大一点就会导致误码。

我总结了几个PDN设计的要点:

去耦电容就近放置:电容离芯片电源引脚越近越好,走线要粗短,减少寄生电感

不同容值搭配使用:大电容滤低频,小电容滤高频,并联使用覆盖更宽频段

电源/地平面要紧耦合:两层之间介质要薄,形成天然的平板电容

避免电源平面分割:高速信号换层时,回流路径不能被切断

DDR5设计中对电源完整性的要求又上了一个台阶。VDDQ电压降到了0.6V,但电流反而更大了,电源噪声的容忍度只有几个百分点。很多DDR5调试的问题,最后查出来都是电源PDN设计不到位。

EMI/EMC:高速设计的"及格线"

最后一个话题是电磁兼容。这个问题比较特殊,因为它不仅是设计问题,还涉及到认证测试。很多产品设计得挺好,功能也没问题,但一做EMC测试就挂。

高速信号的EMI问题,本质上是信号完整性问题的"副作用"。信号反射、阻抗不匹配、串扰这些,都会产生额外的电磁辐射。所以某种程度上说,把信号完整性做好了,EMI问题也就解决了一大半。

几个实用的EMC设计建议:

高速信号线要走内层,用完整的地平面包裹,减少辐射

金属外壳要有良好的接地,连接器安装孔周围要多打接地孔

晶振和时钟电路是EMI重灾区,要重点屏蔽

总结:核心差异一览

说了这么多,最后来张表格总结一下100MHz和1GHz在PCB设计上的核心差异:

图5:100MHz与1GHz级别在PCB设计各要素上的核心差异对比

| 设计要素 | 100MHz级别 | 1GHz级别 |

|---|---|---|

| 阻抗容差 | ±10%~±15% | ±3%~±5% |

| 长度匹配 | 几百mil都行 | 几mil级别 |

| 板材选择 | 普通FR-4 | 高速低损耗板材 |

| 过孔处理 | 随便打,别断就行 | 控制数量,背钻处理 |

| 串扰控制 | 3W原则足够 | 需要精确仿真 |

| 电源设计 | 大概有去耦就行 | 完整PDN设计 |

| 参考平面 | 基本完整即可 | 必须完整,禁跨分割 |

| 仿真验证 | 可做可不做 | 必须做 |

其实说到底,100MHz到1GHz的跨越,不只是数字上的变化,而是设计理念的转变。低速设计可以靠经验、靠"差不多就行",高速设计就得靠理论、靠仿真、靠精确计算。

我的建议是:如果你准备做高速设计,先把信号完整性的基础理论过一遍,搞清楚反射、串扰、时序这些概念背后的物理意义。然后找一款合适的仿真工具,实战演练一下。最后,在设计中多留裕量、多做验证、少走弯路。

毕竟,高速PCB设计这件事,踩过的坑都是经验。没踩过的,提前了解也能少走弯路。

最后一句话:设计的时候多花1小时仿真,可能就能省下10小时的调试时间。这笔账怎么算都划算。

-

pcb

+关注

关注

4415文章

23955浏览量

426011 -

阻抗

+关注

关注

17文章

992浏览量

49480 -

高速接口

+关注

关注

1文章

79浏览量

15340

原文标题:从100M到1G,高速接口的PCB设计到底变了什么

文章出处:【微信号:FPGA研究院,微信公众号:FPGA研究院】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

超过100MHz的高频电源纹波超标是否会影响高速信号产生干扰

高速PCB设计

FX3接口在100MHz的ADC接口

请问AD9643是否支持中频输入1GHz?

GPIF无法在100MHz时钟下工作

AD9643支持中频输入1GHz吗?

Cadence高速PCB设计

ADL5802: Dual Channel, High IP3, 100MHz to 6GHz Active Mixer Data Sheet

100MHz 至 40GHz RMS 功率检波器 具 1dB 准确度和 35dB 动态范围

LTC6400-20 - 1GHz 和 2GHz 全差分放大器实现了高速 ADC 性能

100MHz和1GHz高速接口在PCB设计上的核心差异

100MHz和1GHz高速接口在PCB设计上的核心差异

评论