拆卸集成电路的几种方法,How to remove IC

关键字:拆卸集成电路

在集成电路检修时,经常需要从印刷电路板上拆卸集成电路,由于集成电路引脚多又密集,拆卸起来很困难,有时还会损坏集成电路及印刷板。但是,只要我们细心观察,善于动脑和总结,完好拆卸集成电路并不是一件很困难的事。

1.吸锡器吸锡拆卸法:使用吸锡器拆卸集成块,这是一种常用的专业方法,使用工具为普通吸、焊两用的电烙铁。拆卸集成块时,只要将加热后的两用烙铁头放在要拆卸的集成块引脚上,待焊点锡熔化后被吸人吸锡器内,全部引脚上的焊锡吸完后,集成块自然就可以轻松拿掉。

2.内热式解焊器拆卸法:如附图所示,使用时,首先挤压橡皮球,将焊料收集筒上的锡焊头置于解焊点上,待焊料熔化后,放松橡皮球,焊料被吸入收集筒内。然后将电烙铁离开解焊点,再挤压橡皮球,将收集筒内的焊料从吸锡头喷出。

3.医用空芯针头拆卸法:寻找医用8~12号空芯针头几个,使用时,针头的内径正好能套住集成块引脚为宜。拆卸时用烙铁将引脚焊锡熔化,及时用针头套住引脚.然后拿开烙铁并旋转针头,等焊锡凝固后拔出针头,这样,该引脚就和印刷板完全分开。所有引脚都如上述方法做一遍,集成块就可以轻易被拿掉。

4.多股铜线吸锡拆卸法:取一段新塑料软线,用钳子拉去塑料外皮。将裸露的多股铜丝截成70mm-100mm的线段备用,并将每段头尾稍稍拧几转,使其不会松散。揿压裸线也能成股均匀地平摊被压住为好,将裸线段用酒精松香溶液均匀地浸透晒干。线上的松香不要过多.以免污染印刷版。拆卸集成块时,将上述处理过的裸线压在集成块的焊脚上,并压上电烙铁(一般以45W~75W为宜)。此时,焊脚处焊锡迅速熔化,并被裸线吸附。然后缓缓拉动裸线,使裸线上未受锡部分行经焊脚烙铁间。由于毛细现象作用,焊脚上焊锡被吸收殆尽,焊脚即与印刷板分离。待所有焊脚吸焊工作完成后,集成块即可与印刷板分离。

5.电烙铁毛刷配台拆卸法:该方法简单易行,只要有一把电烙铁和一把小硬质毛刷即可。拆卸集成块时先将电烙铁加热,待达到熔锡温度,将引脚上的焊锡熔化后.趁热用毛刷扫掉熔化的焊锡(用硬鬃刷为宜.如果一次刷不干净可加热再刷,直至把焊锡清除掉).这样就可使集成块的引脚与印刷板分离。该方法可分脚进行.也可分列进行。最后用尖镊子或小一字螺丝刀撬下集成块。

6.增加焊锡熔化拆卸法:这种方法是最省事的方法.只要给待拆卸的集成块引脚上再增加一些焊锡,使每列引脚的焊点连接起来,这样以利于传热,便于拆卸。拆卸时用电烙铁每加热一列引脚,就用尖镊子或小“一”字螺丝刀撬一撬。给两列引脚轮换加热.直到拆下为止:一般情况下,每列引脚加热两次即可拆下。

作者:刘峙

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

发布评论请先 登录

相关推荐

热点推荐

行芯科技亮相IIC 2026国际集成电路展览会暨研讨会

近日,全球集成电路领域的年度标杆盛会——2026国际集成电路展览会暨研讨会(IIC 2026)在上海圆满落幕。

2026年1至2月中国集成电路出口额同比大增69%

根据海关总署3月10日公布的数据,今年1月和2月,中国集成电路(IC)出口额达到3046.7亿元,同比增长68.9%。按数量计算,集成电路出口量比上年同期增长13.7%,达到524.6亿个。

覆盖全“芯”链路!IICIE国际集成电路创新博览会解锁集成电路全链新商机

原“SEMI-e深圳国际半导体展暨集成电路产业创新展”全面升级的 IICIE 国际集成电路创新博览会(简称“IC创新博览会”)将于2026年9月9日-11日登陆深圳国际会展中心(宝安)。本届博览会以

焕新启航·品质跃升 IICIE国际集成电路创新博览会,构建全球集成电路全产业链生态平台

为积极响应国家集成电路创新发展战略部署,加快推进集成电路产业良性发展生态,原“SEMI-e深圳国际半导体展暨集成电路产业创新展”正式升级为“ IICIE国际集成电路创新博览会(简称

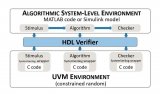

基于模型的设计在电机控制IC领域的应用

为应对日益加剧的竞争压力,集成电路 (IC) 制造商正不断缩短产品交付周期,而与此同时,设计日益复杂,再加之客户对质量和性能的期望值也在增加。传统的设计方法是团队基于文档对规范进行验证,并在最终量产版本推出之前制作多个原型。许多

飞秒激光:重塑集成电路(IC)行业精密制造的未来

1.0 引言:突破微纳加工的精度瓶颈 随着集成电路(IC)行业不断向更小的技术节点、更复杂的封装结构和更高的集成度迈进,精密加工技术正面临前所未有的挑战。微型化的趋势、新材料的广泛应用以及对产品良率

使用HDL Verifier加速信号处理集成电路的验证

信号处理集成电路(IC)设计的验证带来了一些独特的挑战,这些挑战可能会给传统的测试方法带来压力。滤波器、混频器和其他高级信号处理功能的算法复杂性需要严格的验证,以确保实施的 IC 能够

PDK在集成电路领域的定义、组成和作用

PDK(Process Design Kit,工艺设计套件)是集成电路设计流程中的重要工具包,它为设计团队提供了与特定制造工艺节点相关的设计信息。PDK 是集成电路设计和制造之间的桥梁,设计团队依赖 PDK 来确保设计能够在晶圆厂的工艺流程中正确制造。

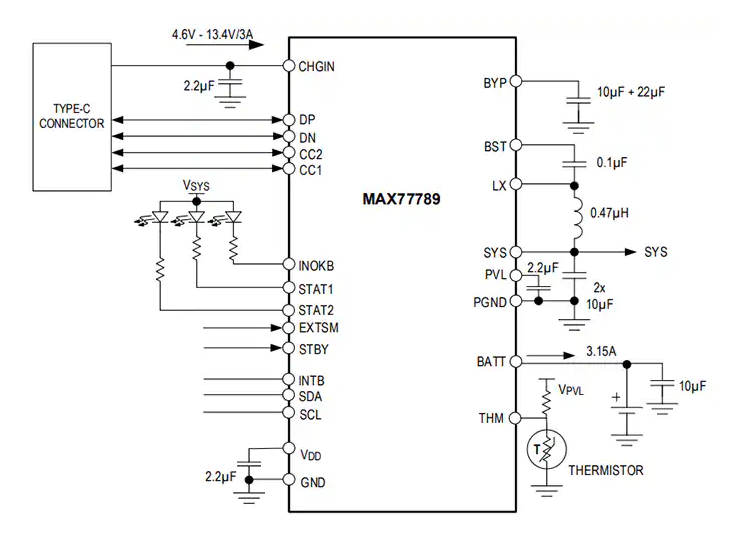

Analog Devices / Maxim Integrated MAX77789 3.15A充电器集成电路 (IC)数据手册

Analog Devices / Maxim Integrated MAX77789 3.15A充电器集成电路 (IC) 具有集成USB Type-C® CC检测和反向升压功能。MAX77789

拆卸集成电路的几种方法,How to remove IC

拆卸集成电路的几种方法,How to remove IC

评论