“我们基于 HDL Verifier 的新工作流程的一个明显优势是能够快速识别缺陷来源。” —— Steffen Löbel,NXP

作者:来自 NXP的Steffen Löbel 和 Jan Hahlbeck

*本文内容采用了机器翻译

信号处理集成电路(IC)设计的验证带来了一些独特的挑战,这些挑战可能会给传统的测试方法带来压力。滤波器、混频器和其他高级信号处理功能的算法复杂性需要严格的验证,以确保实施的 IC 能够按照位真精度按预期运行。此外,由于 IC 通常在各种可能的输入和配置下运行,因此必须评估极端情况——罕见但关键的情况,这些情况可能会避开专注于预定义、可预测序列的测试计划。

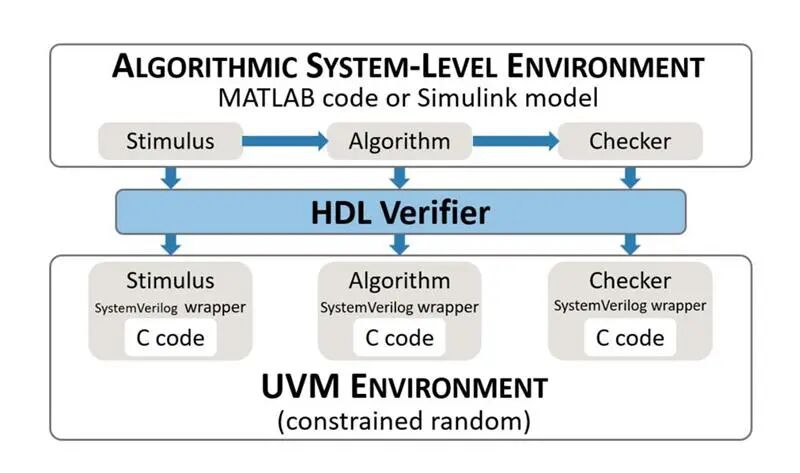

我在 NXP 的团队采用了一种新的 IC 验证工作流程来应对这些挑战。基于 MATLAB,Simulink 和 HDL Verifier,该工作流程结合了约束随机验证和通用验证方法 (UVM) 技术来验证边缘情况并使用随机输入探索状态空间,同时通过约束保持控制(图 1)。在这个最近用来验证汽车行业收音机调谐器 IC 的工作流程中,MATLAB 和 Simulink 模型使用 HDL Verifier 导出为 SystemVerilog DPI-C 组件,并作为参考模型集成到我们基于 Cadence Xcelium 仿真器的验证环境的验证测试平台中。这种方法不仅使我们能够将验证时间缩短 20% 到 30%,而且还使我们能够提高测试覆盖率并在开发早期发现更多实施缺陷。

图 1. IC 验证工作流程结合了约束随机验证和 UVM 技术。

新旧工作流程对比

过去测试类似的 IC 设计时,我们通常使用MATLAB为整个系统生成输入刺激。然后,我们会在 MATLAB 或 Simulink 中运行模拟,并将结果作为黄金参考模式。一旦 RTL 实现完成,我们将对 DUT 施加相同的刺激并根据黄金参考检查其结果。虽然这种方法有效,但也有一些缺点。首先,验证大部分是端到端的,由于所有组件都是一起测试的,因此很难确定缺陷的根本原因。其次,约束随机验证不易进行。因此,虽然常见场景和用例得到了验证,但许多边缘情况却没有得到验证。第三,它没有遵循 UVM,而 UVM 已经成为我们实现测试平台的标准框架。

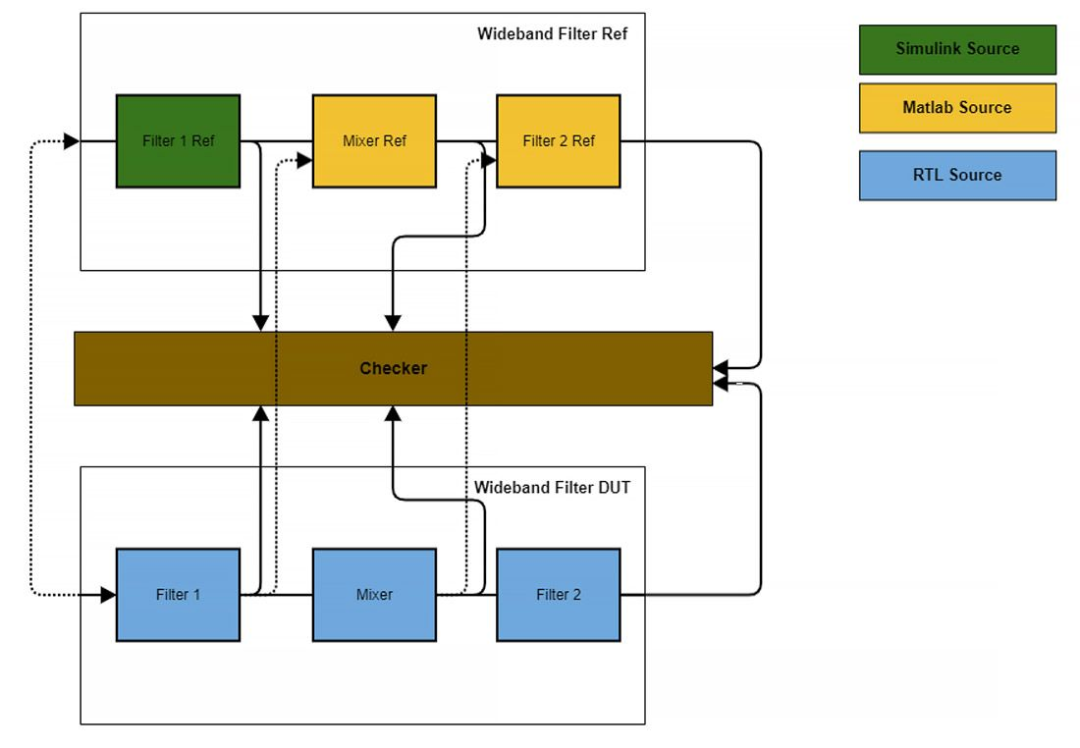

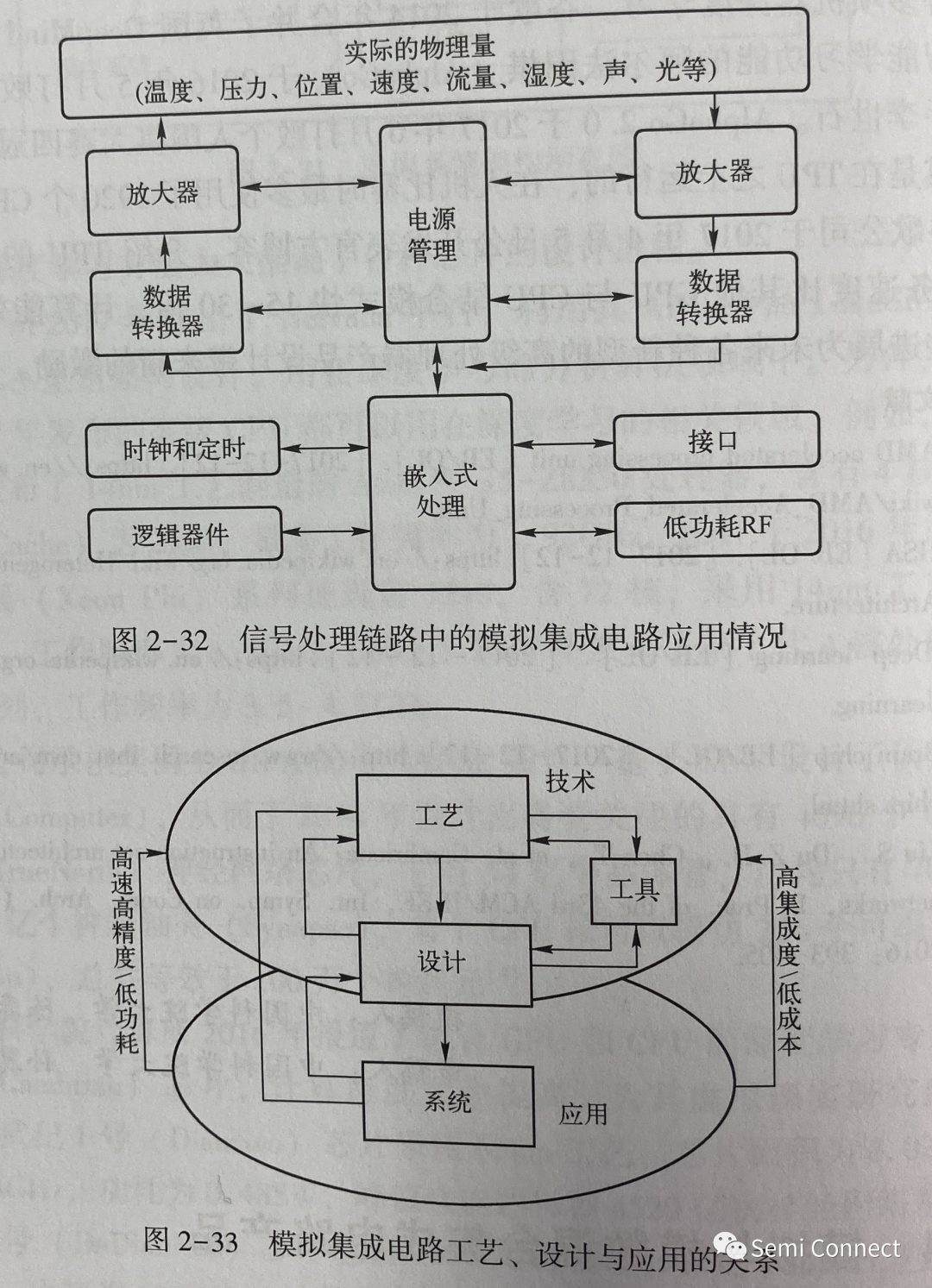

相比之下,新的工作流程使得我们能够在 HDL 仿真环境(Cadence Xcelium)中直接重用现有的 MATLAB 和 Simulink 参考模型。参考模型中的每个组件都与 DUT 中的对应组件相对应。例如,图 2 所示的示例信号处理链包括在 Simulink 中建模的滤波器,后跟混频器和在 MATLAB 中建模的第二个滤波器。我们使用 HDL Verifier 为带有 SystemVerilog DPI-C 包装器的模型生成 C 代码,使我们能够将每个组件集成到测试台中。

在 HDL 仿真环境中,参考模型组件和 DUT 组件会并行运行。与此同时,一个充当 UVM 记分板角色的检查器会实时评估它们的输出。该检查器会对每一个关联组件对(例如,参考模型的混频器与 DUT的混频器)的输出以及整个端到端链路的输出,进行行为一致比较。

图 2. 用于比较 MATLAB 和 Simulink 生成的参考模型组件(顶行)的结果与相应 DUT 组件(底行)的结果的并行结构。

随机化输入并可视化结果

在测试台上运行初步测试(在本例中使用一组预定义的 AM、FM 和数字音频广播 (DAB) 无线电流)以验证信号处理算法的基本功能后,工作流程的下一步是约束随机验证。此阶段涉及大量模拟,其中设计的所有配置设置都被分配了约束范围内的随机值。例如,我们改变混频器设置、滤波器设置、延迟、增益和其他关键配置参数,并运行模拟来评估每组随机配置选项的设计性能。

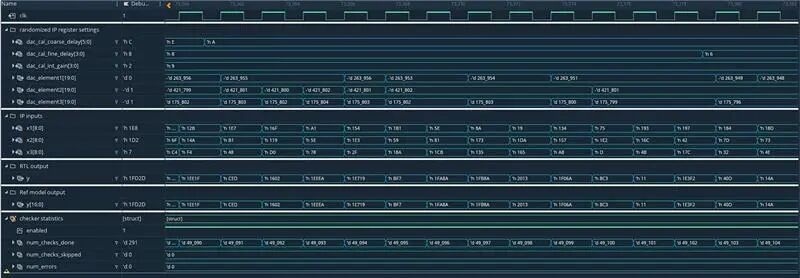

对于每个测试,我们可以查看详细的结果,包括所使用的具体设置、用作 IP 刺激的输入、参考模型实现的结果、RTL 实现的结果以及检查器比较的结果(图 3)。

图 3. 波形显示显示随机 IP 寄存器设置、IP 输入、RTL 输出、参考模型输出和检查器统计数据。

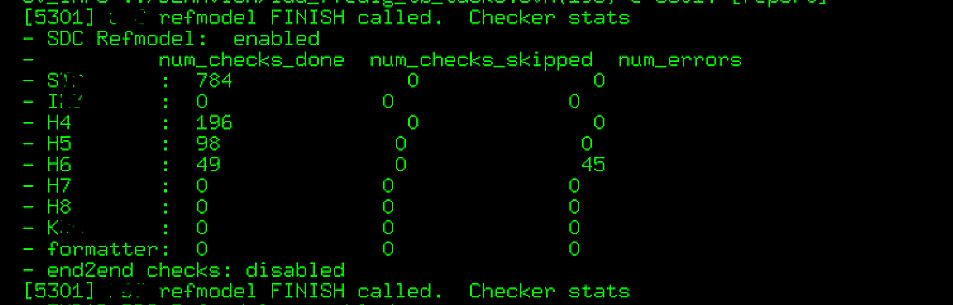

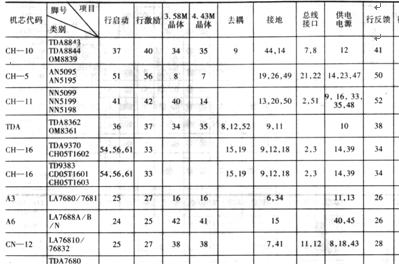

我们还审查了显示一系列完整组件的汇总结果的报告(图 4)。这些报告显示了对链中每个组件执行的检查次数以及错误数量 - 即在 RTL 和参考模型输出之间发现的差异数量。

图 4. 显示多个组件的测试结果的摘要报告。其中,对 H6 组件的测试发现了 45 个错误。

当发现错误时,我们会检查 MATLAB 或 Simulink 中的参考模型实现,并检查 RTL 实现。在某些情况下,我们已经将差异的根源追溯到原始参考设计,但问题更多时候源于 RTL 实现错误。无论哪种情况,一旦缺陷被诊断和纠正,我们就会重新运行测试模拟,以验证修复是否完全解决了参考模型和 RTL 实现之间的任何差异。

关键改进和后续步骤

我们基于 HDL Verifier 的新工作流程的一个明显优势是能够快速识别缺陷来源。与依赖端到端测试的方法相比,面向 UVM 的方法可以进行组件级和系统级测试(就像我们所应用的方法一样),从而更容易地查明具有缺陷的子系统以及可用于复制缺陷的该组件的特定刺激。

此外,由于随机设置通常以设计工程师未曾预料到的方式测试系统,与专注于成熟用例的传统测试计划相比,新的工作流程有助于在开发过程中更早地发现实施缺陷。简而言之,我们无需人工检查即可发现缺陷,也无需花时间考虑要测试的异常场景和边缘情况。

我们能够在 HDL 仿真中重复使用现有的 MATLAB 和 Simulink 模型,并且这种重复使用的好处会在 IC 的每次后续旋转或修订中继续叠加。综合起来,这些优势使我们在无线电信号处理 IC 上实现了验证时间的大幅缩短,最高可达 30%。基于这一指标以及我们已实现的其他优势,其他 NXP 团队正在寻求采用相同的工作流程来开发雷达 IC 和其他 IC 设计的无线电前端。

-

集成电路

+关注

关注

5446文章

12463浏览量

372602 -

matlab

+关注

关注

189文章

3018浏览量

237545 -

仿真

+关注

关注

53文章

4404浏览量

137644 -

混频器

+关注

关注

10文章

859浏览量

49407

原文标题:NXP×MATLAB | 使用 HDL Verifier 加速信号处理集成电路的验证

文章出处:【微信号:MATLAB,微信公众号:MATLAB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

集成电路的设计与概述

集成电路可测性设计方法

数字集成电路设计中的硬件加速验证技术

利用ADMS平台加速混合信号集成电路设计

rbd单片机信号处理集成电路

使用HDL Verifier加速信号处理集成电路的验证

使用HDL Verifier加速信号处理集成电路的验证

评论