Microchip 47L04/47C04/47L16/47C16 EERAM:高可靠非易失性存储解决方案

在电子设计领域,数据的可靠存储与快速读写一直是工程师们关注的重点。Microchip的47L04/47C04/47L16/47C16系列4/16 Kbit SRAM结合EEPROM备份的EERAM(Electrically Erasable Random Access Memory),为我们提供了一种出色的解决方案。下面,我们就来深入了解一下这款产品。

文件下载:47C04T-I SN.pdf

产品概述

Microchip的47L04/47C04/47L16/47C16(47XXX)是具有EEPROM备份的4/16 Kbit SRAM。它采用I²C串行接口,内部组织为512 x 8位(47X04)或2,048 x 8位(47X16)的存储器。该系列产品提供了无限的SRAM读写周期,同时EEPROM单元可实现数据的高耐久性非易失性存储。

产品选型

| 产品型号 | 密度 | Vcc 范围 | 最大时钟频率 | 温度范围 | 封装 |

|---|---|---|---|---|---|

| 47L04 | 4 Kbit | 2.7V - 3.6V | 1 MHz | I, E | P, SN, ST |

| 47C04 | 4 Kbit | 4.5V - 5.5V | 1 MHz | I, E | P, SN, ST |

| 47L16 | 16 Kbit | 2.7V - 3.6V | 1 MHz | I, E | P, SN, ST |

| 47C16 | 16 Kbit | 4.5V - 5.5V | 1 MHz | I, E | P, SN, ST |

产品特性

1. SRAM与EEPROM备份结合

- 内部组织:根据型号不同,内部组织为512 x 8位(47X04)或2,048 x 8位(47X16)。

- 自动存储与恢复:在掉电时(使用可选外部电容),数据自动存储到EEPROM阵列;上电时,数据自动从EEPROM恢复到SRAM阵列。

- 手动操作:提供硬件存储引脚用于手动存储操作,同时支持软件命令启动存储和恢复操作。

- 存储时间:47X04最大存储时间为8 ms,47X16最大存储时间为25 ms。

2. 非易失性外部事件检测标志

该标志可用于检测外部事件,为系统提供更多的监控和控制能力。

3. 高可靠性

- 无限读写周期:SRAM具有无限的读写周期,保证了数据的快速读写性能。

- 高耐久性:EEPROM的存储周期超过100万次,数据保留时间超过200年。

- ESD保护:所有引脚的ESD保护大于4000V,提高了产品的抗干扰能力。

4. 高速I²C接口

- 标准时钟频率:支持行业标准的100 kHz、400 kHz和1 MHz时钟频率。

- 零周期延迟:读写操作零周期延迟,提高了数据传输效率。

- 噪声抑制:采用施密特触发器输入,有效抑制噪声。

- 可级联:最多可级联四个设备,方便扩展系统容量。

5. 写保护

支持从SRAM阵列的1/64到整个阵列的软件写保护,保护重要数据不被误写。

6. 低功耗CMOS技术

- 典型工作电流:200 µA,降低了系统功耗。

- 最大待机电流:40 µA,适合低功耗应用。

7. 宽温度范围

提供工业级(-40°C 到 +85°C)和扩展级(-40°C 到 +125°C)温度范围,满足不同应用环境的需求。

8. 汽车级认证

符合AEC - Q100标准,可用于汽车电子等对可靠性要求较高的应用场景。

电气特性

1. 绝对最大额定值

- VCC:最大6.5V

- A1、A2、SDA、SCL、HS引脚相对于VSS:-0.6V到6.5V

- 存储温度:-65°C到 +150°C

- 偏置下的环境温度:-40°C到 +125°C

- 所有引脚的ESD保护:≥4 kV

2. DC特性

涵盖了高电平输入电压、低电平输入电压、低电平输出电压、输入泄漏电流等多项参数,为电路设计提供了详细的电气参考。

3. AC特性

包括时钟频率、时钟高时间、时钟低时间、输入上升时间、输入下降时间等参数,确保了I²C接口的高速稳定运行。

功能描述

1. 工作原理

47XXX支持双向两线总线和数据传输协议(I²C),主机设备控制总线的启动和停止条件,47XXX作为客户端工作。主机和客户端都可以作为发送器或接收器,但主机设备决定当前的工作模式。

2. 总线特性

2.1 串行接口

- 数据传输条件:数据传输只能在总线空闲时启动,时钟线为高电平时,数据线必须保持稳定,否则将被解释为启动或停止条件。

- 启动条件:时钟线(SCL)为高电平时,数据线(SDA)从高到低的转换确定启动条件。

- 停止条件:时钟线(SCL)为高电平时,数据线(SDA)从低到高的转换确定停止条件。

- 数据有效:启动条件后,时钟信号高电平期间数据线稳定表示数据有效,数据必须在时钟信号低电平期间改变。

- 确认信号:每个接收设备在接收到每个字节后必须生成确认信号,主机设备必须生成与该确认位相关的额外时钟脉冲。

2.2 设备寻址

控制字节是主机设备发送的第一个字节,包含4位操作码、两个用户可配置的芯片选择位(A2和A1)、一个固定为‘0’的芯片选择位和一个读写位。芯片选择位必须与相应引脚的逻辑电平匹配,设备才能响应。

3. SRAM阵列操作

3.1 写操作

- 字节写:主机设备发送控制字节和2字节数组地址,然后发送数据字节,数据在确认位的SCL上升沿锁存到SRAM阵列。

- 顺序写:与字节写类似,但主机设备可以连续发送多个数据字节,地址指针自动递增。

3.2 读操作

- 当前地址读:根据当前地址指针的值开始读取数据,读取后地址指针自动递增。

- 随机读:先设置地址指针,然后发送控制字节进行读取操作。

- 顺序读:与随机读类似,但主机设备在接收到第一个数据字节后发送确认信号,继续读取后续数据。

4. 控制寄存器操作

4.1 状态寄存器

控制软件写保护、自动存储功能、报告阵列是否被修改以及包含硬件存储事件标志。

4.2 命令寄存器

用于执行软件控制的存储和恢复操作,包括软件存储命令和软件恢复命令。

4.3 写操作

选择控制寄存器并设置读写位为‘0’,接收的下一个字节被解释为寄存器地址,然后发送数据字节进行写入。

4.4 读操作

选择控制寄存器并设置读写位为‘1’,读取状态寄存器的值。

5. 存储/恢复操作

5.1 自动存储

启用自动存储功能需要在VCAP引脚连接电容,并将状态寄存器的ASE位设置为‘1’。当检测到掉电事件且VCAP低于VTRIP时,自动触发存储操作。

5.2 硬件存储

通过将HS引脚拉高至少THSPW时间,可以手动启动存储操作,同时触发状态寄存器写周期将EVENT位设置为‘1’。

5.3 自动恢复

上电时自动执行恢复操作,确保SRAM数据与EEPROM数据一致。

6. 确认轮询

在存储和恢复操作以及内部状态寄存器写周期期间,设备不会发送确认信号。通过发送启动条件和写控制字节进行确认轮询,判断操作是否完成。

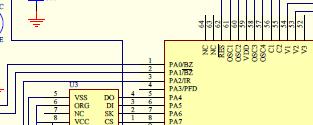

引脚描述

1. 电容输入(VCAP)

连接到47XXX的内部电源总线,使用自动存储功能时,需要连接电容以存储掉电时完成自动存储操作所需的能量。

2. 芯片地址输入(A1, A2)

用于多设备操作,通过不同的芯片选择位组合,最多可连接四个设备到同一总线。

3. 串行数据(SDA)

双向引脚,用于传输地址和数据,需要上拉电阻到VCC。

4. 串行时钟(SCL)

用于同步数据传输。

5. 硬件存储/事件检测(HS)

用于手动启动存储操作,并触发状态寄存器写周期将EVENT位设置为‘1’。

封装信息

提供8引脚PDIP、8引脚SOIC和8引脚TSSOP三种封装形式,每种封装都有相应的标记信息和尺寸规格。

总结

Microchip的47L04/47C04/47L16/47C16系列EERAM以其高可靠性、高速I²C接口、低功耗等特性,为电子工程师提供了一种优秀的非易失性存储解决方案。无论是工业控制、汽车电子还是其他对数据存储有较高要求的应用场景,该系列产品都能发挥出色的性能。在实际设计中,工程师们可以根据具体需求选择合适的型号和封装,充分利用其丰富的功能特性,提高系统的稳定性和可靠性。

大家在使用这款产品的过程中,有没有遇到过什么有趣的问题或者有什么独特的应用经验呢?欢迎在评论区分享交流。

发布评论请先 登录

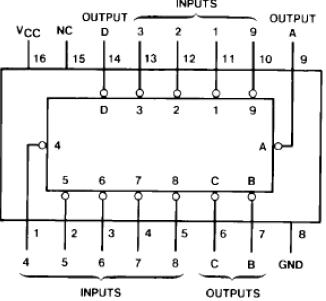

74hc47/74ls47/54LS47中文资料,数据手册

基于HT47C20L的R-F型低电压八位Mask单片机

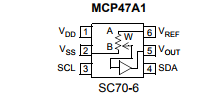

基于MCP47A1下的带命令编码的 6 位易失性 DAC

基于MCP47FVBXX带 / 双通道电压输出 易失性数模转换器

基于47L04/47C04/47L16/47C16下的4K/16K I2C 串行 EERAM

Microchip 47L04/47C04/47L16/47C16 EERAM:高可靠非易失性存储解决方案

Microchip 47L04/47C04/47L16/47C16 EERAM:高可靠非易失性存储解决方案

评论