高速先生成员--姜杰

高速先生前段时间分享过一篇文章《谐振威力,不容小觑》,介绍了平面谐振影响信号插损的案例。

细心的粉丝发现一个问题:案例中的器件布局在单板的TOP层,产生谐振的电源平面在L13层,如果说L13层以下的布线层,比如L18及L22层信号过孔穿过谐振腔,受到影响还能理解。

那么,对于背钻后的L9层和L11层的信号过孔,在Z轴方向上,明明离着谐振腔还有一定的间距,为什么插损也会受影响?

文字描述略复杂,看图一目了然。为了让大家看清楚Z轴方向的间距H,图中仅展示L9层信号走线、相应差分过孔,以及L13层的电源平面。

乍一看,信号路径与电源平面完全没有交集插损异常出现的没来由,分析无从下手……

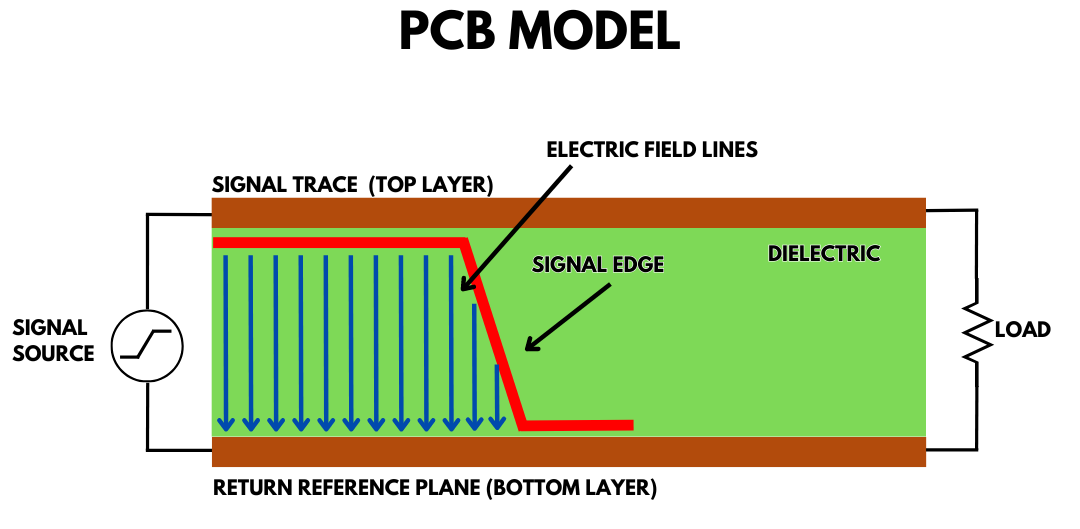

如果能换个角度,比如,电磁场的分布,问题便会迎刃而解。

信号传输过程中场的分布如下,答案就在其中!

给关键位置来个怼脸特写:

所以,真实的情况是,看似毫无关联的信号路径与电源平面,实际通过电磁场暗通款曲。

接下来,高速先生将通过仿真对比,展示信号插损跌落从无到有的过程,从而说明信号路径与电源平面间距的影响。

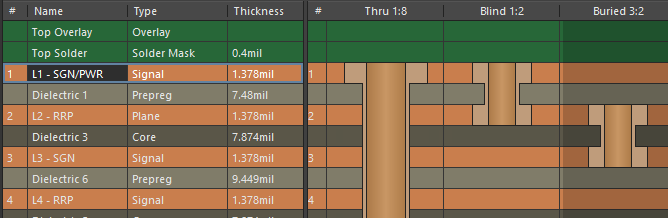

这次选择的仿真对象是L7层信号(对应过孔下端的蓝色走线层面),如果大家还有印象的话(没印象可以直接翻看文初第一个图),该层走线的插损最初是没有异常跌落的。模型调整的是原本位于L13层电源平面(图中紫色高亮)的层面。同时,为了减少变量,让结论更清晰,模型中的过孔stub全部设置为0,直接上图:

插损仿真结果如下:随着电源平面与信号路径越来越近,插损异常跌落从无到有,并逐渐增大。

电场分布仿真结果反映了同样的趋势,随着电源平面与信号路径越来越近,电源平面上的电场强度逐渐增加。

看到这里,严谨的粉丝可能又会问了:过孔stub为0只是理想情况,实际stub长度到底有多大影响呢?

别急,我们保留L7层走线,L9层电源平面的模型(位于中间的L8层是GND平面)继续研究。

通过对比发现,随着stub长度的增加,插损跌落的幅度随之加大。这也从另一个角度说明,平面谐振腔距信号路径(虽然过孔stub是我们极力避免的,但也是信号路径的一部分)越近,对信号产生的影响也越大。

综上,平面谐振对信号插损的影响,并非只存在于信号路径穿过谐振腔这一种情况——即便两者在Z轴方向有一定间距,通过电磁场的隔山打牛,依然可能会引发插损异常。

关于一博:

一博科技成立于2003年3月,深圳创业板上市公司,专注于高速PCB设计、SI/PI仿真分析等技术服务,并为研发样机及批量生产提供高品质、短交期的PCB制板与PCBA生产服务。致力于打造一流的硬件创新平台,加快电子产品的硬件创新进程,提升产品质量。

一博珠海板厂:

位于珠海经济开发区,坐拥PCB产业优质人才资源及完善的产业配套。专注于高端快件,提供高品质的高多层、高速、高精密、HDI等PCB生产制造。聚焦国内高端快件细分市场,致力于推动国内PCB行业的技术进步,尤其是高速、高多层、高复杂PCB产品的快速交付,对应PCB广泛应用于ATE、AI算力、服务器、工控、通信、汽车、医疗设备等领域。

审核编辑 黄宇

-

电磁

+关注

关注

15文章

1209浏览量

54163 -

PCB

+关注

关注

1文章

2347浏览量

13204

发布评论请先 登录

电磁炉方案浅析

EMC电磁屏蔽原理解析:什么是波阻抗?

单片机系统的电磁兼容性(EMC)设计

PCB板上PIN DELAY单位错了,DDR4跑不起来,真的吗?

2026年度《PCB板电磁兼容设计与评审方法》课程来袭!

干货分享 I PCB设计电磁兼容问题交流与解答(二)

PCB设计中的“隐形障碍”:电磁兼容问题的终极解析

PCB 层数设计与电磁兼容(EMC)

改善EMC的PCB设计原理

北京 12月5-6日《PCB板电磁兼容设计与评审方法》公开课报名中!

电磁干扰抑制:PCB板滤波器如何滤除高频噪声

标准电阻器不接PCB的地,电阻测量结果就波动大

信号如何在PCB中传播

遇事不决,PCB电磁绝学

遇事不决,PCB电磁绝学

评论