1

赛题背景分析

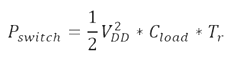

低功耗设计是数字系统非常重要的考虑因素。为了支持低功耗设计,首先要对功耗进行计算。功耗可分为静态功耗(漏电流引起)和动态功耗(门翻转引起)。在本赛题中,我们主要考虑动态功耗的计算方法。 动态功耗的计算公式如下: 其中,VDD为电压,C为等效电容,Tr为翻转率,即单位时间内逻辑门从0→1或从1→0的翻转次数。我们可以把电压和等效电容近似视为常数,对于不同的电路负载,统计其Tr,就可以计算动态功耗。

这道赛题的目的,就是让大家通过VCD文件来统计一个电路负载的翻转率。

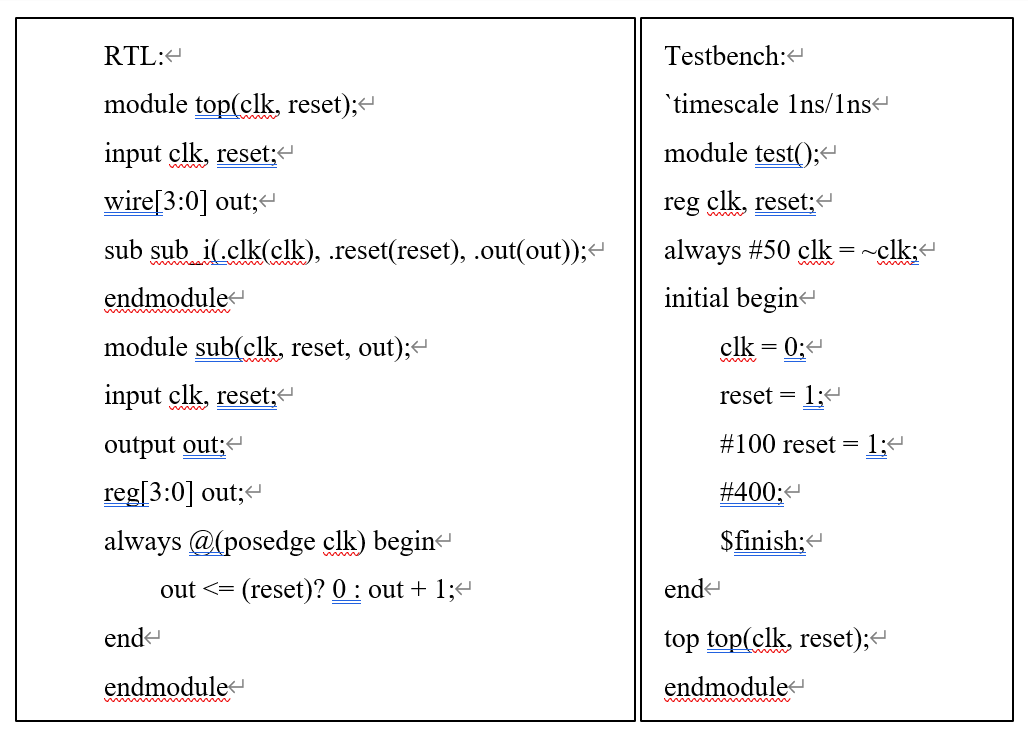

如何得到翻转率呢?我们回顾一下,在电路设计的时候,先设计其RTL(如verilog)代码,并编写testbench给出激励进行测试,如下所示:

其中,VDD为电压,C为等效电容,Tr为翻转率,即单位时间内逻辑门从0→1或从1→0的翻转次数。我们可以把电压和等效电容近似视为常数,对于不同的电路负载,统计其Tr,就可以计算动态功耗。

这道赛题的目的,就是让大家通过VCD文件来统计一个电路负载的翻转率。

如何得到翻转率呢?我们回顾一下,在电路设计的时候,先设计其RTL(如verilog)代码,并编写testbench给出激励进行测试,如下所示:

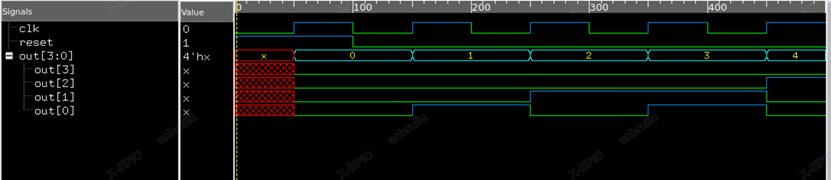

用常见的仿真工具跑如上RTL代码和testbench,可得到如下的输出结果波形:

用常见的仿真工具跑如上RTL代码和testbench,可得到如下的输出结果波形:

信号变化波形图(芯华章科技股份有限公司-Fusion Debug 提供)

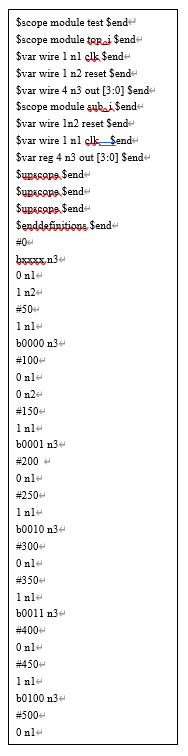

仿真工具可以把上述波形输出VCD文件,类似:

信号变化波形图(芯华章科技股份有限公司-Fusion Debug 提供)

仿真工具可以把上述波形输出VCD文件,类似:

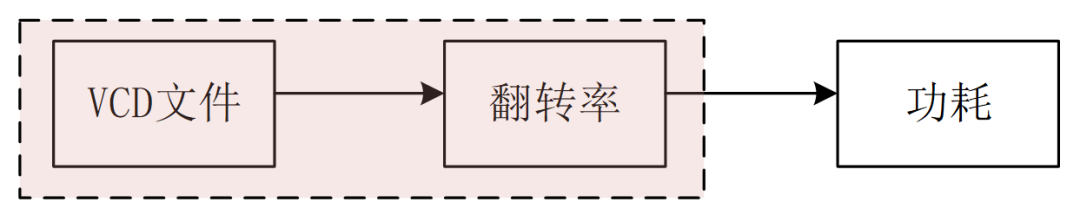

好,现在重点来了。给定VCD文件(其实就是波形的文本表示),我们就可以统计翻转率,进而利用上述的功耗公式来计算动态功耗,它们之间的逻辑关系如下图:

好,现在重点来了。给定VCD文件(其实就是波形的文本表示),我们就可以统计翻转率,进而利用上述的功耗公式来计算动态功耗,它们之间的逻辑关系如下图:

在本赛题中,我们只关注如何从VCD文件(对应波形)到翻转率的解析。

在本赛题中,我们只关注如何从VCD文件(对应波形)到翻转率的解析。

2

赛题要点解析

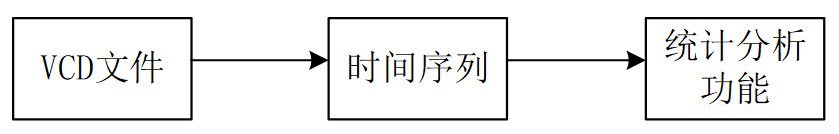

本赛题主要就是进行VCD文件的解析,然后根据题目的要求,得到不同的统计结果(如翻转次数tc,信号逻辑值为1的时间t1, 信号逻辑值为0的时间t0,信号逻辑值为x的时间tx,以及信号逻辑值为1的概率又称静态概率sp)、某个时间窗口的统计结果、不同层次信号的统计结果。 因此,首先需要定义一些数据结构表示信号时间序列,可以用数组或者vector等,将VCD文件读取、解析为这些信号时间序列变量,再针对这些变量进行统计分析,得到所需的输出。如下图所示:

2.1 VCD文件解析

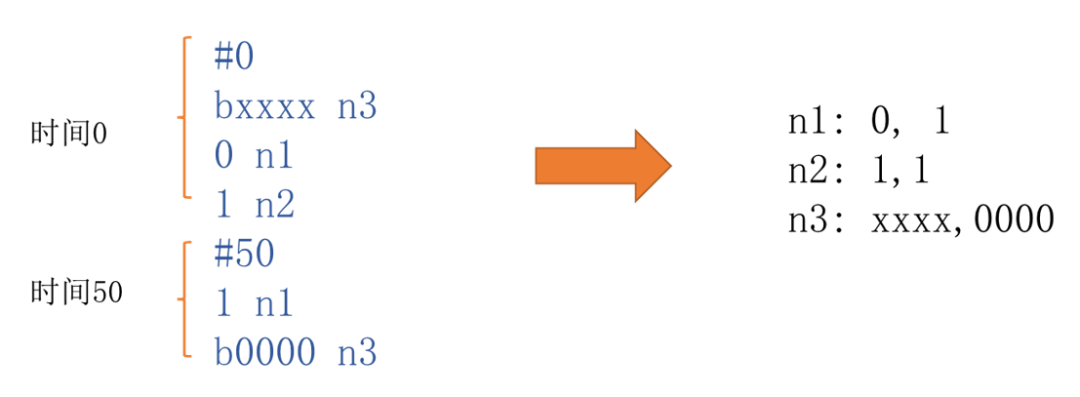

VCD文件解析的思路如下:-

首先扫描文件头,建立每个信号对应的数组或者vector。

-

将VCD文件看作是不同时间段的信号改变,对于一个时间段,扫描各个变量的值的变化,记录其变化,就构成了时间序列。

这样,扫描完一个文件之后,各个变量随时间变化的序列就存下来了。

这样,扫描完一个文件之后,各个变量随时间变化的序列就存下来了。

2.2统计输出

有了信号的时间序列值,可以根据题目要求打印统计结果。主要考虑几方面:-

翻转率等参数的计算,需要统计1和0的时间。

-

一个时间窗口的统计值,需要截取一个时间窗口进行计算。

-

层次化的信号,需要从文件中读取信号间的层次关系进行计算。

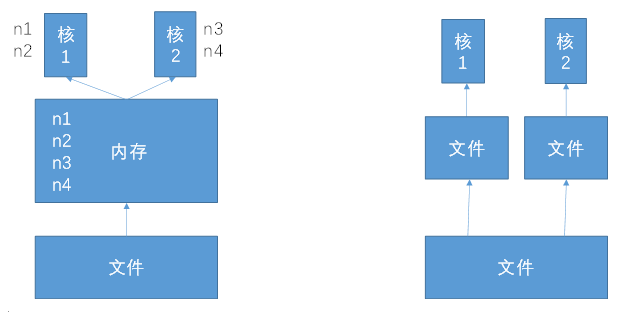

2.3多核加速

在题目要求中提到了多核加速,假如你的电脑有多个核,就可以用多线程方式加速。多核加速的本质是将任务划分到多个线程,让多个线程在多个核上同时运行从而提高计算速度。 加速方法有两种,一种是将文件读入到内存,然后将不同的行分配到不同的核/线程来处理,我们称之为横向划分;另外一种是将文件切分开分到不同的核,每个核处理文件的不同段,我们称之为纵向划分。 可以采用pthread或者openMP进行并行编程,需要注意线程间的同步和锁机制。

可以采用pthread或者openMP进行并行编程,需要注意线程间的同步和锁机制。

2.4文件处理

当VCD文件很大时,为了减少一次性读入占用太多内存,可以每次读入一部分文件存在内存中,如用getline等函数每次读一行等。3

建议解题步骤

1

对VCD的基本语法先熟悉一下,如信号名字的对应关系,每一行表示什么含义等。

2

实现VCD文件到信号时间序列变量的转换。这是一个文本逐行解析的过程。

3

写统计分析的模块,每个模块对应不同的统计需求,相对独立。

4

学习pthread或openMP多线程编程,学习如何创建线程、线程间如何同步、加锁等。

5

用pthread或openMP提高你的程序的效率,这里需要并行划分程序。

6

尝试一下不同的文件读取速度和占用内存情况,选择一个占用内存比较小的方式。

4

其它注意事项

大家在解题时还需要注意以下几点: 1)不要轻易放弃,题目本身难度不大,已经提炼成了算法题,前期的知识准备要花点时间; 2)一定要积极参加培训,很多知识其实一点就透;在没有相关背景积累的情况下学习会有一定的挑战性,但也可以补充很多知识; 3)要遵循循序渐进、从易到难的解题思路,切不可贪大求全让自己陷入到重重迷雾之中; 最后,预祝各位同学发挥出自己的水平,取得良好的成绩。 审核编辑 :李倩-

集成电路

+关注

关注

5446文章

12478浏览量

372780 -

电压

+关注

关注

45文章

5757浏览量

121053 -

等效电容

+关注

关注

0文章

18浏览量

8201

原文标题:芯华章赛题解析:数字集成电路动态功耗优化策略分析与评估

文章出处:【微信号:X-EPIC,微信公众号:芯华章科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

MCU时钟管理对功耗优化方向

MDD 逻辑IC的功耗管理与优化策略

华大九天Empyrean Liberal工具助力数字集成电路设计

新思科技携手深圳大学助力数字集成电路人才培养

电路设计异常要考虑:电流倒灌、热插拔、过流保护、过压保护、上电电流

中国集成电路大全 接口集成电路

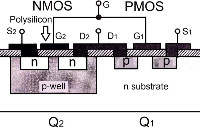

浮思特 | CMOS技术原理与应用:从晶体管结构到反相器设计

概伦电子集成电路工艺与设计验证评估平台ME-Pro介绍

集成电路设计中静态时序分析介绍

集成电路为什么要封胶?

数字集成电路 Verilog 熟悉vivado FPGA微电子、电子工程

新思科技携手深圳大学推动集成电路设计领域发展

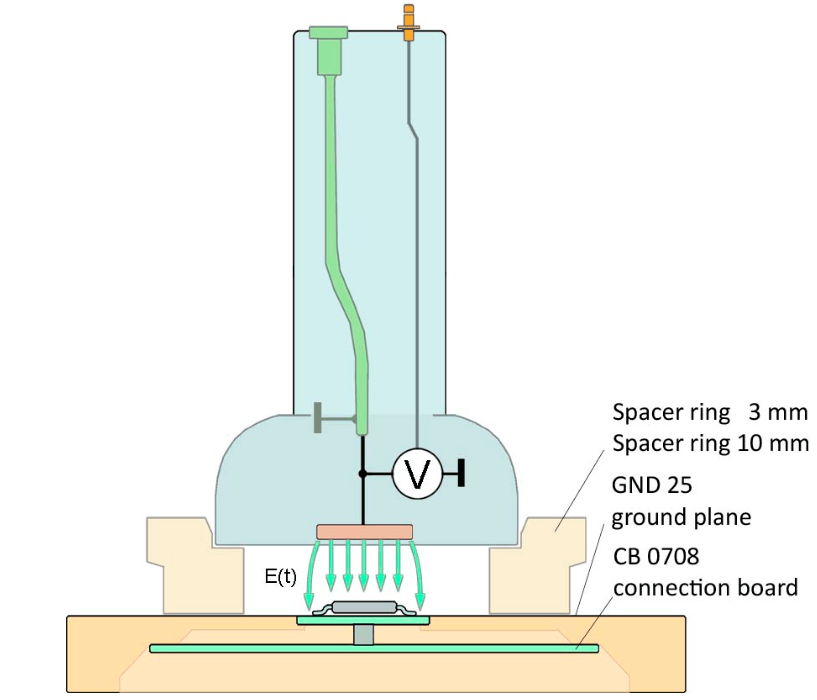

集成电路电磁兼容性及应对措施相关分析(三)—集成电路ESD 测试与分析

数字集成电路动态功耗优化策略分析与评估

数字集成电路动态功耗优化策略分析与评估

评论