碳化硅(SiC)凭借其优异的材料特性,在服务器、工业电源等关键领域掀起技术变革浪潮。本教程聚焦 SiC 尤其是 SiC JFET 系列器件,从碳化硅如何重构电源设计逻辑出发,剖析其在工业与服务器电源场景的应用价值。

我们已经介绍了碳化硅如何革新电源设计、工业与服务器电源。

本文为第二篇,将介绍三种替代 Si 和 SiC MOSFET的方案

SiC JFET、SiC Combo JFET、SiC Cascode JFET、SiC MOSFET的核心要点

SiC JFET

● 常开型

● 极低的导通电阻 RDS(on)

● 栅极偏置电压为 0V 时导通

● 栅极驱动电压范围:-20V至+2V

● 通过栅极电阻RG控制开关速度

SiC Combo JFET

● 常闭型

● 可独立访问 MOSFET 与 JFET 栅极

● 集成芯片温度检测功能

● 通过栅极电阻RG控制开关速度

● 通过施加 2V VGS和 1 mA 的正向偏置电流,对 JFET 的栅极进行过驱动,可使 RDS(on)进一步降低10–15%

● 可选通过 JFET 栅极控制开关速度

● 支持多 FET 器件并联

● 更适合低速开关应用

SiC Cascode JFET

● 常闭型

● 极低导通电阻 RDS(on),关断损耗极小

● 在 0V 时可作为电压阻断器

● 栅极驱动电压范围:0V至+12V,或使用缓冲电路时-5V至+20V(-3V至+18V时可实现最佳MOSFET性能)

● 可使用市售栅极驱动器,实现更灵活的栅极驱动

● 可通过外部 RG控制开关速度(有一定开关损耗),或使用缓冲电容 C 控制

● 具备优异的 MOSFET 体二极管特性,正向压降 VF 极低,反向恢复电荷QRR 极小

● 更适合高频开关应用

SiC MOSFET

● 常闭型

● 低导通电阻 RDS(on)

● 便于并联与速度控制

● 不具备温度自监测功能

SiC JFET 的驱动灵活性

SiC JFET 的驱动灵活性

在某些应用场景中,让半导体器件处于常开状态更为便利。右侧的电路图展示了一个典型示例:通过简单的过驱动方式实现可双向阻断的直接驱动电路。在此电路中,由于器件处于常开状态,即使没有栅极驱动电源,每个JFET也处于导通状态。利用市售的栅极驱动器可直接驱动每个JFET的栅极。

此处,每个JFET的开尔文源极端子与栅极驱动器的公共引脚 COM 相连,JFET的导通通过一个大阻值的栅极电阻 RODV实现,无需外部电压调节。可以将 RODV视为与 JFET 的栅-源二极管协同工作,共同构成其自身的稳压器。

假设在该电路中,栅极驱动器供电电压 VDD和 VSS为±15V,栅极电阻 RODV取值为1kΩ。当栅极电流处于毫安量级时,JFET 的栅-源电压 VGS在室温条件下约为2.3V。栅极驱动电流可通过以下公式进行近似计算:

栅极驱动电流约为12.5 mA,即每个JFET栅极约6.25 mA。由此可得,栅极驱动的功耗为15 V × 12.5 mA = 0.19 W。正是如此低的功耗,既实现了更低的导通电阻(RDS(on)),又保证了良好的片上温度检测功能。仅需1 mA的电流就足以对JFET栅极提供正向偏置,进一步降低RDS(on);而进行温度检测时,也仅需5至10 mA的电流即可轻松实现。

自对准沟槽沟道如何实现最低电阻率

与包括SiC MOSFET和超结(super-junction,SJ)MOSFET在内的所有其他半导体技术相比,安森美(onsemi)第四代SiC JFET和Cascode JFET,是迄今为止在任何给定击穿电压下最接近理论最小导通电阻(即所谓的单极极限)的器件。

这主要得益于安森美革命性的半导体制造工艺。通过采用自对准沟槽沟道(self-aligned trench channel)制造技术,栅极结构能够自动与源极和漏极精确对齐,从而有效缩小漂移区。正是这种制造工艺,使得器件具备了低导通电阻(RDS(on))、高阻断电压、更强的电流承载能力以及更快的开关速度,同时还拥有正温度系数,便于并联使用。

垂直型JFET截面图

极低的单位面积导通电阻

SiC JFET带来的最具影响力的优势或许是降低总成本,这主要源于两个关键因素:更小的PCB占用面积和发热量大幅减少。这一优势使SiC Cascode JFET相比SiC MOSFET具有巨大优势。

SiC JFET的单位面积导通电阻(RDS(A))约为SiC MOSFET的一半,仅为低压硅(Si)MOSFET的约10%。这不仅提升了系统性能,也带来了成本优势。

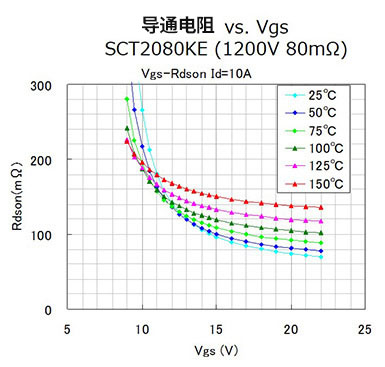

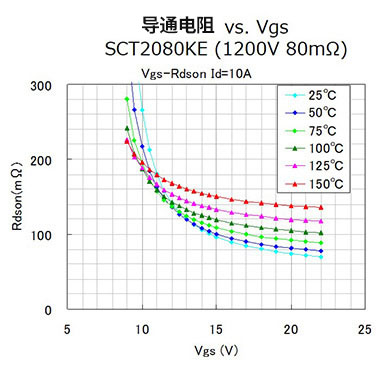

在对比导通电阻随温度变化的曲线时,尽管第四代(Gen4)SiC JFET的电阻-温度曲线斜率比某些其他工艺更陡,但其 RDS(A)的优势仍然超过2倍。

JFET 是如何正常工作

第一象限开关时序

由于JFET是常开型器件,需要对栅极驱动施加负电压才能将其关断并阻断高压(包括电压尖峰)。在所谓的JFET工作“第一象限”期间,当电压向0V增加时,器件开始导通。施加正的漏源电压 VDS会使漏极-栅极PN结反向偏置,导致其耗尽区扩展。如果 VDS持续增加,直至耗尽区填满整个沟道,JFET将进入“饱和”状态,沟道被“夹断”,电流不再随 VDS的增加而增大。

施加正的栅源电压(VGS)会使漏极-栅极和栅极-源极之间的PN结处于正向偏置状态,导致耗尽区收缩并抑制其扩展。正如我们将看到的,根据工作条件的不同,施加正的 VGS是降低导通电阻的简易方法。

由于SiC JFET的栅极由栅极-源极和栅极-漏极之间的PN结构成,无需额外的栅极氧化层屏蔽结构。这不仅避免了增加导通电阻,还从根本上消除了栅极氧化层的可靠性问题。此外,JFET不存在漏极-源极输出电容,其全部输出电容都存在于漏极与栅极之间,因此有:COSS= CRSS。这一特性使得JFET的开关速度可以通过简单调节栅极电阻(RG) 来精确控制。

进一步降低JFET导通电阻

下方图表展示了安森美UJ4N075004L8S SiC JFET在25°C环境温度(上图)和175°C(下图)下的输出特性曲线。当栅源电压 VGS为 -5 V 时,其沟道宽度被耗尽区完全夹断,器件处于完全饱和状态,电流受到限制。

将 VGS提升至-4V可使耗尽区收窄、导电沟道变宽,从而增加导电性并降低导通电阻。在此“Active”区内,增大 VDS会扩展耗尽区,但此时电流随 VDS的增加已不再显著上升,导致输出特性曲线发生弯曲。

图表中蓝色虚线左侧区域对应所谓的“ohmic ”区,该区域右侧蓝线之外才进入“Active”区或线性区。在“ohmic ”区内,随着栅源电压 VGS的升高,电导率增加,电阻下降。当 VGS达到 0V 时,JFET 完全导通,漏极与源极之间的电流沟道完全开启。若在此基础上将 VGS继续提升约2V,导通电阻 RDS(on)可进一步降低达 15% 。

安森美UJ4N075004L8S 750 V, 4.3 mΩ JFET

最大化JFET开关效率

第三象限开关时序

在过去,JFET没有固有体二极管常被视为一种缺陷。但在现代功率应用中,这反而成了一项优势——尽管要充分发挥这一优势需要一定的设计技巧,尤其是在反向导通阶段,即工程师所称的“第三象限”操作中。

上方的一组平面示意图展示了一个处于反向偏置状态的安森美第四代 JFET,其栅源电压 VGS为 -15V。虽然该 JFET 在第一象限可阻断数百伏电压,但其在第三象限的阻断电压能力相对有限,更多取决于漏极-栅极二极管与栅极-源极二极管的偏置状态,而非温度。左图中,漏源电压 VDS为 -3V。

此时 VGS与 VDS之间的差值为 -12V,低于阈值电压 VG(th) ,因此沟道完全阻断,无源极-漏极电流通过。当 VDS降至 -9V 且差值减小至 -6V 时,沟道略微开启,允许微小电流通过。在右图中,当差值达到 -4V(超过阈值电压2V)时,源极-漏极电流得以更自由地流动。

当 VDS低于阈值差值时,JFET 在第三象限的阻断能力通常受限,而这也正是 JFET 快速开关能力发挥作用之处,该特性使得“死区时间”能被尽可能缩短。

片上温度检测

由于JFET的栅源电压 VGS会随温度变化,因此向栅极注入一个微小的正向偏置过驱电流(范围在1 mA至5 mA之间),即可通过外部电路(例如放大器)轻松测量JFET的结温 TJ。该过驱电流会在栅源之间的二极管上产生一个压降,而此压降能以高度可预测的方式反映结温 TJ。通过测量 VGS压降,即可依据公式推导出 JFET 的温度。

类似地,利用结温 TJ作为关键变量,通过测量漏源电压 VDS即可获得可靠的电流值。该方法采用两个相同的高压阻断二极管 D1 和 D2 ,与 JFET 的漏极串联连接。当结合使用栅极驱动器退饱和保护(DESAT)引脚时,可经由这两个二极管提供一个微小电流(范围在毫安至微安级别)。或者,也可从栅极驱动电源通过一个电阻提供该小电流。

在这两种情况下,您都需要对二极管 D1 进行钳位,并跨接一个放大器,以测量该二极管两端的压降。此压降即代表 JFET 的漏源电压 VDS。既然已知芯片温度就能轻松估算其导通电阻 RDS(on),您便可直接运用欧姆定律来估算漏极电流,而无需使用额外的传感器:

实现最佳导热性能

随着裸芯尺寸不断缩小,以及单位面积导通电阻 RDS(A)(即每单位面积的 RDS(on))持续降低,确实会带来热管理方面的挑战。安森美通过在其制造工艺中引入银烧结(silver sintered)裸片贴装技术来应对这一挑战,替代传统的含铅焊料贴装方式。银烧结材料的热导率最高可达传统焊料的六倍。

左侧重叠的阴影矩形代表三款安森美器件在印刷电路板(PCB)上所占用的相对面积:第四代 750 V SiC JFET(蓝色)、第四代 750 V SiC MOSFET(深灰色)和第三代 650 V SiC MOSFET(浅灰色)。尽管第四代 MOSFET 的芯片面积比 JFET 大出 40%,其导通电阻反而略高,且结到外壳的热阻 RθJC也稍大——这正是由于该 MOSFET 仍采用传统的焊料贴装工艺所致。当然,更小的裸片尺寸确实也影响了结到环境的热阻 RθJA,尤其是封装外壳到周围环境散热的角度。

未完待续,后续推文将介绍SiC Cascode JFET等特性。

-

MOSFET

+关注

关注

151文章

10759浏览量

234832 -

安森美

+关注

关注

33文章

2131浏览量

95808 -

JFET

+关注

关注

3文章

202浏览量

23544 -

SiC

+关注

关注

32文章

3847浏览量

70067

原文标题:碳化硅赋能浪潮教程:替代Si 和SiC MOSFET的方案

文章出处:【微信号:onsemi-china,微信公众号:安森美】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

为何使用 SiC MOSFET

SiC-MOSFET与Si-MOSFET的区别

Si-MOSFET与IGBT的区别

SiC-MOSFET有什么优点

SiC功率器件SiC-MOSFET的特点

SiC MOSFET SCT3030KL解决方案

浅析SiC-MOSFET

SiC-MOSFET器件结构和特征

SiC-MOSFET与Si-MOSFET的区别

SiC-MOSFET与Si-MOSFET的区别

介绍三种替代Si和SiC MOSFET的方案

介绍三种替代Si和SiC MOSFET的方案

评论