今年3月份,赛灵思(Xilinx)历史上第四位全球CEO Victor Peng 先生在北京正式宣布赛灵思将推出“自适应计算加速平台”ACAP。Victor 表示:“作为可以和CPU、GPU与FPGA 相提并论、并且性能远超后二者的产品,ACAP可以覆盖更加广泛的应用,帮助人们实现智能互联并且驱动自适应的世界。”

ACAP采用台积电7纳米技术,在机器学习的计算能力方面比16纳米级提升20倍,在5G通信方面能够支持4倍的带宽,在性能功耗比方面具有优越的表现。ACAP是赛灵思公司“Everest 行动”(内部称为“珠穆朗玛”行动)的重大成果。“Everest 行动”已经历经四年,投资10亿美元、动用1500名工程师,无疑是一个重磅级新型产品。可以说,ACAP的问世,对业界来说是一项重大的技术颠覆,也是自赛灵思公司发明FPGA以来最卓著的工程成就。

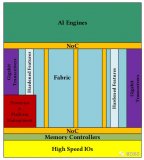

图1 ACAP架构图

上图中的所有其他主要模块都以某种形式在Xilinx 16nm Zynq、Virtex和Kintex UltraScale+系列中出现过,并不需要详细说明。这些模块包括Arm应用和实时处理器、可编程逻辑、HBM(高带宽存储器),使用硅基板和2.5D组装技术连接到Xilinx芯片上的堆叠式DRAM阵列、RFADC和DAC以及高速SerDes端口。

但是那个红色模块仍是个谜。这是公司“七面纱之舞蹈”的一部分,它会慢慢揭开Everest 和ACAP产品的细节,从而在设计阶段就引起公众的兴趣。(这种营销技巧的灵感来自于一个世纪前的著名作家和剧作家奥斯卡·王尔德,目前这种技巧受到了高科技营销人员和真人秀明星的青睐。)

8月份在加利福尼亚州库比蒂诺举行的“Hot Chips 30”会议上,揭开了一两个隐藏着HW和SW可编程引擎的神秘的面纱被揭开。在会议上,Xilinx集团工程总监Juanjo Noguera做了一份详细报告,标题为“HW/SW可编程引擎:Everest项目的特定架构”。Noguera的演示介绍了许多额外的硬件细节,同时保留了最有趣的细节。

Everest HW/SW可编程引擎是由粗粒度、软件可编程的VLIW矢量处理器组成的平铺阵列(tiled array),它们以多种硬件可编程的方式相互连接。Noguera认为,VLIW矢量处理器可以处理各种定点和浮点数据类型。HW/SW可编程引擎阵列出现在下图的左上角,而具有互连方案的单个模块细节位于图中的右下角。

图2 Xilinx HW/SW可编程引擎对Everest结构的详细说明

在Everest设计中,HW/SW可编程引擎阵列与PS(处理器系统)和PL(可编程逻辑)独立通信。阵列中的每个块的软件可编程VLIW向量处理器和数据移动器(DMA机器)组成。

阵列中有三种类型的互连链路模块。第一种类型,由图2中的红色小箭头表示,是使用NSEW(北、南、东、西)排列方法将每个模块与其最近的四个邻居链接起来的平行、双向数据接口。此外,图中显示的绿色小箭头指向的是单向级联接口,允许一个瓦片将部分结果直接传递给其相邻的右侧邻居。

这些短的、本地的点到点的连接让人想起FPGA阵列中用于的短距离LUT-to-LUT通信的本地互连,其级联接口类似于DSP片之间的进位接口。不过这并不是巧合,因为这些通信路径在Xilinx设备中一直很常见。

对于平铺阵列中较长的通信路径,HW/SW可编程引擎使用200G字节/秒的非阻塞、确定性NOC(片上网络)。NOC加上并行的本地互连,构成了可编程引擎的“硬件可编程”性。

我们可以以多种方式连接向量处理块,以实现不同的处理阵列。Noguera在他的演讲中讨论了五种类似的结构。图3列出了这些示例:

图3 Everest HW/SW可编程引擎处理配置示例

配置1是一个简单的一维单向数据流管道。每个处理块处理传入的数据流一部分,然后通过本地内存缓冲区将结果传递到下一个块。配置2是一个数据流图,该数据流图可以看成是数据流管道的多维版本。从本质上讲,它仍然是管道,不过是在多个维度上运行的。配置3利用NOC将结果从一个处理块同时多播到两个或多个后续块。配置4使用输入和输出存储器缓冲区来匹配连接在NOC上的块的差分处理速率。配置5可以使用级联接口将中间结果从一个块传递到下一个块,而不消耗其他资源。

这只是五个配置示例。使用这种新的处理资源可以创造出更多的处理配置,而且还有一些智能自动化的空间可以合成和优化配置,以满足高性能、高功率的目标。当然,这些互连方案也可以组合使用。

HW/SW可编程引擎的功能可以使用Everest的片上PL进行扩展,该PL通过多个NOC节点和CDC(时钟域交叉)缓冲区连接到HW/SW可编程引擎的NOC上,如图4所示。(显然,该架构需要CDC缓冲区,因为HW/SW可编程引擎和PL的时钟速率不同,不过它的运行速度应该不会变慢。)

图4 HW/SW可编程引擎的NOC通过多个NOC节点和时钟域交叉缓冲区连接到设备的可编程逻辑。

如图所示,Everest的HW/SW可编程引擎(图中缩写“PE”)与其PL之间的互连总带宽为Tbytes/sec量级。这将导致许多系统架构师不得不重新思考他们关于处理器体系结构的假设。

我们可以使用连接的PL以多种方式增强HW/SW可编程引擎的能力。例如,可以使用PL的RAM阵列来增加向量处理块对PL中的片上SRAM (BRAM和UltraRAM)块的访问。也可以使用PL来实现硬件加速器,它可以比块矢量引擎更快地执行特定的计算。Noguera建议使用PL为tile创建“ISA扩展”,但他没有详细说明。

机器语言推理和5G无线信号处理的性能结果给人留下了深刻印象,如下图5所示。

图5 HW/SW可编程引擎相对于可编程逻辑实现的结果。

值得注意的是ML(机器语言)推理的20倍改进。当涉及到ML推理时,FPGA已经相当快,因为推理计算涉及许多乘法和加法。FPGA中的数以千计的DSP片可以快速地执行这些计算,但是HW/SW可编程引擎似乎更快。Noguera说,5G无线处理中的4倍改进也很重要,因为这意味着珠穆朗玛峰架构可以达到2G./sec的传输速率。

在Noguera演讲后的问答环节中,听众提出了一些详细的问题。第一个问题是关于HW/SW可编程引擎的时钟速率。Noguera的回答是,他还不能直接回答这个问题,但是他试图通过声明引擎可以处理2G./sec的5G传输比特率来间接回答。他说,HW/SW可编程引擎处理器的工作频率将是“千兆级”。

另一个问题涉及HW/SW可编程引擎阵列中的模块数量。答案是每个HW/SW可编程引擎中将有数十到数百个模块,这取决于设备构成。ACAP设备的HW/SW可编程引擎中有数百个矢量处理器,它们将被大规模并行化。这个范围与所有FPGA供应商(包括Xilinx)在广泛的设备家族中将不同数量的资源放置到单个成员中的方式非常一致,并且它传达了Xilinx开发ACAP设备家族的意图。

然而,第一款Everest设备还没有出来。这一里程碑性的计划将于今年晚些时候实现。同时,七个面纱的舞蹈还在继续。Noguera承诺将在今年晚些时候在圣何塞、北京和法兰克福举行的Xilinx开发者论坛上披露更多细节。

-

FPGA

+关注

关注

1655文章

22283浏览量

630285

原文标题:秒杀GPU:FPGA发明以来最伟大的技术详解

文章出处:【微信号:SSDFans,微信公众号:SSDFans】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

从FPGA到ACAP,赛灵思再次超越自我

基于7nm工艺的FPGA加速芯片-ACAP

ME结构在FPGA加速芯片ACAP有何作用

勇敢的芯板你玩转Altera FPGA

【AD新闻】赛灵思新CEO访华绘蓝图,7nm ACAP平台要让CPU/GPU难企及

ACAP的主要架构创新解析

【年度精选】2020年度TOP10榜单——FPGA技术社区问答

晶体管发明史

三张图解析FPGA/ACAP在AI推理中的优势

二十世纪最伟大的发明之一--半导体激光器

揭秘赛灵思计算平台ACAP技术细节

FPGA发明以来最伟大的技术ACAP解析

FPGA发明以来最伟大的技术ACAP解析

评论