AD6643双中频接收器:高性能与低功耗的完美结合

在当今的电信应用中,对于多天线系统的需求日益增长,这就要求相关的硬件设备具备高动态范围性能、低功耗和小尺寸等特点。AD6643双中频(IF)接收器就是这样一款专门为满足这些需求而设计的产品,下面我们就来详细了解一下它的特性、性能以及应用。

文件下载:AD6643.pdf

产品概述

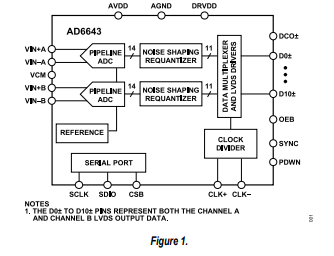

AD6643是一款11位、200 MSPS/250 MSPS的双通道中频接收器,它集成了两个高性能的模数转换器(ADC)和噪声整形再量化器(NSR)数字模块。其设计旨在支持电信应用中的多天线系统,在高动态范围性能、低功耗和小尺寸方面表现出色。

产品亮点

- 紧凑封装:两个ADC封装在一个9 mm × 9 mm × 0.85 mm、64引脚的LFCSP封装中,节省空间。

- NSR功能:通过引脚可选的噪声整形再量化器(NSR)功能,在185 MSPS时可在高达60 MHz的降低带宽内提高信噪比(SNR)。

- LVDS接口:LVDS数字输出接口配置适用于低成本FPGA系列。

- 单电源供电:可从单个1.8 V电源供电。

- SPI接口:标准串行端口接口(SPI)支持各种产品特性和功能,如数据格式(偏移二进制或二进制补码)、NSR、掉电、测试模式和电压参考模式。

- 时钟灵活性:片上整数1 - 8输入时钟分频器和多芯片同步功能,支持广泛的时钟方案和多通道子系统。

性能指标

直流指标

AD6643的分辨率为11位,保证无丢失码。在精度方面,偏移误差最大为±10 mV,增益误差在不同型号和条件下有所不同。输入参考噪声在25°C时为0.614 LSB rms。模拟输入的典型值为1.75 V p-p,输入电容为2.5 pF,输入电阻为0.9 kΩ。电源电压AVDD和DRVDD的范围为1.7 - 1.9 V,不同工作模式下的电源电流也有所不同,例如在NSR禁用时,I_DRVD为154 - 215 mA。

交流指标

在信号与噪声比(SNR)方面,NSR禁用时,在不同输入频率下SNR可达65.3 - 66.6 dBFS;NSR启用时,22%带宽模式下在不同输入频率下SNR可达72.6 - 76.1 dBFS,33%带宽模式下SNR可达70.1 - 76.1 dBFS。信号与噪声和失真比(SINAD)、无杂散动态范围(SFDR)等指标也表现出色,例如在某些频率下SFDR可达92 dBc。

数字指标

时钟输入支持CMOS、LVDS、LVPECL等多种逻辑电平,内部共模偏置为0.9 V,差分输入电压范围为0.3 - 3.6 V p-p。同步输入(SYNC)和其他逻辑输入(如CSB、SCLK、SDIO等)也有相应的电压和电流要求。数字输出为LVDS,差分输出电压在ANSI模式下为250 - 450 mV,在降低摆幅模式下为150 - 280 mV。

开关和时序指标

输入时钟速率最高可达625 MHz,转换速率在不同型号下分别为200 MSPS和250 MSPS。数据传播延迟、DCO传播延迟、DCO到数据偏斜等指标也有明确规定。此外,还规定了同步时序和SPI时序的要求。

工作原理

ADC架构

AD6643采用双前端采样保持电路,后跟流水线式开关电容ADC。每个阶段的量化输出在数字校正逻辑中组合成最终的11位结果,也可以通过NSR模块进行处理。流水线架构允许第一阶段处理新的输入样本,其余阶段处理先前的样本,采样发生在时钟的上升沿。

模拟输入考虑

模拟输入是一个差分开关电容电路,设计用于在差分信号处理中实现最佳性能。在采样模式下,信号源必须能够在半个时钟周期内对采样电容充电并稳定。为了减少驱动源输出级所需的峰值瞬态电流,可以在每个输入串联一个小电阻,并在输入两端并联一个电容以提供动态充电电流。在中频欠采样应用中,应减少输入两端的并联电容。

电压参考

AD6643内置了稳定而准确的电压参考,可以通过SPI调整参考电压来调整满量程输入范围,ADC的输入跨度与参考电压的变化线性相关。

时钟输入考虑

为了实现最佳性能,应使用差分信号对AD6643的采样时钟输入(CLK+和CLK -)进行计时。时钟输入可以是CMOS、LVDS、LVPECL或正弦波信号,时钟源抖动是最需要关注的问题。AD6643具有灵活的时钟输入结构,包括输入时钟分频器和占空比稳定器(DCS),DCS可以提供标称50%占空比的内部时钟信号,减少时钟占空比对性能的影响。

功耗和待机模式

AD6643的功耗与采样率成正比。通过断言PDWN引脚或通过SPI端口,可以将其置于掉电模式,此时ADC通常消耗10 mW。在待机模式下,可以保持内部参考电路供电,以实现更快的唤醒时间。

数字输出

AD6643的输出驱动器可以配置为ANSI LVDS或降低驱动LVDS,使用1.8 V DRVDD电源。数据格式可以通过SPI控制选择偏移二进制、二进制补码或格雷码。数字输出使能功能(OEB)可以通过OEB引脚或SPI接口启用,当OEB引脚为低时,输出数据驱动器启用;当OEB引脚为高时,输出数据驱动器处于高阻抗状态。

噪声整形再量化器(NSR)

NSR功能允许在奈奎斯特频带的子集内保持高于11位的SNR,并且不影响接收器的谐波性能。NSR功能可以通过SPI独立控制每个通道,提供22%和33%两种带宽模式,每种模式下可以通过6位调谐字设置有用的频率范围。

通道/芯片同步

AD6643具有SYNC输入,允许用户灵活同步内部模块,确保多个ADC之间的同步操作。输入时钟分频器可以通过SYNC输入进行同步,可以设置为在单个SYNC信号或每个SYNC信号上同步。

串行端口接口(SPI)

SPI接口允许用户通过ADC内部的结构化寄存器空间配置转换器的特定功能或操作。通过SCLK、SDIO和CSB三个引脚实现读写操作,数据可以以MSB优先或LSB优先模式发送。SPI接口可以由FPGA或微控制器控制,但在需要转换器全动态性能的时期,SPI不应处于活动状态,以避免噪声影响转换器性能。

应用信息和设计指南

应用领域

AD6643适用于多种电信应用,如通信、分集无线电和智能天线(MIMO)系统、多模式数字接收器(3G)、WCDMA、LTE、CDMA2000、WiMAX、TD - SCDMA、I/Q解调系统和通用软件无线电等。

设计指南

- 电源和接地:建议使用两个独立的1.8 V电源,一个用于模拟(AVDD),另一个用于数字输出(DRVDD),并使用多个去耦电容覆盖高低频率。使用单个PCB接地平面,并进行合理的分区,以实现最佳性能。

- 暴露焊盘:必须将ADC底部的暴露焊盘连接到模拟地(AGND),并在PCB上使用连续的暴露铜平面,通过多个过孔实现最低的电阻热路径。

- VCM引脚:将VCM引脚通过0.1 μF电容接地,并在VCM引脚与通道A和通道B的模拟输入网络连接之间包含33 Ω电阻,以实现最佳的通道间隔离。

- SPI端口:在需要转换器全动态性能的时期,SPI端口不应处于活动状态,必要时可以在SPI总线和AD6643之间提供缓冲器,以防止信号在关键采样期间在转换器输入处转换。

总结

AD6643双中频接收器以其高性能、低功耗和小尺寸的特点,为电信应用中的多天线系统提供了理想的解决方案。其丰富的功能和灵活的配置选项,使得工程师可以根据具体应用需求进行优化设计。在使用过程中,遵循设计指南可以确保AD6643发挥最佳性能。你在实际应用中是否遇到过类似的高性能ADC呢?你对AD6643的哪些特性最感兴趣呢?欢迎在评论区分享你的经验和想法。

发布评论请先 登录

AD6643双中频接收器:高性能与低功耗的完美结合

AD6643双中频接收器:高性能与低功耗的完美结合

评论