本期为大家带来的是《雷达应用中射频转换器的无杂波电源(第 1 部分)》,介绍了一种基于低噪声电源管理架构的射频采样系统设计方案,以解决相控阵雷达和 5G 通信应用中因开关电源噪声耦合导致的 ADC 动态性能下降问题。

引言

寻找噪声源时,电源引脚也被视为输入,且所有有源器件都具有引脚。在当今的实际设计中,进行射频 (RF) 相关设计时应考虑电源引脚。任何电源输入端的噪声和耦合都会因额外的杂波而导致雷达应用中的性能不达标。

尽管本文的重点是数据转换器,尤其是在千兆赫兹频段中进行采样的射频转换器,但是此处讨论的原理适用于所有集成电路,包括低频或高频应用信号链中的全差分放大器、混频器、低噪声放大器、增益块、射频开关以及数字步进衰减器。

本质上,模数转换器 (ADC) 是一个巨型混频器;输入端的任何信号都将卷积到其输出频谱。任何输入都是如此。可假设“泄漏噪声”(也称为白噪声或杂散)仅来自时钟和/或模拟输入。但是,对于先进雷达系统之类的应用,开关模式电源 (SMPS) 也会泄漏噪声并严重破坏频谱性能。

进入系统板的高噪声总线轨电压会偏置 ADC 的各个部分,通常使用低压差稳压器 (LDO) 来降低该电压。但是,如需在组件尺寸和效率之间进行权衡,这并非更实用的方法。这种情况下,某些 SMPS 技术会更适合这些应用,它们对 SMPS 输出噪声具有更深刻的认知。

本系列由两部分组成,第一部分介绍当噪声耦合到 ADC 的电源时会发生的情况、噪声如何通过 ADC 的电路进行耦合以及一些常用的电源权衡。

电源噪声耦合

提供给 ADC 的带有噪声的采样时钟最终会对 ADC 性能造成灾难性影响。与此相关的论文有很多,因此下文仅是一种概括性的阐述。当认为时钟低于标准时,ADC 的信噪比 (SNR) 和噪声频谱密度将偏离其数据表规格。如图 1 所示,快速傅里叶变换频谱重叠图展示了抖动时钟与应用于 ADC 的纯净采样时钟之间的差异。请注意,使用低于标准的采样时钟时,SNR 会降低 ~3dB。这种下降会极大地减小系统的总动态范围。

图 1 带有噪声的采样时钟与纯净采样时钟之间的对比

图 2 与时钟输入的 ADC 输出频谱耦合的宽带噪声或近端噪声

为了进一步说明这一点,如果时钟具有任何宽带噪声或近端噪声,则这两种噪声都会在输出频谱中占据很大分量。图 2 中展示了这一点。此前,建议将 ADC 视为巨型混频器;即使 ADC 处于理想状态,仅以宽带或近端方式耦合到时钟的任何噪声最终都将卷积到输出频谱。

同样的概念也可应用于电源输入。如图 2 所示,通过将基频(fIN)同样的概念也可应用于电源输入。如图 2 所降低到 DC,DC 附近的任何宽带噪声或近端噪声都将卷积到输出频谱。请参见图 3。

图 3 与电源输入的 ADC 输出频谱耦合的宽带噪声或近端噪声

噪声通过时钟进行耦合的方式与噪声通过电源引脚进行耦合的方式略有不同。在时钟示例中,时钟节点的内部电路与模拟输入的采样保持结构紧密相连。因此,该位置是让通过时钟引脚耦合的任何噪声设法进入 ADC 内部信号路径的理想之选(如图 2 所示)。在此情况下,耦合路径几乎达到零衰减。

注意,图 4 所示的 ADC 内部电路包含一个衰减符号。此符号表示 ADC 对通过电源引脚耦合的任何噪声或信号的抑制(抑制程度以电源抑制比 (PSRR) 衡量)。最终,此衰减定义了 ADC 内部电路设计的耦合抑制量,即PSRR。某些电路设计拓扑能够比其他拓扑提供更少的噪声衰减,因此更多噪声将泄漏到 ADC 的数字化路径中,导致 ADC 性能降低。图 5 举例说明了两个不同的电路结构。

得益于连接到电源轨的高隔离度金属氧化物半导体结构,图 5a 中所示的结构类型可带来更好的噪声衰减和耦合效果(从而改善 PSRR)。采用简单的上拉电阻设计,图 5b 中的电路能够实现较小的噪声衰减。

寄生效应是区分良好和不良 PSRR 容差的另一个因素。目前,许多 ADC 设计以及许多其他器件中都采用更小的工艺几何尺寸和更低的电源电压范围。这些几何尺寸又会导致电压阈值变小,从而对噪声更敏感。

图 4 电源衰减耦合路径示例

图 5 连接到电源引脚的ADC 内部电路结构的通用示例

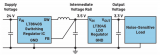

电源权衡:SMPS 与 LDO

高速 ADC 对电源噪声敏感,因此一种最大限度地减少噪声的主流方法是将开关模式电源 (SMPS)纳入设计方案 ,从而降低系统中有效的主总线轨电压(例如,28V 或15V)。SMPS 提供一个中轨电压,使 LDO 能够向相应的ADC 电源域提供纯净电压。请参阅图 6。

图 6 ADC12DJ5200RF 评估模块(EVM)的SMPS 和 LDO 设计

与线性电源相比,SMPS 设计具有若干优点。功率损耗的减少转化为更高效、更优的解决方案。整个电路板上众多 LDO 的电压降形成的功率损耗所带来的功率耗散会降低,同时整个 SMPS 电源电路的尺寸使得可用 PCB面积增大。单独使用 SMPS 时必须仔细考虑所选的开关电源、滤波和电路设计布局才能实现所要的结果,但这完全可以实现。请参阅图 7。

图 7 ADC12DJ5200RF EVM 的“仅 SMPS” 设计

ADC 的交流性能 (SNR/SFDR) 在两种电源设计之间处于同等水平,因为以 10.4GSPS 采样率进行采样时模拟输入频率为 1.5GHz 的。此基本测试令人相信 SMPS 设计是可靠,如图 8 所示。

图 8 ADC12DJ5200RF 交流性能比较

结论

功率 IC 设计中的新技术突破已让位于“仅 SMPS”方法,因此可将该方法运用于对噪声敏感的许多应用(例如雷达和高端仪器)。

本文使用了 TPS62913 低纹波和低噪声降压转换器来展示这些权衡之间的差异。此降压转换器经过专门设计,有助于让电源设计满足噪声敏感型高速应用对于噪声和纹波的要求。第 2 部分第后续文章将使用 12 位 ADC12DJ5200RF射频采样 ADC 来定义和测量 PSRR 和电源调制比,并举例说明了如何正确进行功率管理权衡。

-

射频

+关注

关注

106文章

6091浏览量

173819 -

电源管理

+关注

关注

117文章

8504浏览量

148224 -

adc

+关注

关注

100文章

7942浏览量

556859 -

模数转换器

+关注

关注

26文章

4099浏览量

130249 -

采样系统

+关注

关注

0文章

5浏览量

6112

原文标题:模拟芯视界 | 射频转换器的电源噪声抑制:实现无杂波雷达设计

文章出处:【微信号:tisemi,微信公众号:德州仪器】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

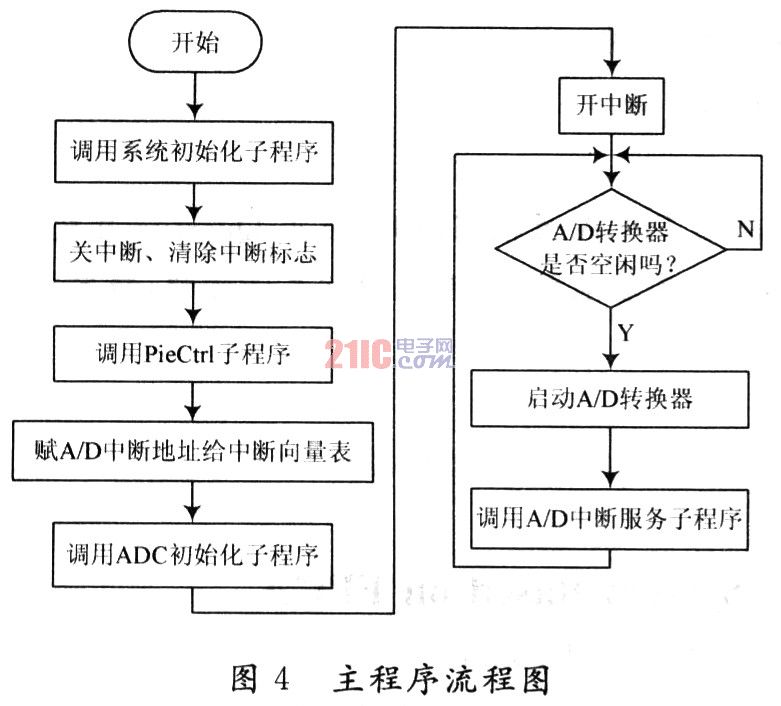

采用TMS320F2812变频电源的交流采样系统设计方案

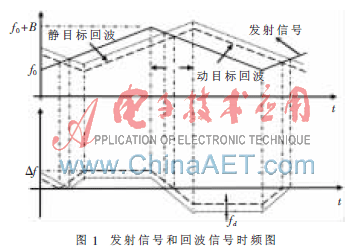

基于dsp防撞雷达信号采样系统设计

一种基于低噪声电源管理架构的射频采样系统设计方案

一种基于低噪声电源管理架构的射频采样系统设计方案

评论