文章来源:十二芯座

原文作者:Lychee

本文介绍了集成电路的背面供电技术的原理、类型、优势和挑战。

随着晶体管密度逼近极限,传统前端供电(Front-side Power Delivery)导致的 IR Drop(电压降)和布线拥挤已成为性能杀手。

BSPDN 通过将电力传输网(PDN)从晶圆正面移至背面,实现了信号与电力的物理分离。本文将基于四种演进路径,解析BSPDN.

背面供电(BSPD),也被称为背面供电网络(BSPDN)或背面供电过孔(BPV)技术,是一项半导体制造创新。它将芯片的主供电网络从晶圆正面(即晶体管和信号互连层所在的一侧)转移到了晶圆的背面。

这种方法能够实现更高效的电力传输,减少布线拥塞,并提升性能、能效和可扩展性——对于 2nm 及更先进的工艺节点而言,这一点尤为重要。

在传统的半导体设计中,电源轨和信号布线都是在晶体管层上方的正面金属层中实现的。随着特征尺寸不断缩小以及晶体管密度的增加,这些布线层变得日益拥塞,从而产生了电阻和电容瓶颈。

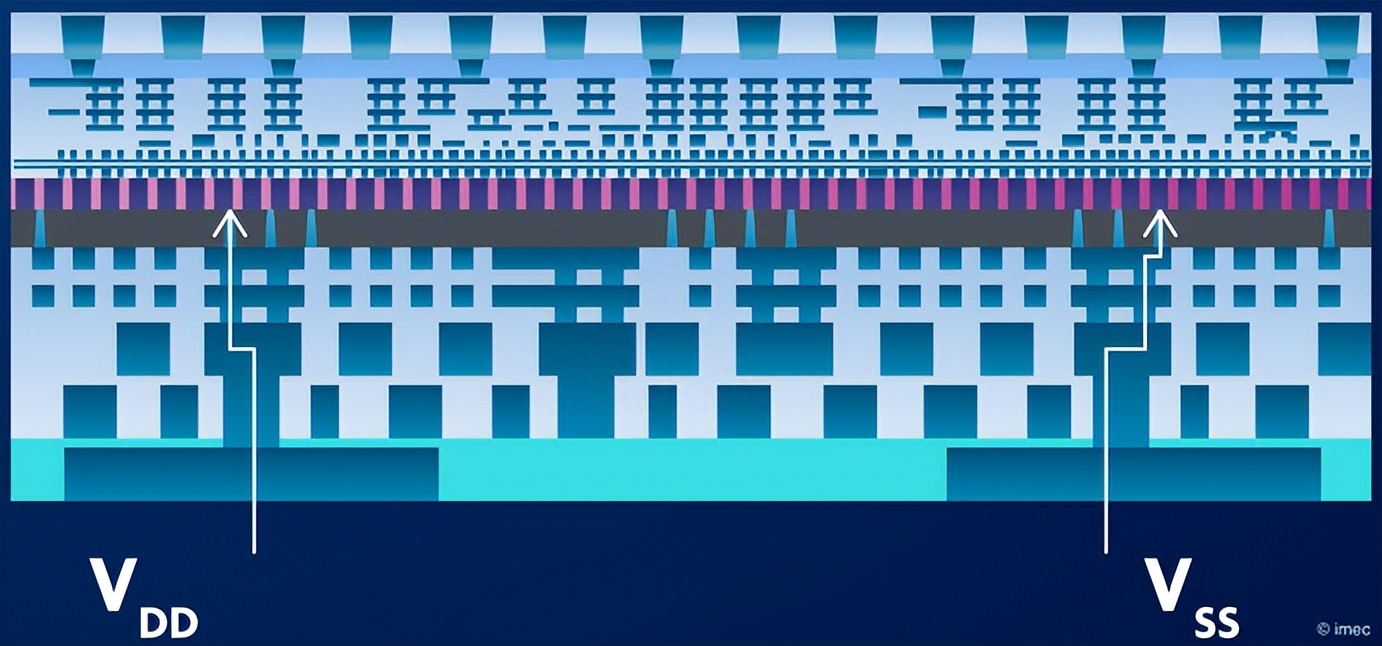

BSPDN 技术通过背面过孔(有时称为电源过孔)将电力直接从晶圆背面传输到靠近晶体管层的埋入式电源轨,从而实现了供电网络与信号网络的分离。

信号布线依然完全保留在正面,但这释放了金属走线资源,缩短了信号路径,并降低了延迟。

Different Types

背面连接从“间接”到“直接”的四个阶段,这代表了工艺复杂度的逐步提升和寄生电阻的持续降低。

1 Power Tap to M0

物理机制:这是最原始的形式。电力从背面金属层 (BS_M0) 通过粗大的硅通孔 (TSV) 传输到正面顶层金属,再逐层向下传递。

局限性:TSV 占用空间巨大(Micron 级别),严重阻碍了晶体管缩放,且路径过长,压降改善有限。

2 Power Via

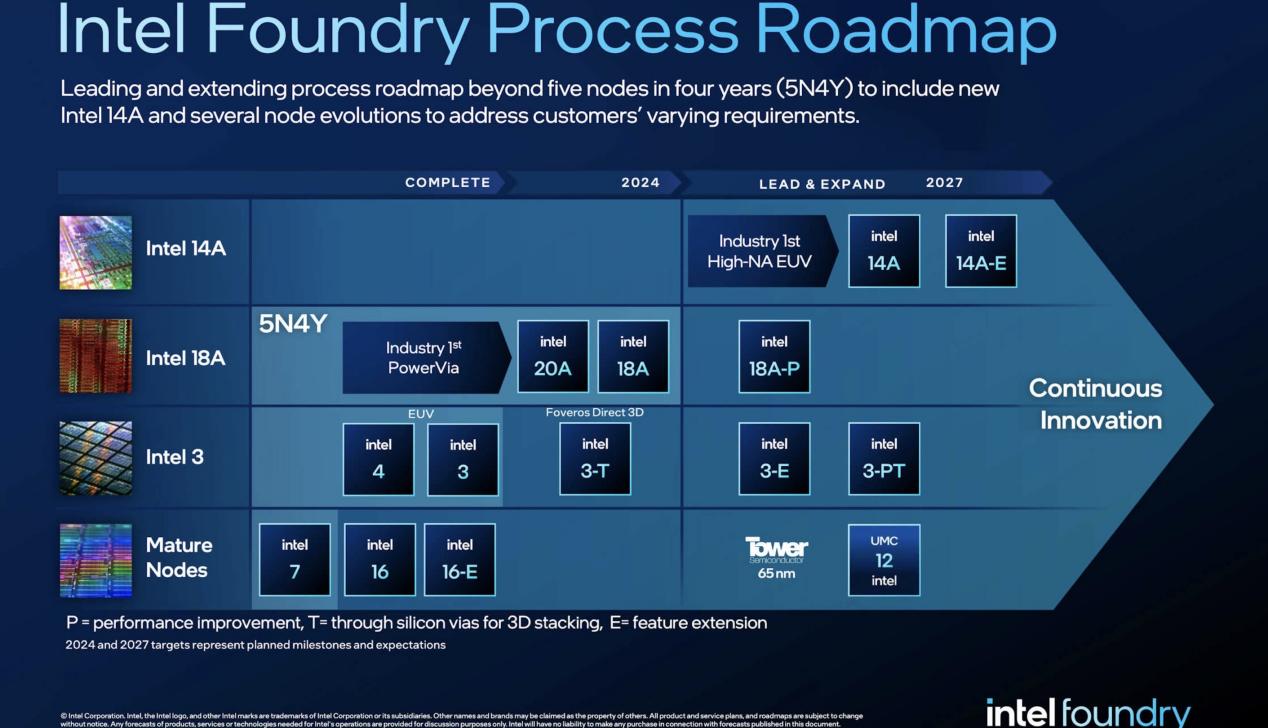

物理机制:这是目前 2nm 节点的主流方案(如 Intel PowerVia)。在晶体管下方埋入电源轨 (BPR),通过较小的垂直通孔 (PV) 直接与背面金属连接。

优势:大幅释放了正面金属层 (FS M0-M3) 用于信号布线。据 IMEC 数据显示,这种架构能带来 10% 以上的性能增益,主要源于布线拥挤度的降低。

3 Direct BS Contact to S/D

物理机制:这是更为激进的方案,背面通孔不再经过 BPR,而是直接接触 NanoSheet(纳米片)晶体管的源极/漏极 (S/D)。

挑战:这要求极高的晶圆减薄技术(需减薄至数百纳米以内)和精准的背面套刻(Overlay)精度。

4 Direct BS Contact to Gate

物理机制:极致的演进,背面金属直接驱动栅极 (Gate)。

应用场景:主要用于特定的逻辑控制或静态随机存储器 (SRAM) 单元优化,以实现极致的单元高度压缩。

关键技术优势

降低 IR 压降:电力通过从背面到晶体管的更短、更粗的金属路径传输,降低了电压降,从而允许更高且更稳定的工作频率。

释放正面布线资源:随着电源线移至背面,正面有更多的布线轨道可用于信号传输,从而减少了拥塞和导线长度。

提高能效:供电网络(PDN)电阻的降低以及信号线电容的减少,降低了整体功耗(包括静态功耗和动态功耗)。

更好的电源完整性:更低的电压噪声(电压暂降)允许减小电压保护带,从而提高性能和可靠性。

增强 3D 集成潜力:在 3D 堆叠和芯粒(Chiplet)系统中,为正面凸块/微凸块区域腾出了空间,可用于高密度的裸片间互连。

挑战与展望:晶圆减薄与散热

BSPDN 虽然解决了供电问题,但也带来了新的工程难题:

晶圆强度:背面加工需要将晶圆减薄到极致,这使得晶圆变得像纸一样脆弱,极易破碎,对载体晶圆键合 (Carrier Wafer Bonding) 工艺要求极高。

热失控风险:由于背面被大面积金属层覆盖,传统的散热路径被改变。因此系统级设计必须考虑如何在封装层中整合更高效的背面冷却方案。

-

集成电路

+关注

关注

5463文章

12669浏览量

375607 -

晶圆

+关注

关注

53文章

5445浏览量

132713 -

晶体管

+关注

关注

78文章

10434浏览量

148543

原文标题:背面供电网络 (BSPDN) 的架构革命

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

无线传感器网络技术及应用现状

如何优化供电网络?

智能电网的概念与网络技术架构

背面供电网络技术的架构革命

背面供电网络技术的架构革命

评论