电子发烧友网报道(文/周凯扬)对于任何试图将半导体工艺推进至埃米级的晶圆厂而言,GAA和背面供电似乎都成了逃不开的两大技术。GAA和背面供电在满足芯片性能标准的同时,进一步改善了功耗和面积,可以说是高端芯片下一轮实现PPA全面提升的关键。

目前绝大多数晶圆厂已经确定了GAA这一晶体管架构上改变,然而在背面供电何时投入应用上,头部三大晶圆厂却没那么坚定。背面供电技术可以有效改善供电线路的空间占用,并减少电力传输过程中造成的损失。照理说这种供电网络方式的改进应该大力普及,但绝大多数晶圆厂似乎都更愿意将这一技术推迟至2nm甚至更晚的节点上。

英特尔:率先实现背面供电,与RibbonFET同步

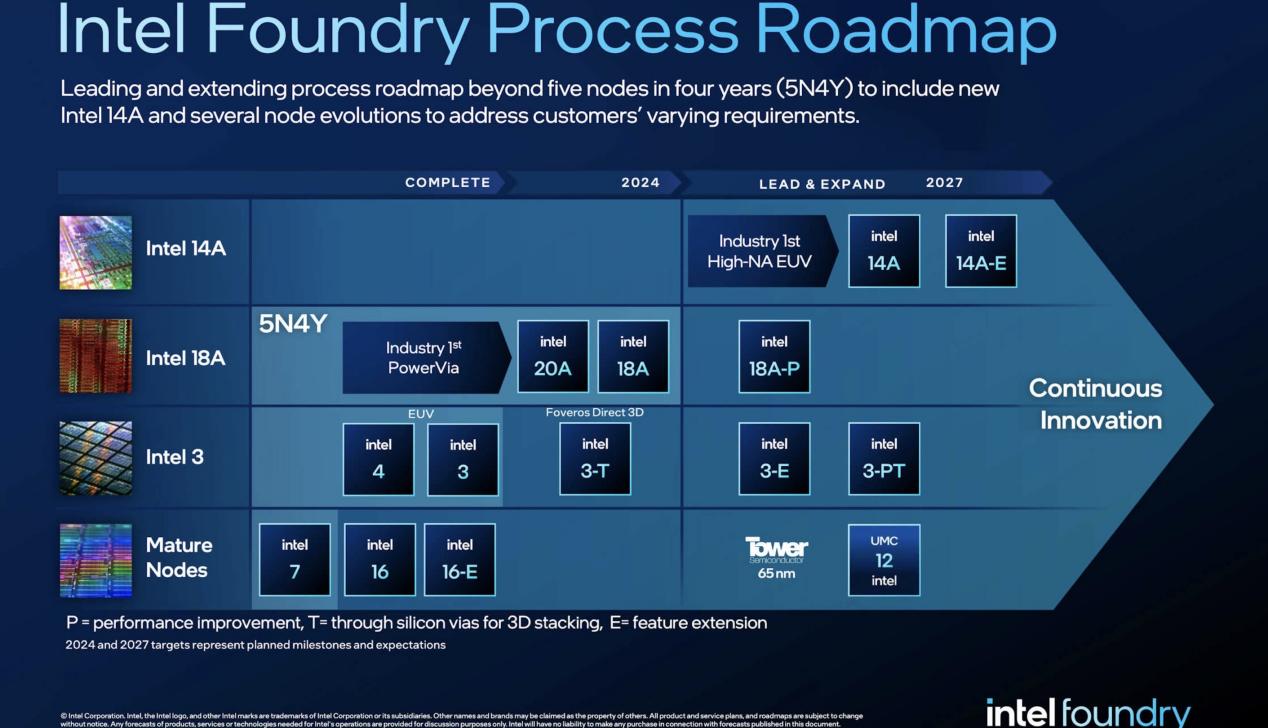

作为才进入晶圆代工市场没多久,且此前在工艺水平上落后不少的英特尔,却成了背面供电技术的先行者。在2024年上半年投产的20A节点上,英特尔将成为业界首个将背面供电技术应用于量产节点的厂商,而该节点也将首次引入英特尔的GAA版本,RibbonFET晶体管。

早在去年,英特尔就在Blue Sky Creek这一测试芯片验证了PowerVia背面供电技术的优势。Blue Sky Creek是基于英特尔去年底发布的Meteor Lake处理器中能效核(E-Core)打造的,在PowerVia的设计下,核心频率有了5%以上的提升,单元密度达到90%以上。

英特尔工艺路线图 / 英特尔

根据英特尔说法,由于PowerVia这类背面供电技术减少了互联层这个生产成本最高、工序较为复杂的部分,也就意味着在先进工艺上的制造成本会有所减少,同时EUV参与的工作量也会一并减少。

尽管如此,良率依然是英特尔最关心的,要想真正做到大规模量产,良率达标才是该工艺节点正式投入使用的标志。英特尔在去年试验阶段的目标是让基于PowerVia的Intel 4芯片与九个月前的Intel 4芯片良率匹配。随后在Intel 20A上达到类似的良率目标,并用于今年发售的Arrow Lake处理器上。

台积电:2025年进入开始采用GAAFET,但背面供电缺席2nm

今年4月的北美技术研讨会上,台积电也对其工艺路线图进行了更新,不过在时间节点上的计划并没有改变:基于第一代GAAFET技术的N2节点将于2025年下半年开始量产,而新能改良版的N2P将于2026年末接替N2的位置,同年也会推出电压加强版的N2X节点。

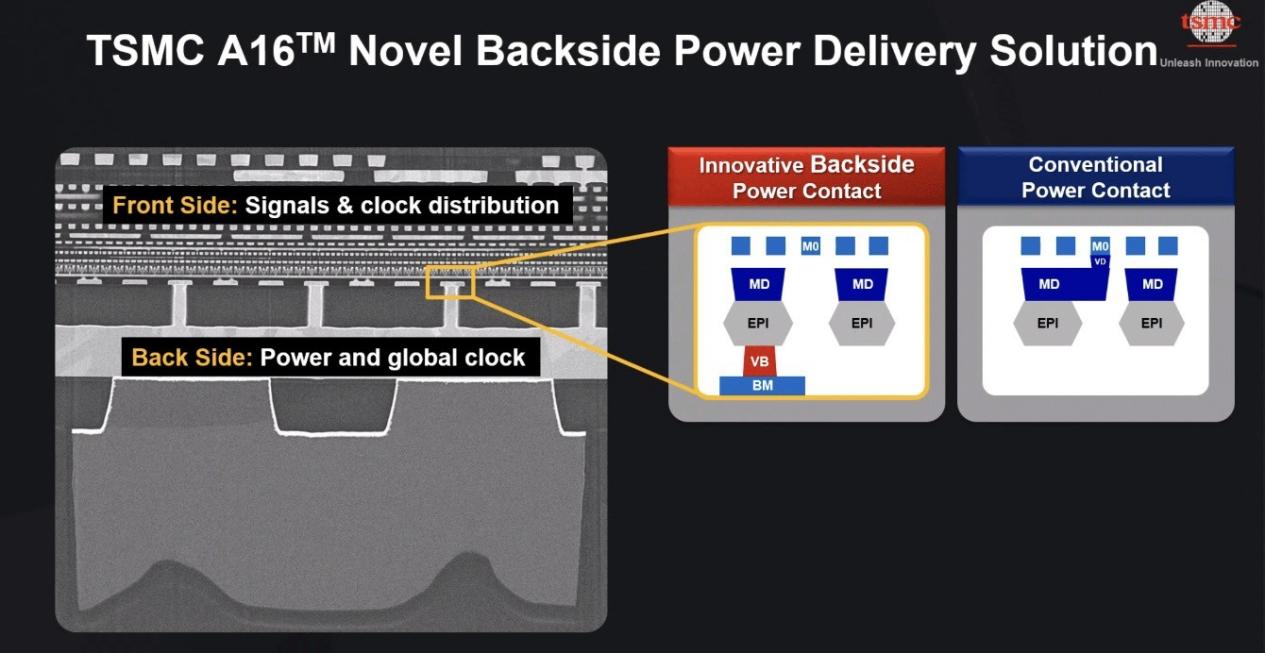

台积电SPR技术 / 台积电

不过有趣的是,台积电的技术路线发生了改变,N2P不再加入此前宣布的背面供电技术,台积电决定将该技术的应用推迟至A16节点。在台积电2023年的路线图中,N2P基于N2节点的改善之一就是加入SPR背面供电技术,不过好在A16节点的投产目标也在2026年,只不过预计在年末的时段。

台积电对其背面供电技术的命名为Super Power Rail(SPR),并表示该技术最适合用于HPC产品,因为此类产品往往具备复杂的信号路线和密集的供电网络。相较于N2P,A16在背面供电技术的加持下,可以实现在同电压下8%-10%的速度提升,在同样的速度下可以将功耗降低15%-20%,芯片密度则会实现1.07至1.1倍的提升。

根据台积电的说法,他们的SPR技术直接将背面供电网络与每个晶体管的源极和漏极相连,就面积效率而言这是最有效的一个技术路线,在生产方面,这是最复杂或者说最昂贵的一条路线,或许也是因为考虑到成本和效率之类的原因,台积电才决定将其延后至A16节点。

与另外两家不同的是,台积电并没有披露更多2nm之后的工艺节点,目前只有一个A16节点,而三星和英特尔都已经公开了在1.4nm工艺上的计划。台积电是否在进入埃米时代后,继续保持性能、良率和产量上的三重优势,依然值得我们持续关注。

三星:改良版2nm,PPA全面提升

在2024年之前,三星的计划是在SF1.4这一1.4nm节点上用上背面供电技术,如果以过去的工艺路线图来看,三星在2027年才会将背面供电技术集成在最新工艺上,明显要晚于另外两家竞争对手。但三星在背面供电技术上的研究早就开始了,去年他们也为两个基于Arm架构的测试芯片实现了背面供电,虽然并没有透露工艺节点,但三星表示在测试的两个节点下分别实现了10%和19%的芯片面积减少。

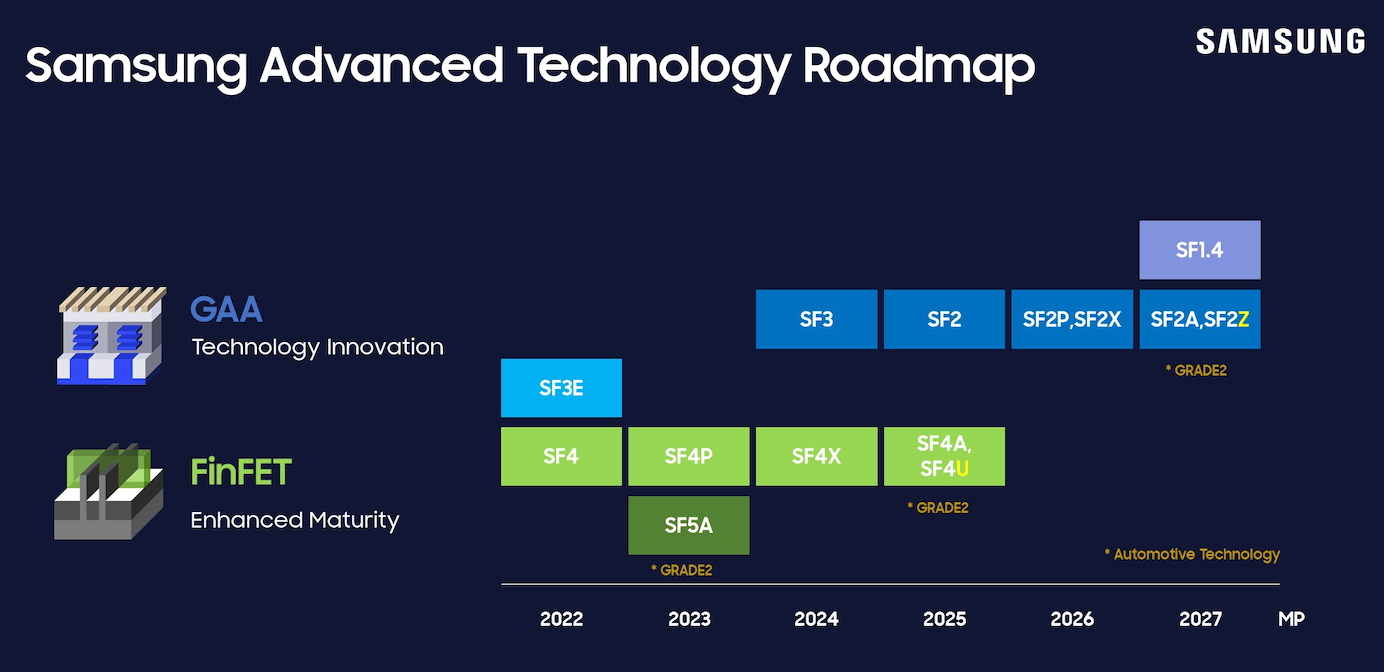

三星最新工艺路线图 / 三星

然而在近日举办的三星北美SFF大会上,三星发布了全新的工艺路线图,主要是在2nm节点上进行了更新。从原先的SF2和SF2P两个节点,再增加三个节点,分别是SF2X、SF2Z和SF2A。其中SF2和SF2P依然是针对移动应用打造,而SF2X和SF2Z则是为了HPC/AI应用打造,同时三星也把背面供电率先集成在SF2Z上,SF2A则是针对汽车应用打造的节点。

SF2和SF2P两大节点分别计划25年和26年量产,SF2X计划26年量产,而SF2Z和SF2A分别定在27年量产。由此看来,虽然路线图有所更新,但三星依然是最后一个用上背面供电技术的晶圆厂,作为从2022年起就开始生产GAA的晶圆厂,三星在GAA的技术成熟度上应该不输其他两家。

三星在本次SFF大会上,也再次保证1.4nm的SF1.4工艺准备工作仍在稳步进行,性能和良率目标不变,且与SF2Z一样,预计于2027年进入大规模量产。作为“超越摩尔”工作的一环,三星也在持续寻求材料和架构上的创新,从而在1.4nm之后的工艺上实现突破。

被谨慎对待的背面供电技术

与传统的正面供电技术相比,背面供电技术无疑可以提高芯片性能,有的甚至还能进一步降低成本,但在技术成熟前,晶圆厂面临的是良率、可靠性、散热和调试性能上可能存在的多重问题,所以绝大多数晶圆厂仍在权衡,或许今年下半年英特尔推出的Arrow Lake处理器能给我们一个参考。

与此同时,晶体管密度也可能不再是划分先进与成熟工艺的唯一标准,从这三家厂商的路线图来看,即便未来进一步改进的3nm或4nm节点,很可能还是会继续使用FinFET和传统正面供电技术。

-

供电技术

+关注

关注

1文章

27浏览量

11009 -

2nm

+关注

关注

1文章

215浏览量

5094 -

GAA

+关注

关注

2文章

38浏览量

7907

发布评论请先 登录

2nm“诸神之战”打响!性能飙升+功耗骤降,台积电携联发科领跑

全球首款2nm芯片被曝准备量产 三星Exynos 2600

今日看点丨三星美国厂2nm产线运作;《人工智能生成合成内容标识办法》正式生效

今日看点:传台积电先进2nm芯片生产停用中国大陆设备;保时捷裁员约200人

算力存储:首款2nm定制SRAM来了!

台积电2nm良率超 90%!苹果等巨头抢单

台积电2nm制程良率已超60%

手机芯片进入2nm时代,首发不是苹果?

台积电加大亚利桑那州厂投资,筹备量产3nm/2nm芯片

联发科采用AI驱动Cadence工具加速2nm芯片设计

台积电设立2nm试产线

2025年半导体行业竞争白热化:2nm制程工艺成焦点

台积电2nm工艺将量产,苹果iPhone成首批受益者

台积电分享 2nm 工艺深入细节:功耗降低 35% 或性能提升15%!

2nm突围,背面供电技术的首个战场

2nm突围,背面供电技术的首个战场

评论