高性能时钟缓冲器CDCVF2310-EP:设计与应用全解析

在电子工程师的日常工作中,时钟缓冲器是一个至关重要的组件,它能够确保时钟信号的稳定传输和分配。今天我们要详细探讨的就是德州仪器(TI)推出的一款高性能时钟缓冲器——CDCVF2310 - EP。

文件下载:cdcvf2310-ep.pdf

一、核心特性

1. 高性能驱动能力

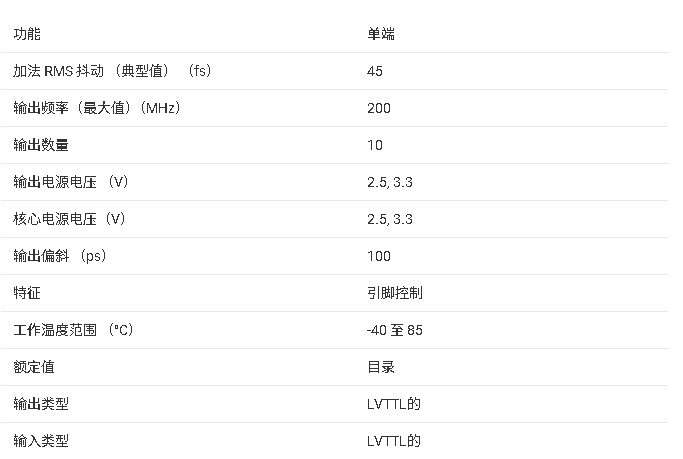

CDCVF2310 - EP是一款1:10的时钟驱动器,在(V_{DD})为3.3V时,它能够以高达200MHz的频率稳定运行。这意味着它可以满足大多数高速时钟系统的需求,为系统提供稳定的时钟信号。

2. 低引脚间偏移

在(V_{DD})为3.3V时,其引脚间偏移(Pin - to - Pin Skew)小于100ps。低偏移特性对于需要精确时钟同步的系统至关重要,能够有效减少信号传输过程中的时间误差,提高系统的稳定性和可靠性。

3. 宽电源电压范围

该芯片的(V_{DD})范围为2.3V至3.6V,这使得它在不同的电源环境下都能正常工作,具有很强的适应性。无论是在低电压还是高电压的系统中,工程师都可以放心使用。

4. 输出使能毛刺抑制

CDCVF2310 - EP具备输出使能毛刺抑制功能,能够确保输出使能序列与时钟输入同步,从而在输入时钟的下一个完整周期(由输入时钟的负边沿触发)上启用或禁用输出缓冲器。这一特性可以有效避免时钟信号在使能或禁用过程中产生毛刺,保证时钟信号的纯净度。

5. 输出分配和片上阻尼电阻

它可以将一个时钟输入分配到两组各五个输出端,为多个需要时钟信号的模块提供稳定的时钟源。同时,芯片内置了25Ω的片上串联阻尼电阻,有助于减少信号反射和振荡,提高信号质量。

6. 封装形式

采用24引脚的TSSOP封装,这种封装形式体积小,便于在电路板上进行布局和焊接,适合各种小型化的电子设备。

二、应用场景

1. 通用应用

在各种通用电子系统中,如计算机、通信设备等,都需要稳定的时钟信号来保证系统的正常运行。CDCVF2310 - EP凭借其高性能和低偏移的特性,能够为这些系统提供可靠的时钟分配解决方案。

2. 国防、航空航天和医疗应用

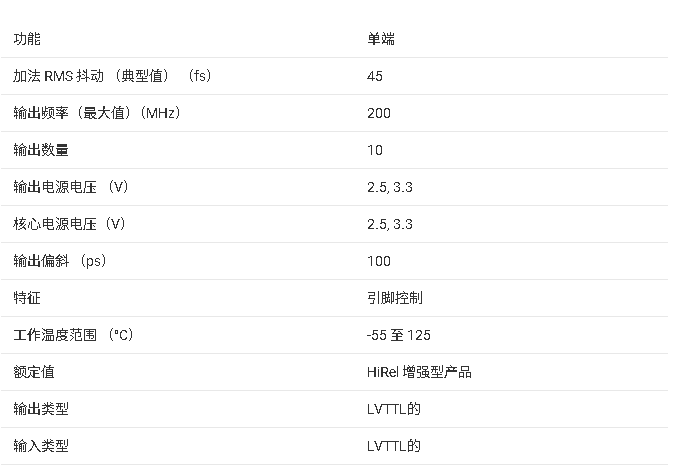

该芯片支持国防、航空航天和医疗等对可靠性和稳定性要求极高的应用领域。它具有受控基线、单一组装和测试地点、单一制造地点等特点,并且可在军事温度范围( - 55°C至125°C)内正常工作,同时还具备延长的产品生命周期和产品变更通知功能,能够满足这些领域对产品质量和可靠性的严格要求。

三、功能与工作模式

1. 功能框图与引脚功能

从功能框图可以看出,CDCVF2310 - EP主要由逻辑控制部分和输出缓冲部分组成。其引脚包括时钟输入(CLK)、输出使能控制引脚(1G和2G)以及两组各五个输出引脚(1Y[0:4]和2Y[0:4])等。其中,1G和2G为输出使能控制引脚,高电平有效,当该引脚为逻辑高电平时,对应的输出时钟将跟随输入时钟(CLK)。

2. 工作模式

上电后,无论控制引脚的状态如何,输出的默认状态为低电平。在正常工作时,当控制引脚(1G或2G)为低电平,且在CLK输入上检测到负时钟边沿时,对应的输出组1Y[0:4]或2Y[0:4]将被置于低电平状态;当控制引脚(1G和2G)为高电平,且在CLK输入上检测到负时钟边沿时,对应的输出组将切换到缓冲模式,输出跟随输入时钟。

四、电气特性与参数

1. 绝对最大额定值

在使用CDCVF2310 - EP时,需要注意其绝对最大额定值,如电源电压范围为 - 0.5V至4.6V,输入电压范围为 - 0.5V至(V_{DD}) + 0.5V(最大值限制为4.6V)等。超过这些额定值可能会导致器件永久性损坏,因此在设计电路时必须严格遵守。

2. 推荐工作条件

推荐的电源电压范围为2.3V至3.6V,不同的电源电压下,输入和输出的电压、电流等参数也有所不同。例如,在(V{DD})为3V至3.6V时,低电平输入电压(V{IL})最大为0.8V,高电平输入电压(V_{IH})最小为2V。同时,未使用的输入引脚必须保持高电平或低电平,以防止其浮空。

3. 电气参数

在推荐的工作结温范围内,芯片的输入电流、静态器件电流、输入电容、输出电容等参数都有明确的规定。例如,输入电流在(V{I})为0V或(V{DD})时,最大为±5μA;静态器件电流在CLK为0V或(V{DD}),且输出电流(I{O})为0mA时,典型值为100μA。

4. 时序要求

时钟频率在(V{DD})为3V至3.6V时,最大为200MHz;在(V{DD})为2.3V至2.7V时,最大为170MHz。同时,芯片还规定了输出延迟、输出偏移、脉冲偏移、上升时间、下降时间等时序参数,这些参数对于保证时钟信号的质量和同步性非常重要。

五、热性能与封装信息

1. 热性能指标

文档中给出了该芯片的多项热性能指标,如结到环境的热阻(theta{JA})为91.7°C/W,结到顶部的热阻(theta{JCtop})为31.2°C/W等。这些指标可以帮助工程师在设计散热方案时,正确评估芯片的发热情况,确保芯片在正常的温度范围内工作。

2. 封装信息

CDCVF2310 - EP采用TSSOP(PW)封装,提供了多种可订购的零件编号,不同的编号在包装数量、载体等方面有所不同。同时,还给出了详细的封装尺寸图、引脚排列图以及电路板布局示例、模板设计示例等,为工程师的电路板设计提供了便利。

六、设计时的注意事项

1. ESD防护

该集成电路容易受到静电放电(ESD)的损坏,因此在处理和安装过程中,必须采取适当的防护措施,如佩戴防静电手套、使用防静电工作台等。否则,ESD损坏可能会导致芯片性能下降甚至完全失效。

2. 电源稳定性

由于芯片对电源电压有一定的要求,因此在设计电源电路时,要确保电源的稳定性和纯净度,尽量减少电源纹波和噪声的影响。可以使用滤波电容、电感等元件来改善电源质量。

3. 布局布线

在电路板布局布线时,要注意时钟信号的传输路径,尽量减少信号的干扰和延迟。同时,要合理安排芯片的引脚和其他元件的位置,确保散热良好。

CDCVF2310 - EP是一款性能优异、应用广泛的时钟缓冲器芯片。电子工程师在设计相关电路时,只要充分了解其特性、参数和注意事项,就能够充分发挥其优势,为系统提供稳定、可靠的时钟信号。大家在使用过程中遇到过哪些问题呢?欢迎在评论区分享交流。

-

时钟缓冲器

+关注

关注

2文章

273浏览量

51954 -

电子设计

+关注

关注

42文章

2918浏览量

49917

发布评论请先 登录

CDCVF2310-EP CDCVF2310-EP 2.5V 至 3.3V 高性能时钟缓冲器

什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析

CDCVF2310 2.5V至3.3V高性能时钟缓冲器数据表

CDCVF2310-EP 高性能时钟缓冲器技术文档摘要

CDCVF2310 2.5V-3.3V高性能时钟缓冲器技术文档总结

高性能时钟缓冲器CDCVF2310 - EP:设计与应用全解析

高性能时钟缓冲器CDCVF2310 - EP:设计与应用全解析

评论