深入解析CDCL1810A:高性能时钟分配器的卓越之选

在电子设计领域,时钟分配器的性能对于系统的稳定性和可靠性起着至关重要的作用。今天,我们就来深入探讨一下德州仪器(TI)的CDCL1810A这款高性能时钟分配器,看看它有哪些独特的特性和优势。

文件下载:cdcl1810a.pdf

一、CDCL1810A概述

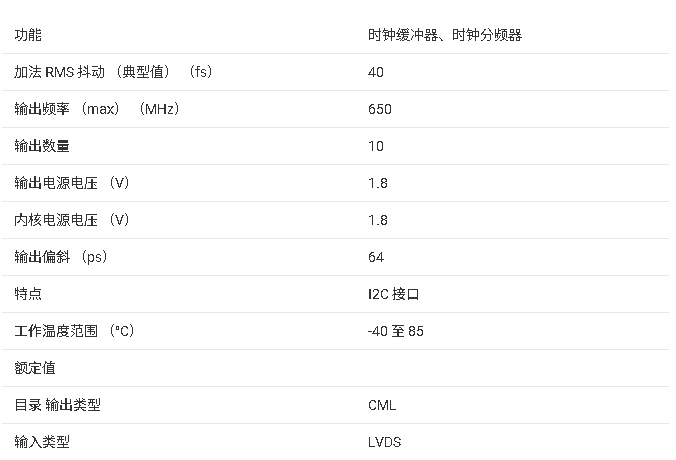

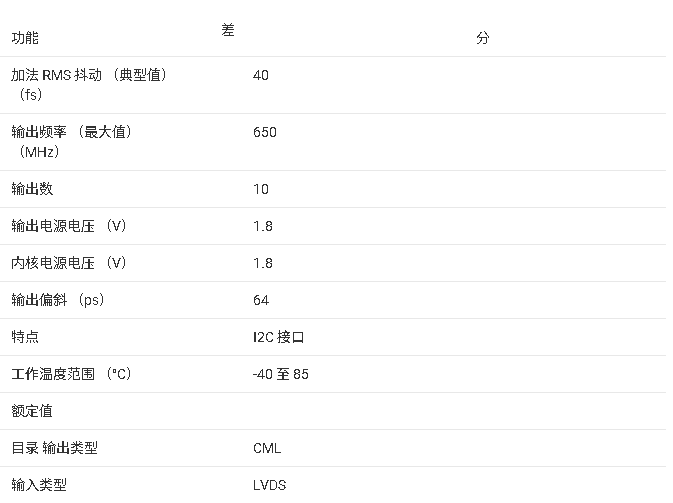

CDCL1810A是一款1.8V、具有10个输出的高性能时钟分配器。它采用单1.8V电源供电,具备低输入到输出附加抖动(低至10fs RMS)的特点,能够为高速SERDES等应用提供稳定的时钟信号。其输入采用低电压差分信号(LVDS),具有100Ω差分片上终端,最高支持650MHz的频率;输出为差分电流模式逻辑(CML),具有50Ω单端片上终端,同样最高支持650MHz的频率。该器件还拥有两组各五个输出,每组都有独立的分频比,输出频率可通过1、2、4、5、8、10、16、20、32、40和80的分频比得出。

二、关键特性分析

1. 低抖动性能

低至10fs RMS的输入到输出附加抖动,使得CDCL1810A在处理高速信号时能够保持出色的稳定性,减少信号失真和干扰,为系统提供精确的时钟信号。这对于对时钟精度要求极高的高速SERDES应用来说至关重要,能够有效提高系统的性能和可靠性。

2. 灵活的分频配置

可编程分频器P0和P1为输出频率与输入频率的比值提供了高度的灵活性,计算公式为 (F{OUT }=F{IN } / P) ,其中P(P0,P1)可以取1、2、4、5、8、10、16、20、32、40和80。这种灵活的分频配置使得CDCL1810A能够适应不同的应用需求,满足多样化的设计要求。

3. 接口兼容性

支持一个差分LVDS时钟输入和总共10个差分CML输出,并且CML输出在交流耦合时与LVDS接收器兼容。此外,在仔细观察输入电压摆幅和共模电压限制的情况下,还可以支持单端时钟输入。这种广泛的接口兼容性使得CDCL1810A能够与各种不同的设备进行连接,提高了其通用性和适用性。

4. 设备管理接口

通过SDA/SCL串行两线接口,所有设备设置都可以进行编程。该串行接口仅能耐受1.8V电压,并且支持400kb/s的快速模式和7位寻址,与流行的2引脚串行接口标准兼容。这为设备的配置和管理提供了方便,使得工程师可以根据实际需求对设备进行灵活的设置。

三、应用领域

1. 高速SERDES时钟分配

在1G/10G以太网、1X/2X/4X/10X光纤通道、PCI Express、串行ATA、SONET、CPRI、OBSAI等高速SERDES应用中,CDCL1810A可以将参考时钟分配到各个设备,确保系统的同步运行。其低抖动性能和高频率支持能力能够满足这些高速应用对时钟信号的严格要求。

2. 1对10时钟缓冲和扇出

CDCL1810A可以将一个时钟信号复制成10个输出,实现1对10的时钟缓冲和扇出功能。这在多DSP芯片环境等应用中非常有用,可以为多个设备提供相同的时钟信号,保证系统的一致性和稳定性。

四、设计要点

1. 电源供应

该设备设计为在1.8V的模拟电源(AVDD)和核心电源(VDD)下运行,AVDD和VDD可以由单个电源提供。在设计电源电路时,要确保电源的稳定性和纯净度,避免电源噪声对设备性能产生影响。

2. 布局设计

- 旁路电容连接:旁路电容与设备电源之间的连接应尽可能短,以减少电感和电阻,提高电源的稳定性。

- 电容接地:电容的另一侧应使用低阻抗连接到接地平面,以有效降低噪声。

- 电容选择:如果电容安装在背面,可以使用0402组件;如果安装在元件面,建议使用0201尺寸的电容,以方便信号布线。

- 接地处理:设备的暴露散热垫必须尽可能多地使用接地过孔焊接到地((V_{SS})),否则会严重影响设备性能。

五、与其他设备的比较

与CDCL1810相比,CDCL1810A在某些方面具有不同的特性。例如,CDCL1810A没有输出同步功能,但能确保在任何设备通信(如输出启用/禁用)期间所有输出保持启用状态,分频更改会立即应用于输出,不过可能会导致毛刺和不同的相位偏移。此外,CDCL1810A在连续和独立操作未编程输出方面表现更好,在配置和编程其他输出时,未编程的输出可以继续独立运行。

六、总结

CDCL1810A作为一款高性能时钟分配器,凭借其低抖动、灵活的分频配置、广泛的接口兼容性和方便的设备管理接口等特性,在高速SERDES和时钟缓冲扇出等应用中具有显著的优势。在设计过程中,合理的电源供应和布局设计是确保其性能发挥的关键。电子工程师在选择时钟分配器时,可以根据具体的应用需求和设计要求,综合考虑CDCL1810A的各项特性,以实现最佳的系统性能。你在实际应用中是否使用过类似的时钟分配器呢?遇到过哪些问题?欢迎在评论区分享你的经验和见解。

发布评论请先 登录

CDCL1810 1.8V 10路输出高性能时钟分配器数据表

CDCL1810A 1.8V、10 输出高性能时钟分配器数据表

CDCL1810A 高性能时钟分配器技术文档总结

CDCL1810高性能时钟分配器技术文档总结

深入解析CDCL1810A:高性能时钟分配器的卓越之选

深入解析CDCL1810A:高性能时钟分配器的卓越之选

评论