前言:当SK海力士与英伟达宣布合作开发目标性能达1亿IOPS的“AI-NP”次世代存储方案时,业界在惊叹其野心之余,一个严峻的工程现实也随之浮现:我们现有的测试与验证体系,正面临被其自身旨在测量的对象所淘汰的风险。 1亿IOPS——这个约是当前顶尖企业级固态硬盘十倍性能的数字,不仅是对存储介质和控制器架构的极限挑战,更是对半导体后端测试技术的“终极拷问”。如果验证技术停滞不前,任何设计上的辉煌突破,都可能在量产时因无法被准确计量和保证而黯然失色。这场性能军备竞赛的下半场,战火已从设计图纸蔓延至测试实验室。

趋势洞察:性能定义的权杖,正向验证能力转移

存储芯片的竞争维度已发生根本性转变。过去,竞争围绕容量、成本与耐久性展开;如今,在AI算力需求的暴力驱动下,极致带宽与极致延迟成为新的制高点。从HBM到如今目标1亿IOPS的超低延迟存储,其核心诉求是彻底消除数据存取瓶颈,让计算单元“永不饥饿”。

这一趋势导致了一个根本性变化:芯片性能的最终认定权,部分从设计者移交给了测试系统。 测试设备不再仅仅回答“芯片功能是否正常”,而必须权威地回答“芯片是否确如宣称般强大”。当性能目标冲至物理极限,测试系统本身的带宽、精度和延迟必须远优于被测芯片,才能提供无可置疑的测量基准。否则,性能宣称将沦为缺乏权威背书的“纸面数据”。因此,验证能力本身成为了性能竞赛的基础设施,其先进与否,直接决定了尖端产品能否被市场所采信。

技术挑战:验证“性能圣杯”的四重深渊

为1亿IOPS级别的存储芯片建立可信的验证体系,需要跨越四道看似不可逾越的技术深渊:

1.测试通道的“代际鸿沟”

芯片设计面向的是PCIe Gen6(64 GT/s)乃至更未来的接口协议,而主流高端测试机的接口带宽往往存在一至两代的滞后。如果测试机自身的数据通道存在瓶颈,就如同用一条乡间小路为超跑测速,测试结果反映的将是通道的极限,而非芯片的极限。精准测量纳秒级延迟和每秒亿万次操作,要求测试设备在接口物理层和协议栈上实现超前支持。

2.信号完整性的“毫米波战争”

数据传输速率进入数十GT/s领域后,整个测试链路的电气特性成为决定性因素。测试机内部走线、连接器、负载板乃至探针卡的微小阻抗失配,在如此高的频率下都会引发严重的信号反射和损耗,导致眼图塌陷。这意味着测试硬件的设计必须遵循射频与微波工程原则,其材质、工艺和仿真精度需达到通信设备级别,以维持测试信号的纯净度,确保测量的是芯片性能,而非测试夹具的衰减。

3.测试负载的“现实失真”

如何生成能逼真模拟AI数据中心工作负载、并足以“压满”1亿IOPS的测试向量?传统的固定模式或简单随机数据流已完全失效。验证需要能精确复现高强度混合读写比(如70/30)、深度队列、高度随机且碎片化的数据访问模式。这要求测试系统具备强大的实时数据生成、调度与比对能力,其复杂程度堪比一个小型的数据流量生成系统。

4.量产现实的“时间与热力学诅咒”

在实验室中,或许可以花费数小时对一颗芯片进行详尽的特性分析。但在量产中,测试时间是以毫秒计的奢侈。如何在极短的接触时间内,完成从接口链路训练、性能峰值扫描到稳定性快速筛查的全套动作,是工程上的巨大挑战。同时,芯片在全速测试时产生的瞬时高功耗与集中发热,对测试座的散热设计提出了近乎残酷的要求,任何散热不足都将导致芯片因热降频而无法展现真实性能。

解决方案:构建“探针式”的新一代性能计量基座

应对上述挑战,要求测试体系从“功能检验”范式全面转向 “极限性能计量” 范式,其核心是构建一个能够窥探并度量芯片性能巅峰的“基座”。

硬件基座先行:打造“超规格”的计量通道

测试设备供应商必须与标准组织及领先客户进行超前协同研发,确保其平台在芯片量产之前,就已具备下一代接口协议的完整计量能力。这包括采用更低损耗的高速连接器材料、利用先进电磁仿真设计PCB走线、并集成更高精度的时域反射计等功能,以确保证整个测试通道的性能余量远超被测芯片的设计规格。

软件引擎重构:开发“场景化”的负载模拟器

测试软件需进化为一个可灵活编程的应用负载模拟引擎。它应内嵌多种经过验证的AI训练与推理负载模型,允许用户根据自身场景调配参数,并能在测试中动态施加压力,快速绘制出芯片在不同负载下的性能曲面图与失效边界。其目标是以最高效率,在量产约束下逼近芯片的真实性能轮廓。

系统级协同设计:集成“对抗性”散热与并行架构

在测试硬件层面,必须集成主动式高效散热方案,如微通道液冷或涡流风冷,确保芯片测试触点能在持续峰值功耗下保持低温。在系统层面,通过多核处理器与高速背板互联,实现对多个被测单元(DUT)的并行、异步性能测试,用系统级的吞吐效率来弥补单颗芯片测试时长可能增加的影响。

结语

1亿IOPS的目标,如同一座灯塔,照亮了存储技术的未来航道,也同时照出了当前验证体系的暗礁。它宣告了一个新时代的到来:芯片的性能上限,将越来越由其验证体系的下限所决定。 如果计量工具无法跟上创新的步伐,那么最尖端的设计将因无法被准确证明而困于实验室。

在您看来,突破下一代存储性能验证瓶颈,是需要测试设备在硬件带宽上实现代际跨越更为紧迫,还是构建高度复杂且真实的软件负载模型面临更大困难? 当芯片的速度不断挑战物理学的边界,用于衡量其速度的“尺”与“钟”,必须首先完成自我革命。在这一前沿领域,那些如Hilomax一般,自1983年便扎根于半导体测试与烧录技术,通过持续自主研发(如率先攻克UFS4.1烧录核心)来定义行业标杆,并构建全球化服务网络以确保技术落地的企业,其价值正从提供工具,升维为赋能整个产业信任并兑现其性能承诺的基石性伙伴。

审核编辑 黄宇

-

AI

+关注

关注

90文章

38225浏览量

297116 -

IOPs

+关注

关注

0文章

13浏览量

14450

发布评论请先 登录

AI眼镜或成为下一代手机?谷歌、苹果等巨头扎堆布局

安森美SiC器件赋能下一代AI数据中心变革

Microchip推出下一代Switchtec Gen 6 PCIe交换芯片

Telechips与Arm合作开发下一代IVI芯片Dolphin7

适用于下一代 GGE 和 HSPA 手机的多模/多频段 PAM skyworksinc

罗德与施瓦茨携手高通成功验证下一代紧急呼叫系统

安森美携手英伟达推动下一代AI数据中心发展

下一代高速芯片晶体管解制造问题解决了!

下一代PX5 RTOS具有哪些优势

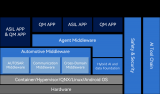

光庭信息推出下一代整车操作系统A²OS

亿纬锂能将为小鹏汇天提供下一代原理样机低压锂电池

罗德与施瓦茨和高通合作加速下一代无线通信发展

使用下一代GaNFast和GeneSiC Power实现电气化我们的世界

瞄准1亿IOPS:下一代AI存储的“性能验证”如何不拖后腿?

瞄准1亿IOPS:下一代AI存储的“性能验证”如何不拖后腿?

评论