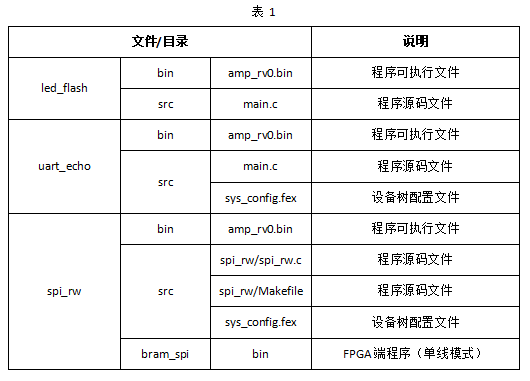

MounRiver Studio2支持在主菜单Project下勾选Show Memory Analysis开启内存分析功能。开启该功能后进行工程编译,无需额外配置工程属性,就可以直观地查看各个段链接后在内存空间的分配信息,以及符号的排列统计。

随着编译后的分析进度完成,编辑器会扩展一个分组区域打开编译结果分析视图。

视图上方以柱形图显示各个section节大小,以及饼图形式展现Flash和RAM的大小和使用量。

- text为代码节,存储在Flash中

- data为数据节。初始值在Flash,运行时在RAM

- bss为未初始化数据节,只存储在RAM中。

对于一般程序,Flash的使用量为.text,.data节大小之和;RAM使用量为.data,.bss节大小之和。

分析视图的下方为符号表,显示符号的类型(函数或变量),名称,地址,大小等详细属性。表中默认以地址递增排序,也可以按需选择大小排序。

通过符号表,物理内存分布一目了然,此外方便工程师进行一些功能优化:

- 代码膨胀定位:快速识别占用空间最大的函数

- 库函数优化:发现大型库函数,考虑替换或优化实现

- 异常快速定位:通过程序计数器pc值直接定位故障函数,协助调试

- 缓存局部性优化:将频繁调用的函数集中放置,提高指令缓存命中率;分支预测改善:

变化和状态栏显示了同个工程与上一次编译时的符号状态和大小变化值。我们通过将例程模块简单修改后重新编译。改动后打印函数后未被调用,打印库中相关函数都没有被链接,因此代码体积减小,区域FLASH和RAM大小骤减,库函数如memset状态为removed。关联的符号变化和在表中均能直观体现。

内存分析下方的符号视图还提供了上下文菜单。选择某符号的行后右键,支持跳转到符号在源码中定义位置。

右键符号,同样支持跳转到该符号反汇编对应位置,编辑器会打开其所在编译单元中间文件(.o)的反汇编结果,供用户快速浏览处理优化后的汇编指令。

-

Memory

+关注

关注

1文章

80浏览量

30851 -

IDE

+关注

关注

0文章

368浏览量

49210 -

嵌入式开发

+关注

关注

18文章

1169浏览量

50219 -

编译

+关注

关注

0文章

696浏览量

35277 -

RISC-V

+关注

关注

49文章

2946浏览量

53535

发布评论请先 登录

RT-Thread 邀您参与“开放・连接”2026玄铁 RISC-V 生态大会,携手共铸 RISC-V“芯”纪元

RISC-V不支持 Nx吗?

RISC-V,正式崛起

探索RISC-V在机器人领域的潜力

为什么RISC-V是嵌入式应用的最佳选择

RISC-V 蜂鸟E203中PC指针起始地址设置搭建

RISC-V B扩展介绍及实现

国产!全志T113-i 双核Cortex-A7@1.2GHz 工业开发板—RISC-V案例开发手册(上)

普华基础软件亮相2025 RISC-V中国峰会

RISC-V 手册

2025新思科技RISC-V科技日活动圆满结束

RISC-V International CEO:RISC-V 应用全面开花,2031 年渗透率将达 25.7%

兆松科技发布高性能RISC-V编译器ZCC 4.0.0版本

RISC-V和ARM有何区别?

RISC-V架构下的编译器自动向量化

RISC-V IDE MRS2使用笔记(二): 编译后Memory分析

RISC-V IDE MRS2使用笔记(二): 编译后Memory分析

评论