电路功能与优势

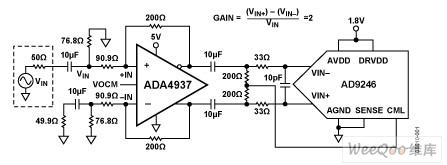

本文所述电路如图1所示,它利用ADC驱动器 ADA4937-1 提供交流耦合单端输入至差分的转换,用于驱动14位125 MSPS ADC AD9246 。ADA4937是一款低噪声、超低失真、高速差分放大器,具有低直流失调和出色的动态性能。它是分辨率高达16位、DC至100 MHz、高性能ADC的理想驱动器,非常适合各种不同的数据采集和信号处理应用。与以前的模数转换器相比,此电路的功耗与成本均有所降低,适用于通信、仪器仪表和医疗成像等应用。

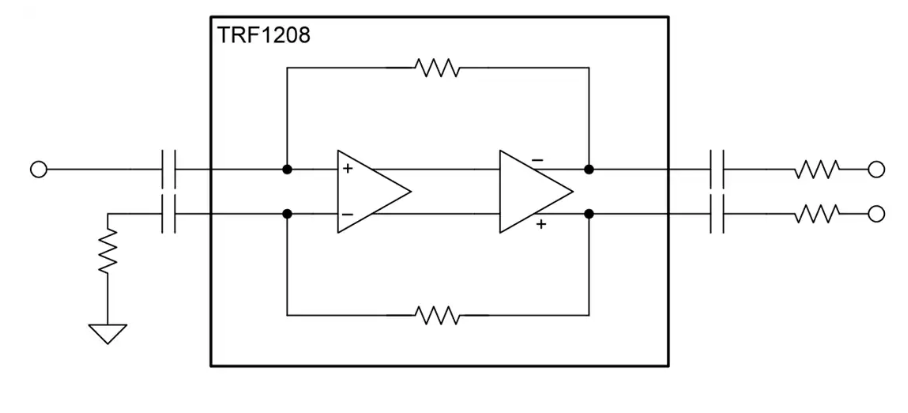

图1. ADA4937-1驱动AD9246

电路描述

AD9246是一款单芯片、14位、80 MSPS/105 MSPS/125 MSPS模数转换器(ADC),采用1.8 V单电源供电,内置一个高性能采样保持放大器(SHA)和片内基准电压源。利用宽带宽、真差分采样保持放大器(SHA),用户可以选择包括单端应用在内的各种输入范围和偏移。该器件可用于多路复用系统,在连续通道中切换满量程电平,以及采用远超过奈奎斯特速率的频率对单通道输入进行采样。

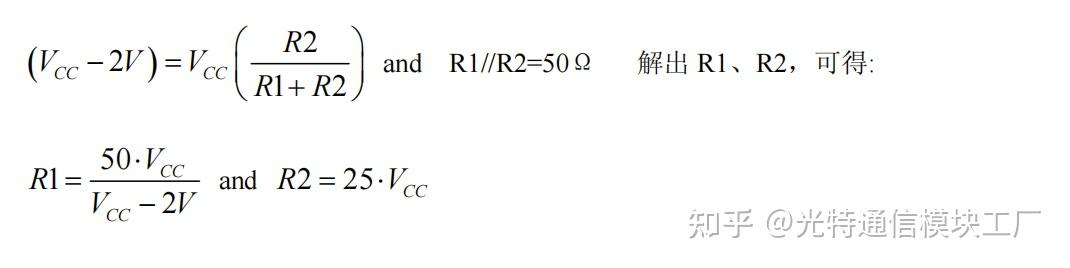

采用差分驱动时,AD9246能够实现最佳性能。ADA4937不仅提供单端至差分转换,而且提供增益与电平转换。ADA4937的输出共模电压通过电阻分压器与ADA4937的Vocm引脚相连来设置。

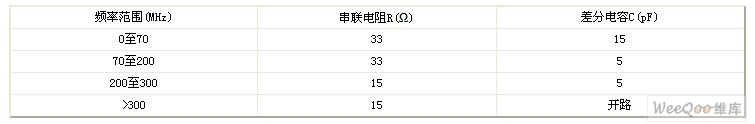

ADC驱动器的输出交流耦合至一个单极、低通滤波器。该低通滤波器可降低ADC输入处的噪声带宽,并且与ADC及驱动器的开关电容输入形成一定程度的隔离。在任何配置中,分流电容值C均取决于输入频率和源阻抗,并且可能需要减小或去除。表1列出了设置RC网络的建议值。不过,这些值取决于输入信号,只能用作初始参考。

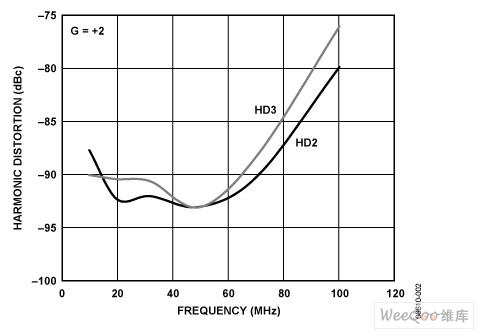

图2. ADA4937和AD9246组合的HD2/HD3

ADC的输入共模电压由CML引脚和一对200 Ω电阻设置。在其它应用中,CML与ADA4937的Vocm引脚用来设置ADC的输入共模电压,请参考下一部分“常见变化”。ADA4937采用ADI公司专有的硅-锗(SiGe)互补双极性工艺制造,可实现极低的失真水平,输入电压噪声仅为2.2 nV/√Hz。

图1所示电路已经过各种频率的?1 dBFS信号测试。图2所示为二次和三次谐波失真(HD2/HD3)与频率的关系曲线。

常见变化

驱动ADC时,还可以考虑其它几种放大器配置:差分交流耦合输入至差分输出、直流耦合单端输入至交流耦合差分输出、直流耦合单端输入至差分输出以及直流耦合差分输入至差分输出。

在直流耦合系统中,驱动器输出共模电压通过Vocm引脚设置。可调输出共模电平使ADA4937输出能够与ADC的输入共模电压相匹配。ADA4937的内部共模反馈环路也可提供出色的输出平衡,并能抑制偶数阶谐波失真积。在这些应用中,ADC的CML引脚经常与驱动器的Vocm引脚直接相连,确保实现最佳的ADC输入共模电压。在其它应用中,Vocm引脚可以采用低阻抗源驱动,如运算放大器等。也可以让Vocm引脚保持浮地,但通过一个电容来旁路,这种情况下,Vocm电压被设置为+Vs和–Vs引脚所施加电压的中间点。

表1. RC网络建议值

:

发布评论请先 登录

AD8310用交流耦合的时候,输出电压的浮动特别大,怎么解决?

XC9246B65CMR - G评估板:降压DC/DC转换器的技术解析

XC9246B75CMR - G 评估板数据解析与设计要点

MAX12557:高性能14位IF/基带ADC的卓越之选

AD9254:高性能14位150 MSPS模数转换器的深入剖析

AD9246:高性能14位ADC的深度剖析与应用指南

AD9233:高性能12位ADC的深度剖析与应用指南

14位、150 MSPS、1.8V模数转换器AD9254S:技术解析与应用指南

XU9246输入电压1.8-5.25V,输出电压2.5-5.5V,输出电流3A

TDP158:6Gbps交流耦合型TMDS或HDMI电平转换器转接驱动器深度解析

耦合之殇,软件设计中的隐疾

TRF1208 10MHz-11GHz ADC驱动器放大器技术解析

解析基带和射频的工作原理

PECL接口终端匹配技术详解:直流与交流耦合设计指南

在交流耦合基带应用中驱动AD9233/9246/9254 ADC

在交流耦合基带应用中驱动AD9233/9246/9254 ADC

评论