在高速数据通信与光模块领域,时钟源的选择直接决定系统的传输速率与链路稳定性。扬兴科技 YSO233UJ系列差分晶振,特别针对光模块关键频点 156.25MHz与 312.5MHz优化设计,以超低抖动、宽温稳定和高可靠性,为 800G、1.6T、3.2T光模块 提供精准的时钟支持。

一、关键频点优势

· 156.25MHZ

广泛应用于以太网 10G/100G/400G/800G/1.6T/3.2T 接口,是高速光模块的核心参考时钟。

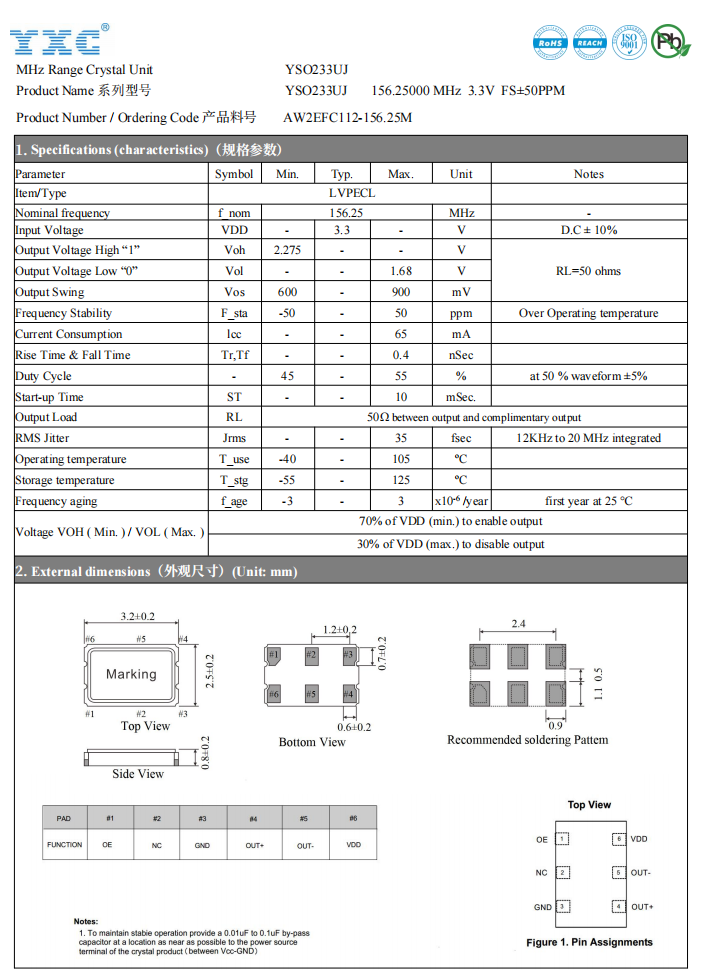

YSO233UJ在该频点下,采用LVPECL输出模式时,抖动低至35fs,极大降低误码率(BER),保障高速链路的数据完整性。

高基频光刻晶片设计,避免倍频产生的相位噪声累积,使得在大带宽高速SerDes通道中仍能保持高信号质量。

· 312.5MHZ

主要用于更高速的 SerDes 接口与新一代超大带宽光模块设计,是 800G/1.6T/3.2T光模块时钟架构的重要频点。

在该频点下,YSO233UJ仍能提供极低抖动,满足400GbE/800GbE/1.6TbE 以太网PHY 芯片与 DSP 芯片的时钟输入要求。

高频率下的低相位噪声特性,使其成为 低延迟互联和高速交换机背板的理想时钟源。

二、YSO233UJ系列差分晶振核心特性

1、超低抖动

在 156.25MHz 频点、LVPECL输出时,抖动值低至 35fs;在 312.5MHz 高频条件下依然维持优异的抖动性能。适配高速 SerDes、光模块 DSP,确保高速互联中 BER(误码率)最小化。

2、宽温与高稳定度

工作温度范围覆盖 -40°C至 105°℃,可选扩展至 -40°C至 125°C,满足数据中心和电信基站的极端环境需求。总频差 +50ppm,保证光模块在长时间运行下的频率一致性与协议符合性

3、多种输出兼容

·支持 LVDS、LVPECL、HCSL输出模式,灵活匹配不同光模块及主控芯片架构。

·通过简化外围设计,降低系统 BOM 成本,加速产品研发进度。

4、高基频光刻晶片工艺

·直接输出目标频点(156.25MHz/312.5MHz),避免倍频或分频方案带来的额外抖动。

·信号质量更高,相位噪声更低,特别适合高速光模块与核心交换应用。

三、在新一代光模块中的应用价值

· 800G光模块:

在 156.25MHz作为核心时钟输入时,保证光链路高速传输的稳定性;在312.5MHz 下,支持高速 DSP 芯片的精密时钟需求。

· 1.6T光模块:

超低抖动性能直接关系到系统 BER 水平,YSO233UJ通过优化的相位噪声指标,使其满足下一代互联标准。

· 3.2T光模块:

在高带宽应用中,312.5MHz 时钟频点尤为关键,YSO233UJ的高可靠性头超高速 SerDes 链路提供坚实保障。

结语

作为扬兴科技面向高速光通信市场推出的高性能差分晶振,YSO233UJ系列聚焦156.26MHz与 312.5MHz两大关键频点,以 35fs级超低抖动、±50ppm 稳定度、宽温支持,为 800G、1.6T、3.2T 光模块 提供精准时钟支持。它不仅优化了链路性能,更为新一代数据中心和超高速互联奠定了坚实基础。

-

有源晶振

+关注

关注

1文章

1014浏览量

22965 -

晶振

+关注

关注

35文章

3637浏览量

73817 -

高速光纤

+关注

关注

0文章

6浏览量

2961 -

差分晶振

+关注

关注

0文章

189浏览量

2099

发布评论请先 登录

光刻工艺的基本步骤

差分振荡器:支持0.15ps超低抖动的高速时钟核心

从SFP到OSFP:FCom差分晶振覆盖全类型光模块的时钟设计方案

差分输出 × 超低抖动:打造高速稳定的大型数据同步时脉

CW32 MCU在高频率运行下的系统稳定性的提升方案

请问通过DDS可以实现的最高频率的BPSK是多少MHz?

基于ispClock 5406D的高速串行接口时钟解决方案

用模拟时钟IC替代昂贵的高频率VCO,改善抖动性能

zpwsmileKLA-Tencor光刻工艺控制解决方案可将产量优化至0.13微米

YXC扬兴科技 MEMS振荡器 YSO691ER高稳定性和可靠性助力光端机领域

高速光模块时钟解决方案:YSO233UJ通过高基频光刻工艺实现超低抖动与高频率稳定性

高速光模块时钟解决方案:YSO233UJ通过高基频光刻工艺实现超低抖动与高频率稳定性

评论