“本文将详细介绍 CAMM2 及其布线规范。”

什么是 CAMM2?

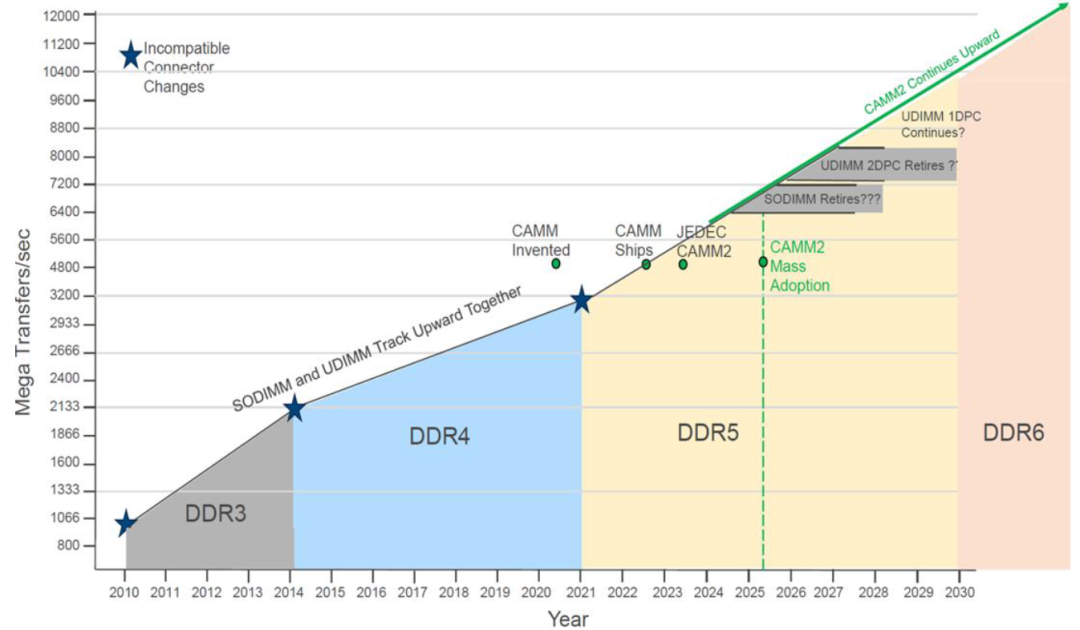

CAMM2 的全称是Compression Attached Memory Module 2,是由 JEDEC (固态技术协会) 正式采纳并发布的新一代内存模组标准(标准代号为JESD318),于 2023 年 12 月发布。它旨在取代已在笔记本电脑和小型 PC 中使用了超过 25 年的SO-DIMM标准。

CAMM2 的主要特点和优势:

-

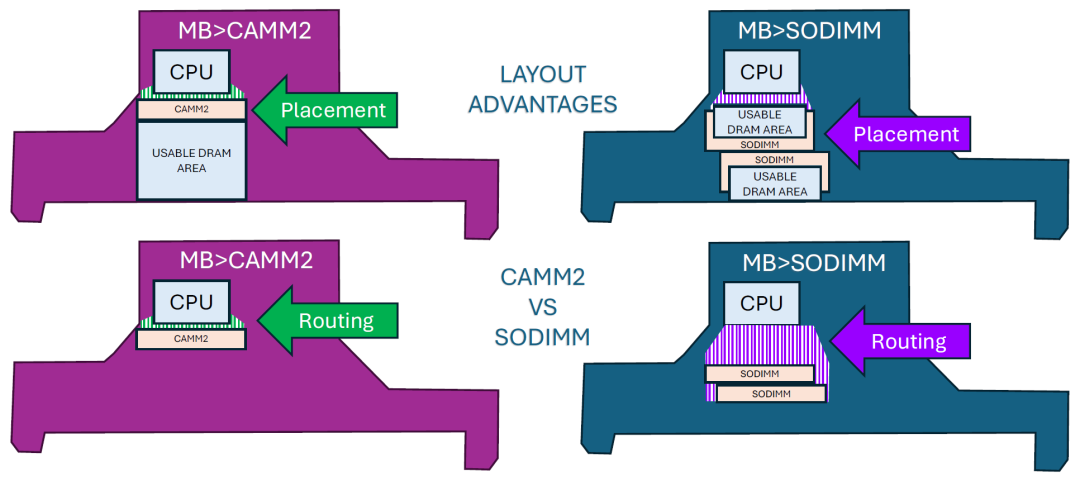

更薄、更节省空间:CAMM2 模组的设计非常纤薄,它平贴在主板上,而不是像 SO-DIMM 那样倾斜插入。与 SO-DIMM 相比,它可以节省高达 57% 的厚度和显著的主板面积,这对于制造更轻薄的笔记本电脑至关重要。

-

实现 LPDDR 内存的模组化:这是 CAMM2 最大的突破之一。传统上,LPDDR (低功耗内存) 因其信号要求,几乎总是直接焊接在主板上,导致用户无法升级。CAMM2 标准(特别是 LPDDR5/5X CAMM2)首次实现了低功耗内存的可插拔和可更换,兼顾了 LPDDR 的低功耗和高性能,以及模组化升级的灵活性。

-

更高的性能和带宽:由于模组直接平贴在主板上,内存颗粒与 CPU 之间的信号路径更短、更直接。这减少了信号干扰,使其能够支持比 SO-DIMM 更高的内存频率和数据速率。

-

支持双通道:单个 CAMM2 模组就可以支持双通道内存配置。而在 SO-DIMM 时代,实现双通道通常需要安装两条内存条。这简化了主板设计,并能在有限空间内提供更高的数据吞吐量。

-

两种版本:JESD318 标准定义了两种 CAMM2:

-

DDR5 CAMM2:针对需要高性能的主流笔记本和台式机。

-

LPDDR5/5X CAMM2:针对需要极致轻薄和低功耗的笔记本电脑。 这两种模组的引脚定义不同,不能混用,以确保系统安全。

SODIMM vs CAMM2

引脚设计

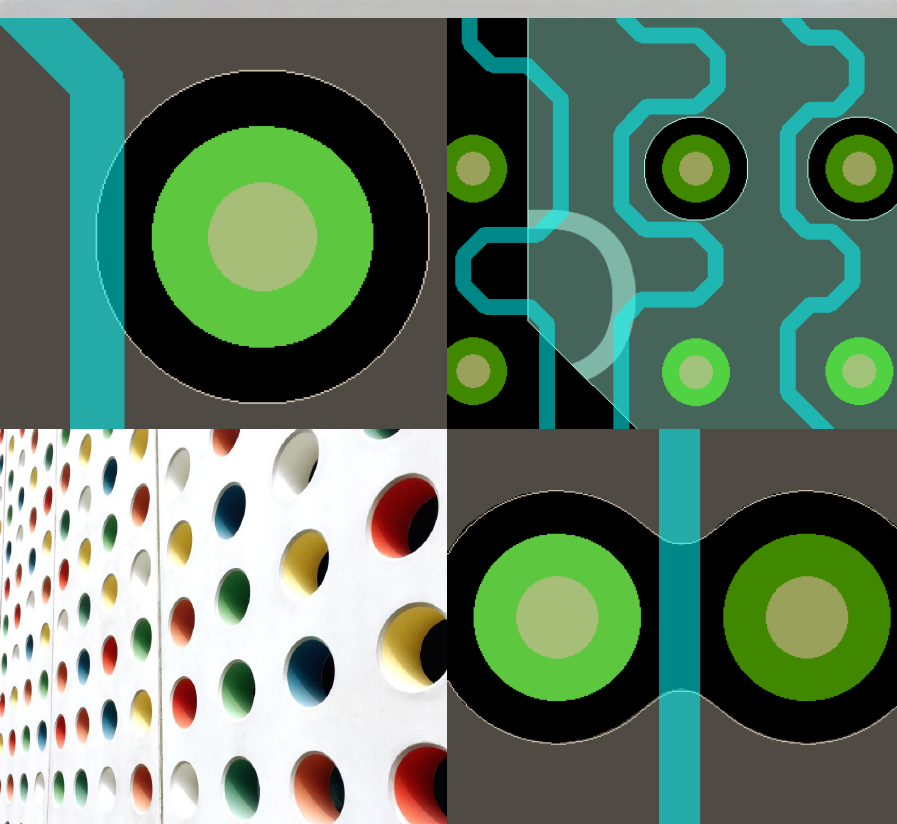

传统 SODIMM 金手指接触设计暴露在环境中,会导致 SODIMM氧化。

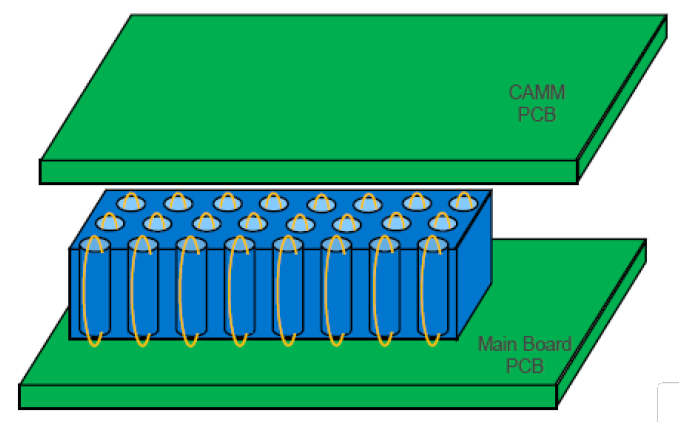

新 CAMM2 压缩触点引脚设计平直且短,并封装在一个圆柱体内。

CAMM PCB 阻挡圆柱体顶部 (模组),主板 PCB 阻挡圆柱体底部 。

新的 CAMM2 压缩触点设计:

CAMM2 设计有望消除内存重插的需求。

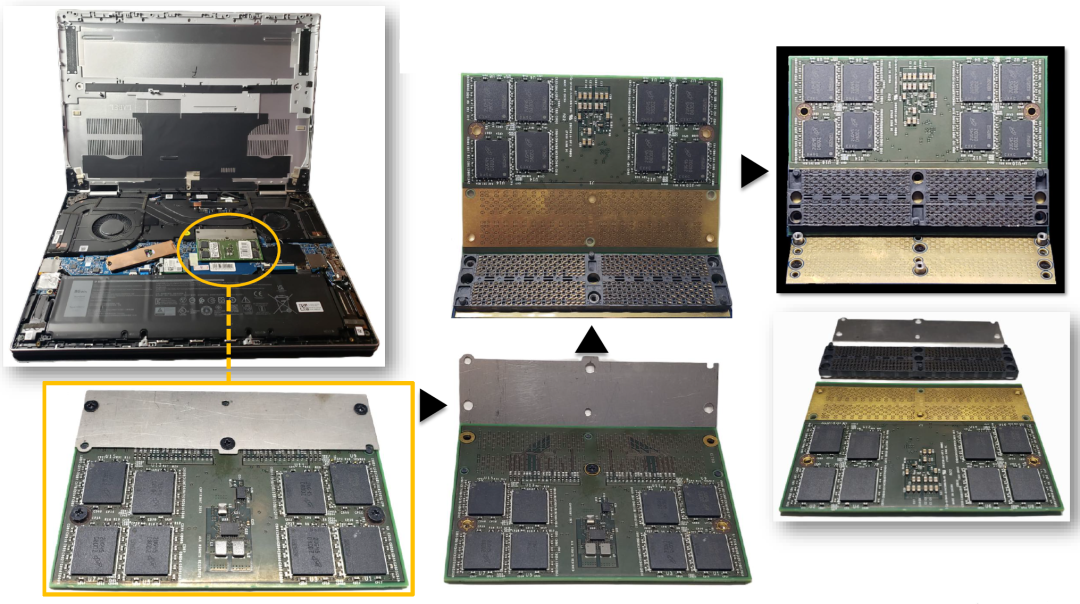

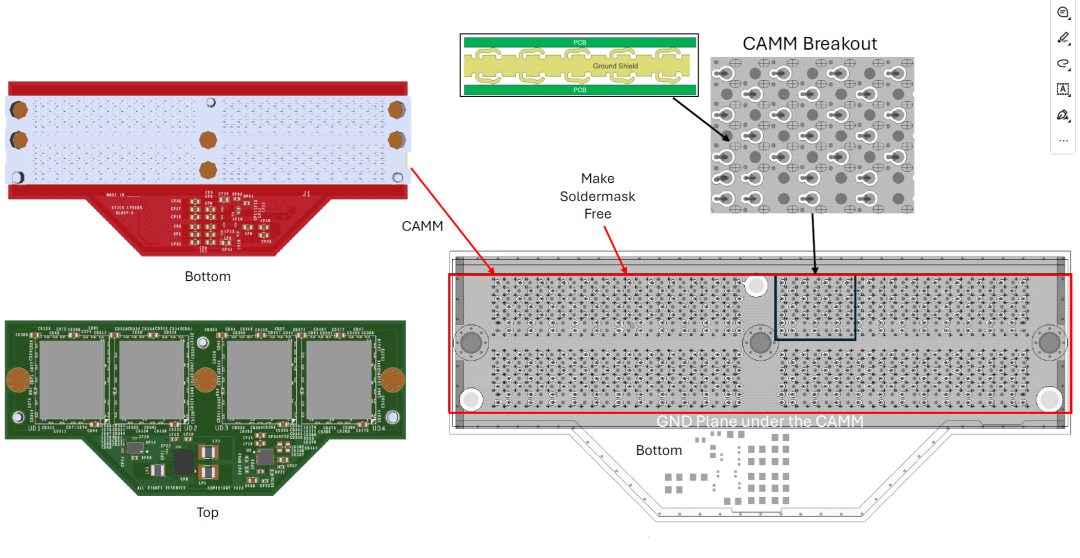

CAMM 近观

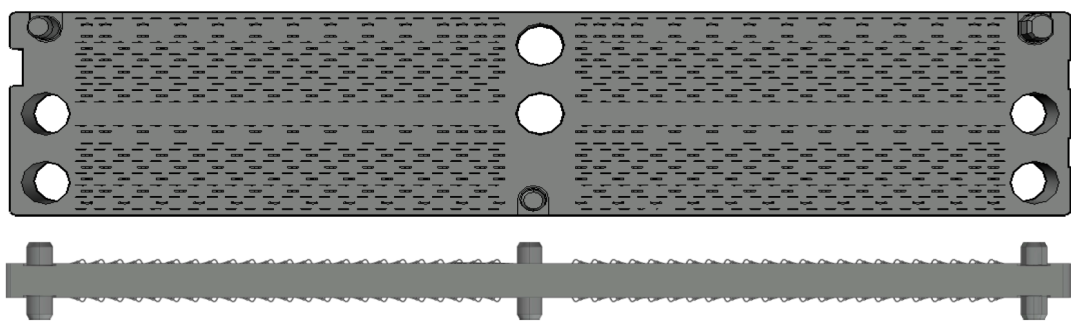

Dell 原始 CAMM 版本

-

616 个引脚

-

73.90 x 14.65 x 2.87 mm

-

两个安装孔

JEDEC CXXX 版本

-

644 个引脚,无接地屏蔽

-

78.00 x 17.00 x 1.00 mm

-

主要用于 LPDDR5 CAMM

JEDEC CAMM2 版本

-

356 个引脚 + 112 个接地屏蔽 (结构 A)

-

78.00 x 17.00 x 2.87 mm

-

3 个用于 DDR5 的安装孔

-

3 个用于 LPDDR5 的安装孔

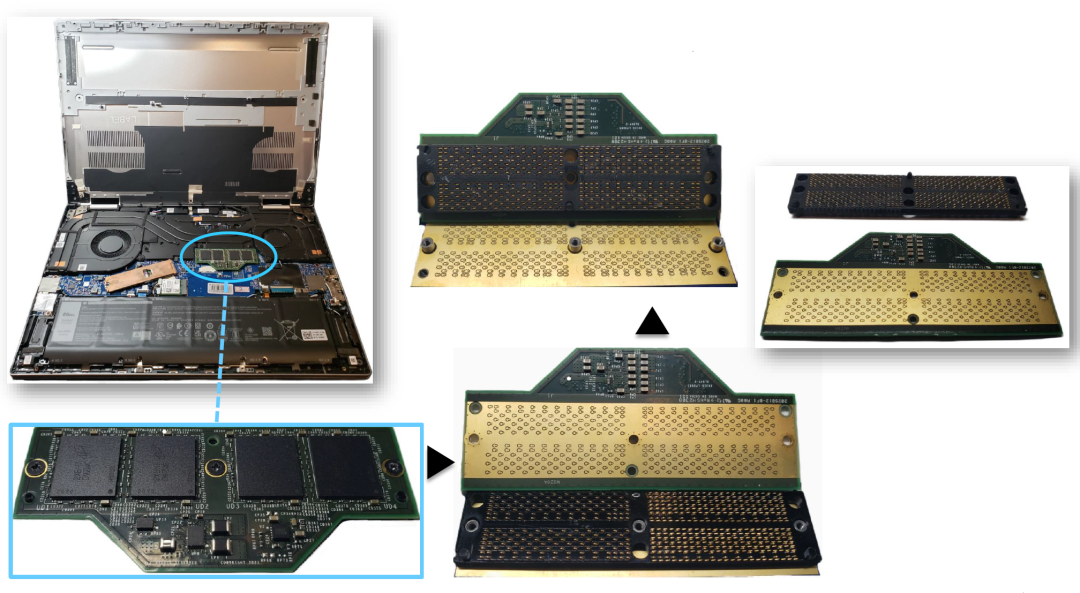

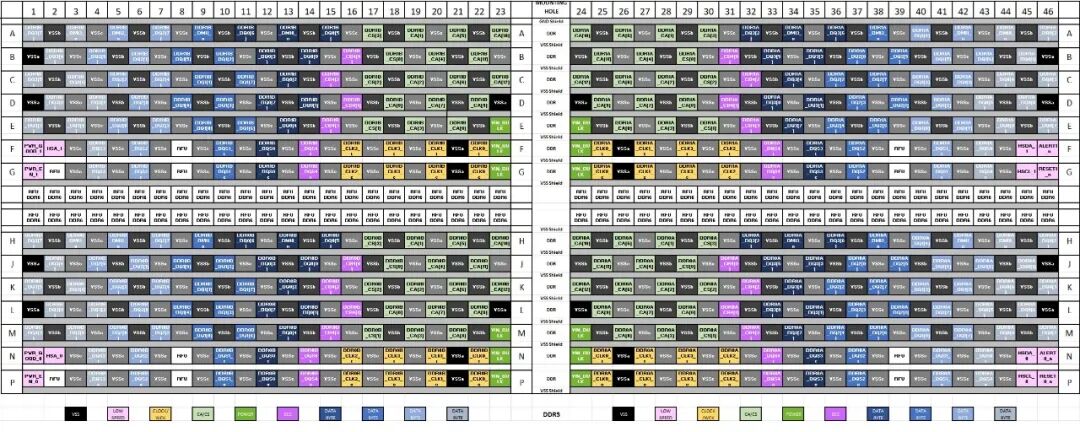

DDR5 CAMM2

LPDDR5/5X CAMM2

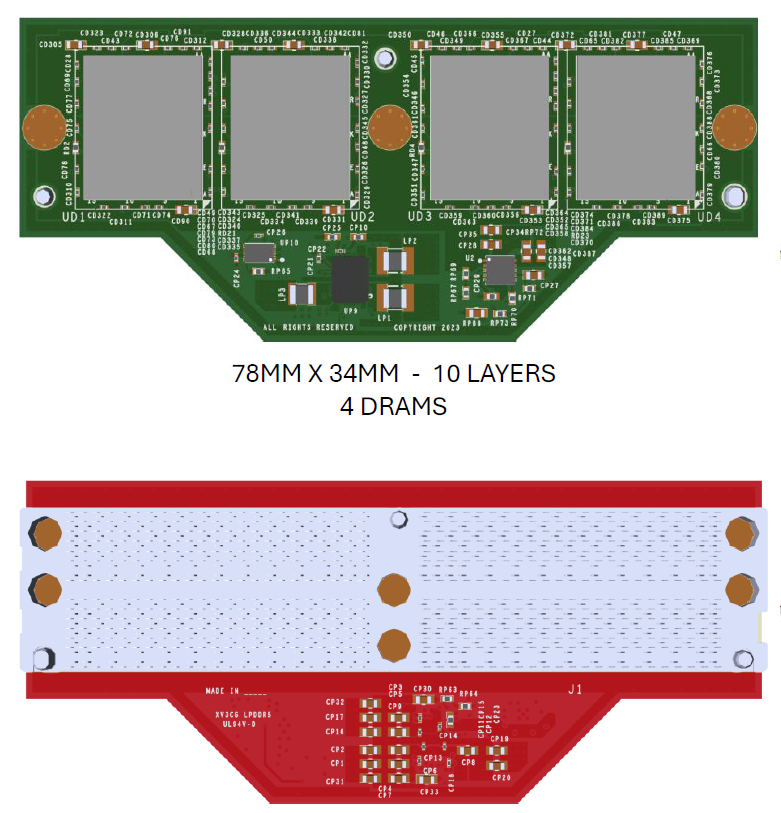

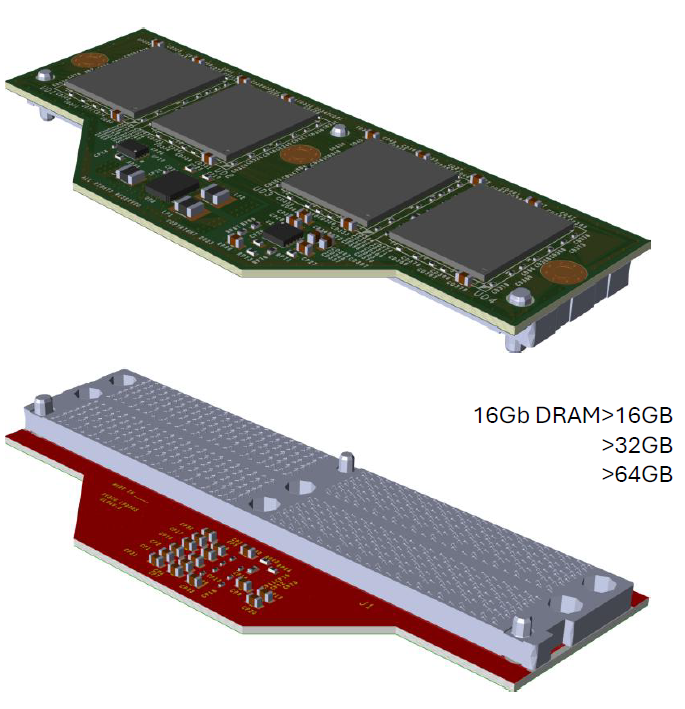

LPDDR5/5X CAMM2 Layout 理念

Layout 理念

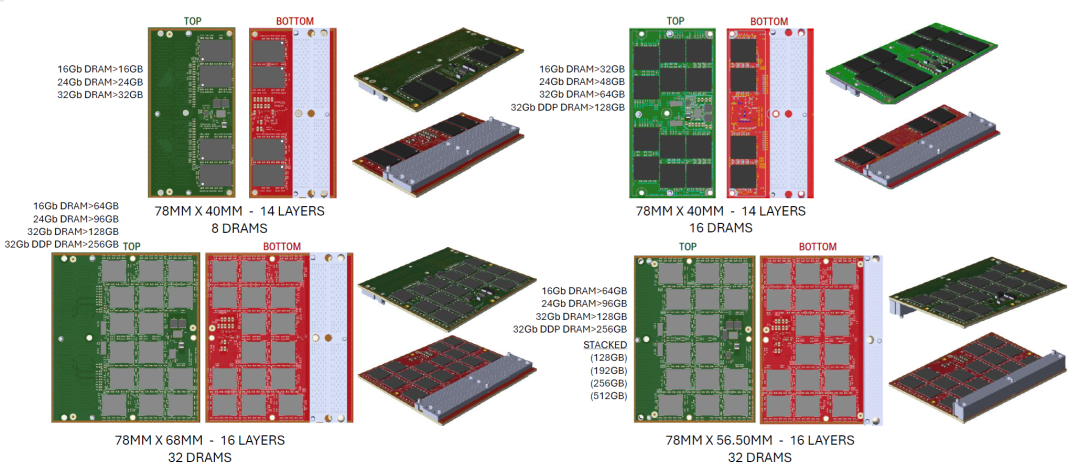

DDR5 外形规格

LPDDR5 外形规格

通过 LPDDR5 silicon stacking 实现 16, 32, 64GB 容量

美光率先推出基于 LPDDR5X 的 LPCAMM2 内存,转变 PC 用户体验

Layout 要求

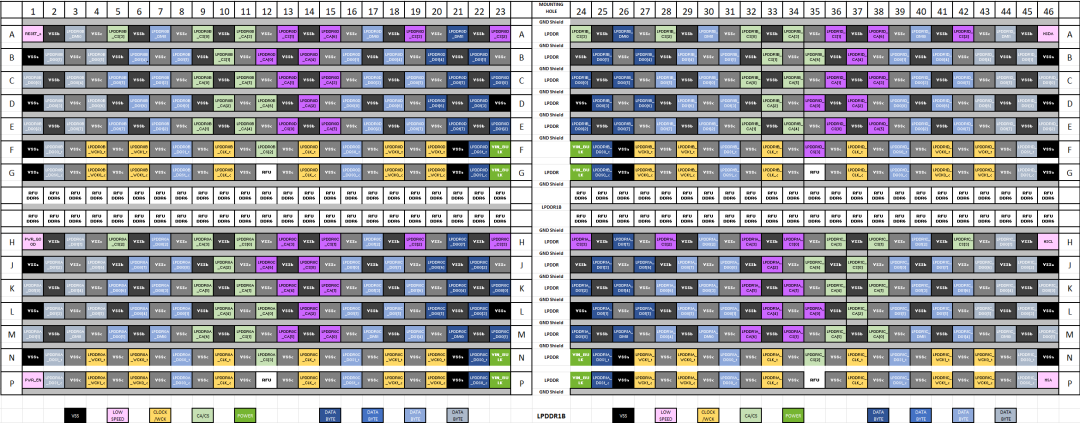

DDR5 Pinout

LPDDR5 Pinout

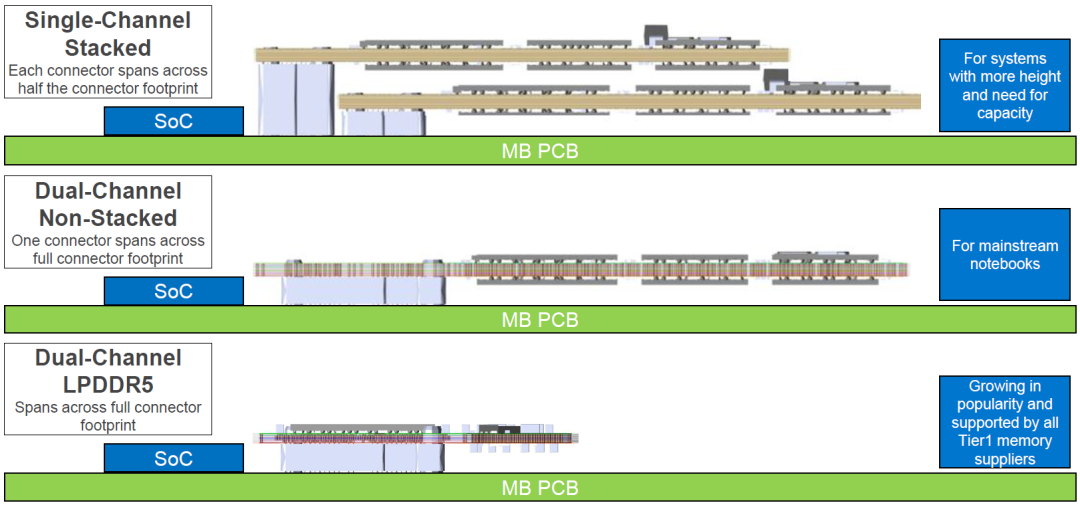

单通道 VS 双通道

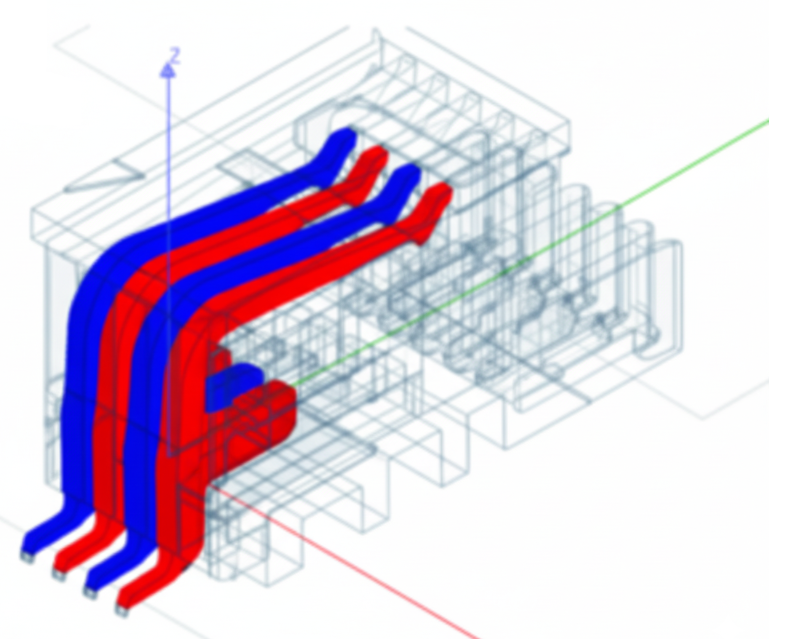

主板 PCB CAMM 安装

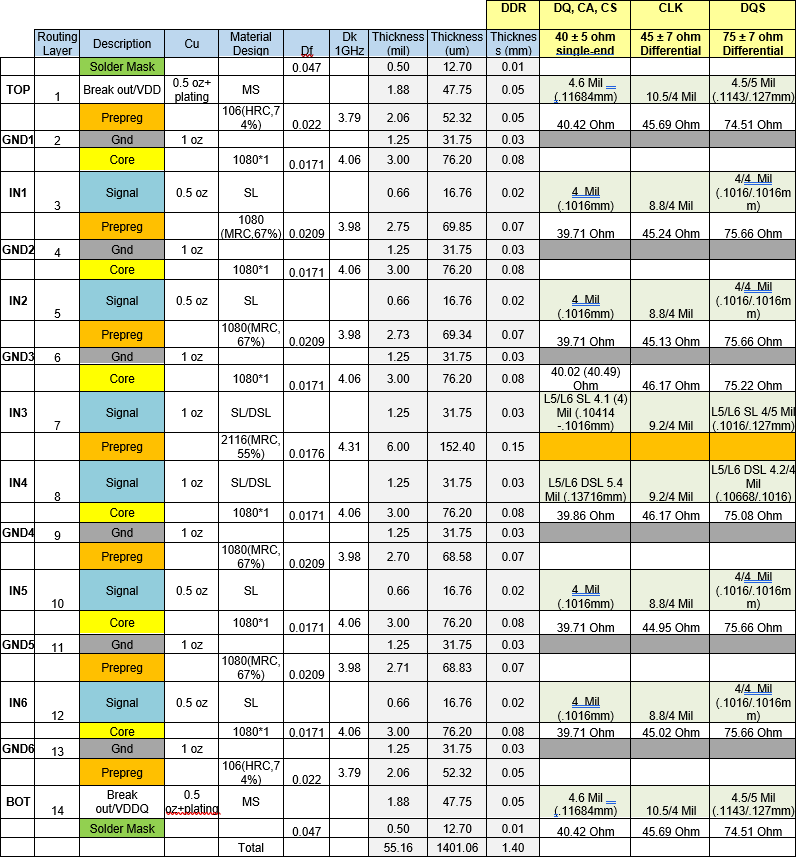

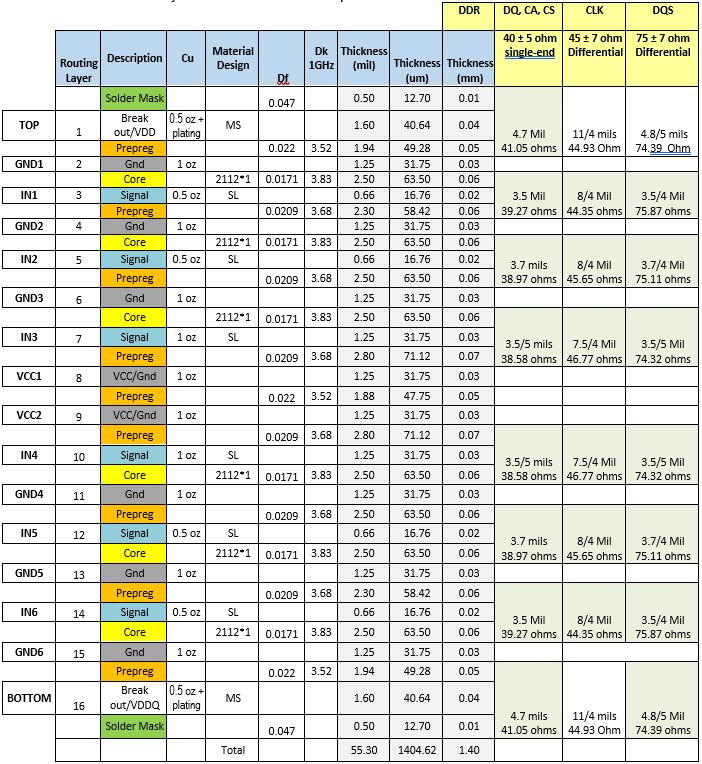

层叠

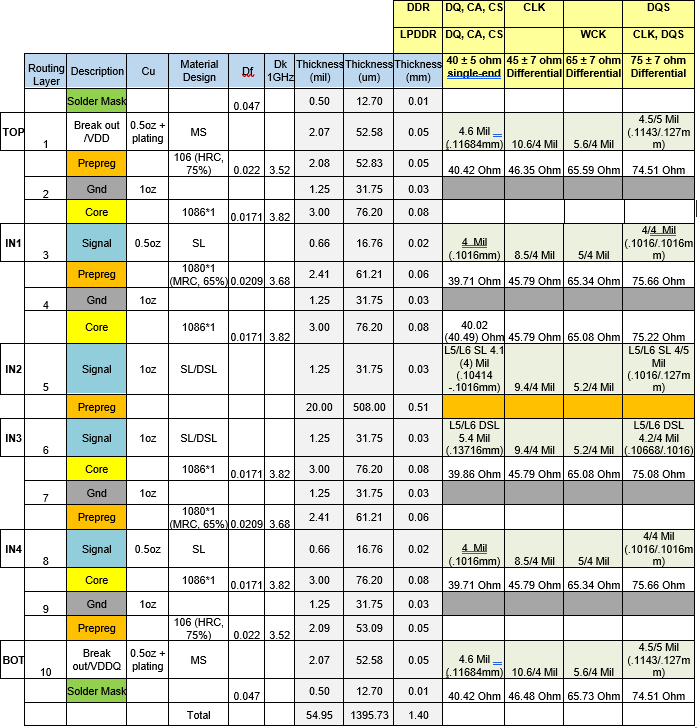

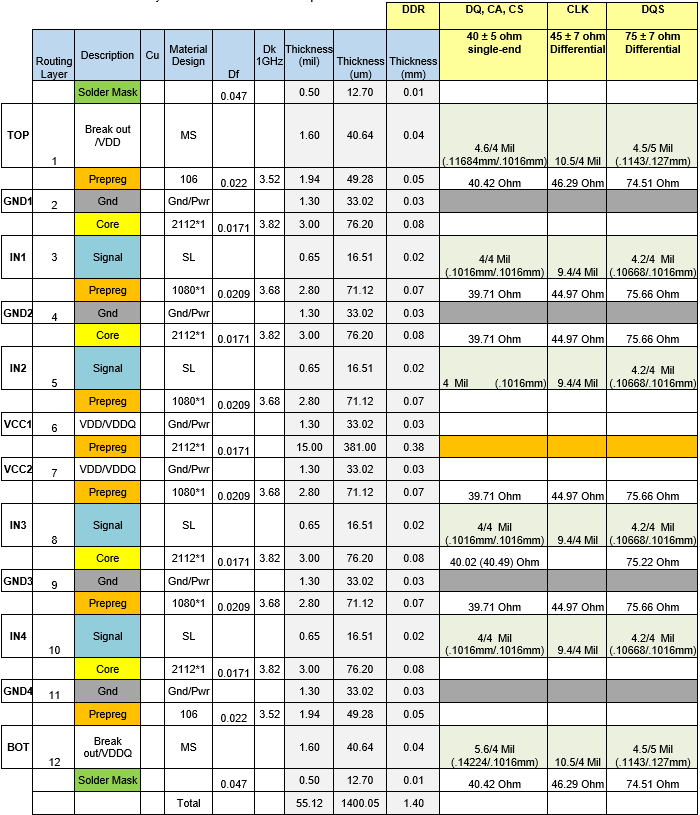

多种因素影响模块堆叠结构的定义,模块供应商会与 PCB 供应商一起,根据材料特性、材料可用性、电气性能和成本等多种因素来定义其堆叠结构。

DDR5 CAMM2 14 层层叠:

DDR5 CAMM2 16 层层叠:

DDR5 及 LPDDR5 CAMM2 10 层层叠:

DDR5 CAMM2 12 层层叠:

模块拓扑结构

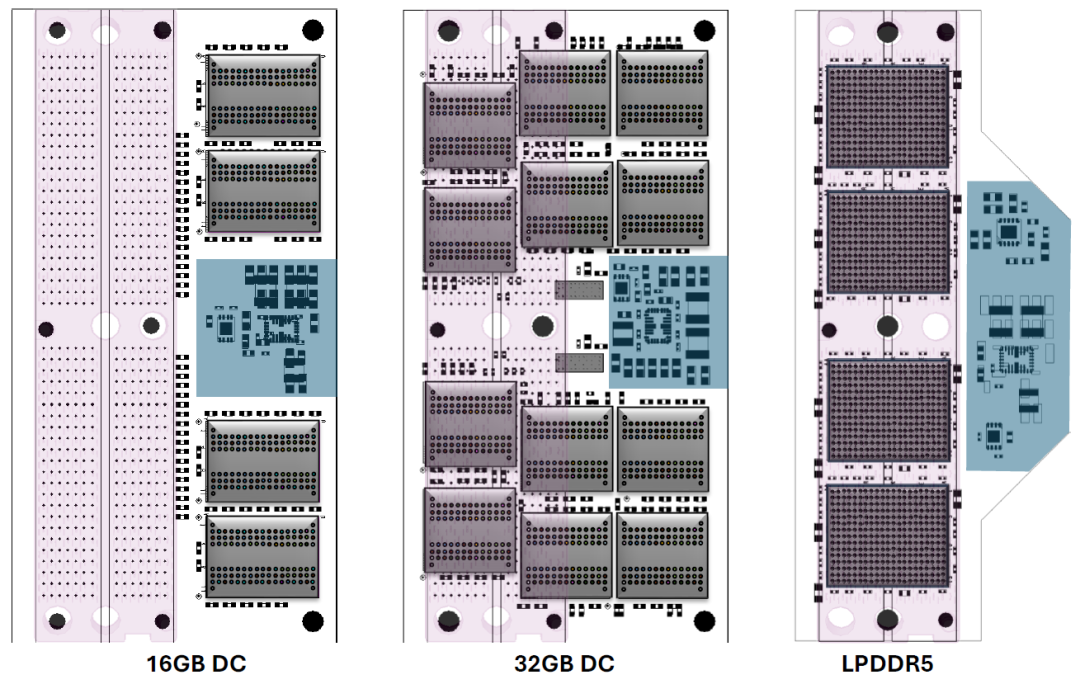

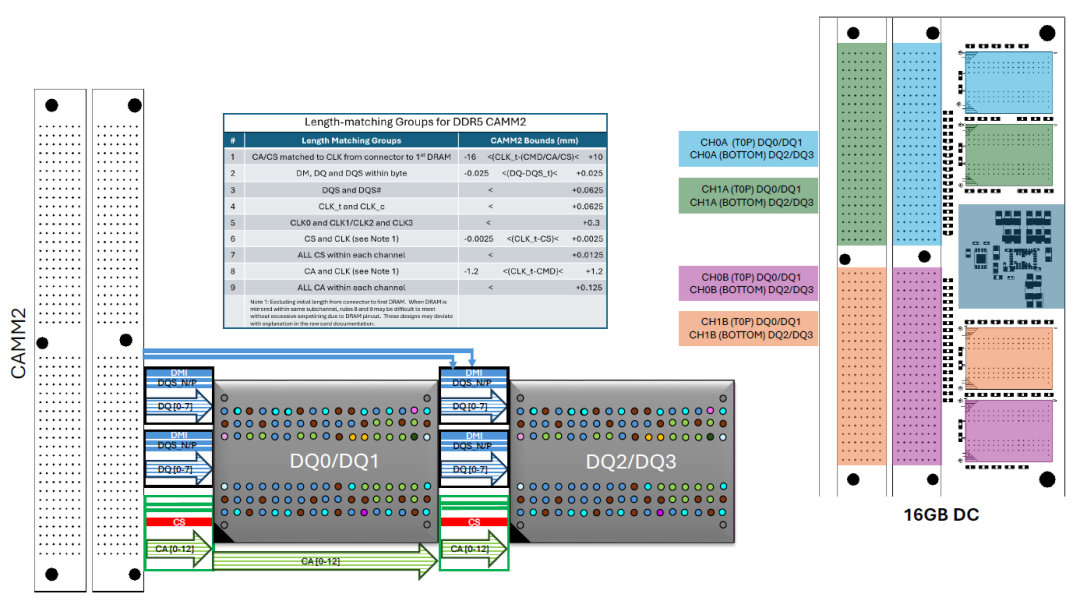

16GB 双通道,32GB 双通道及LPDDR5

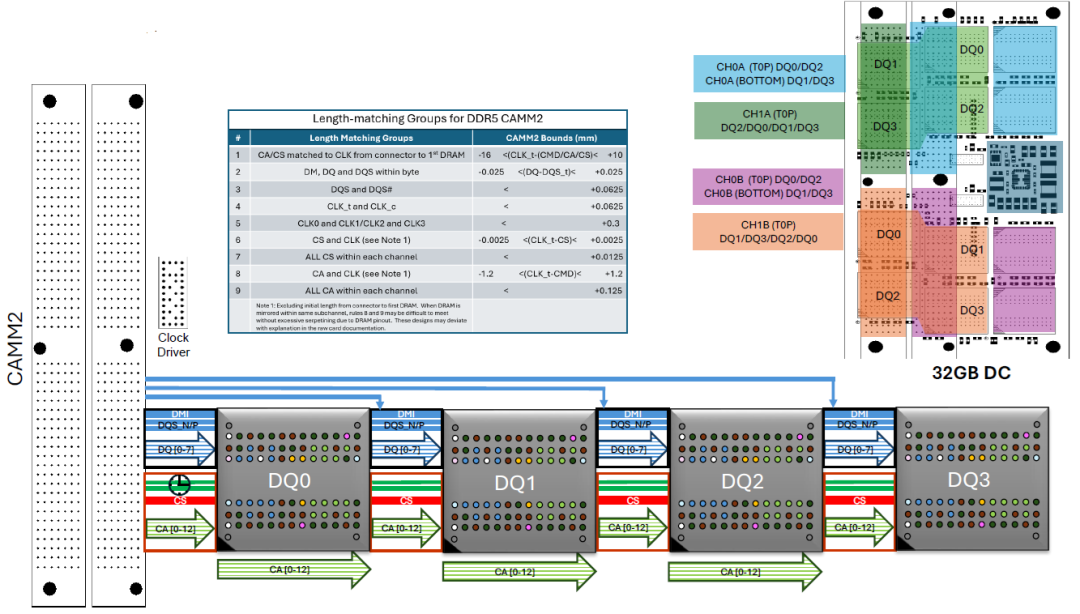

32GB DC:16颗 DRAM 顶层12颗,底层4颗

LPDDR5:顶层4颗DRAM

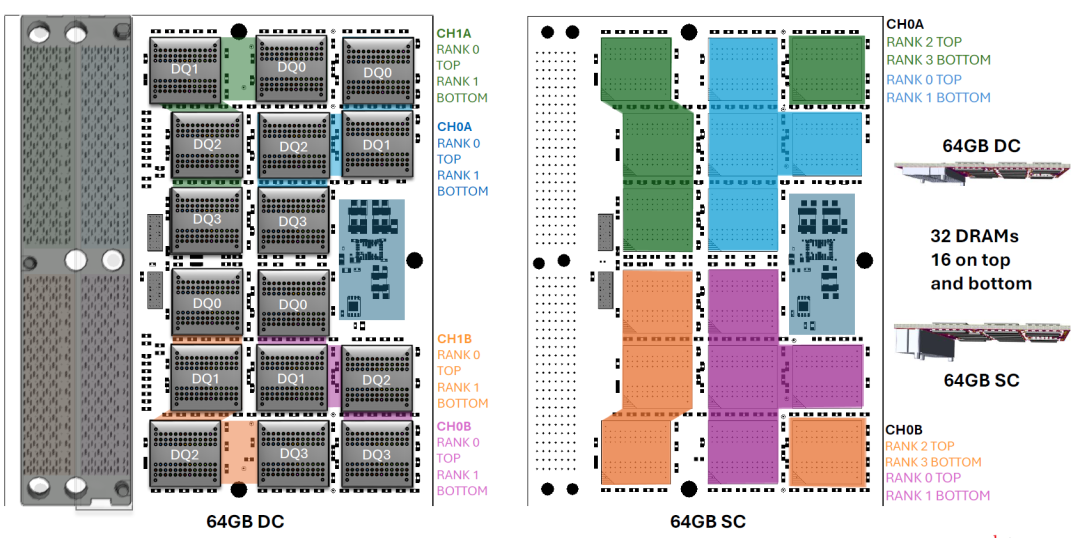

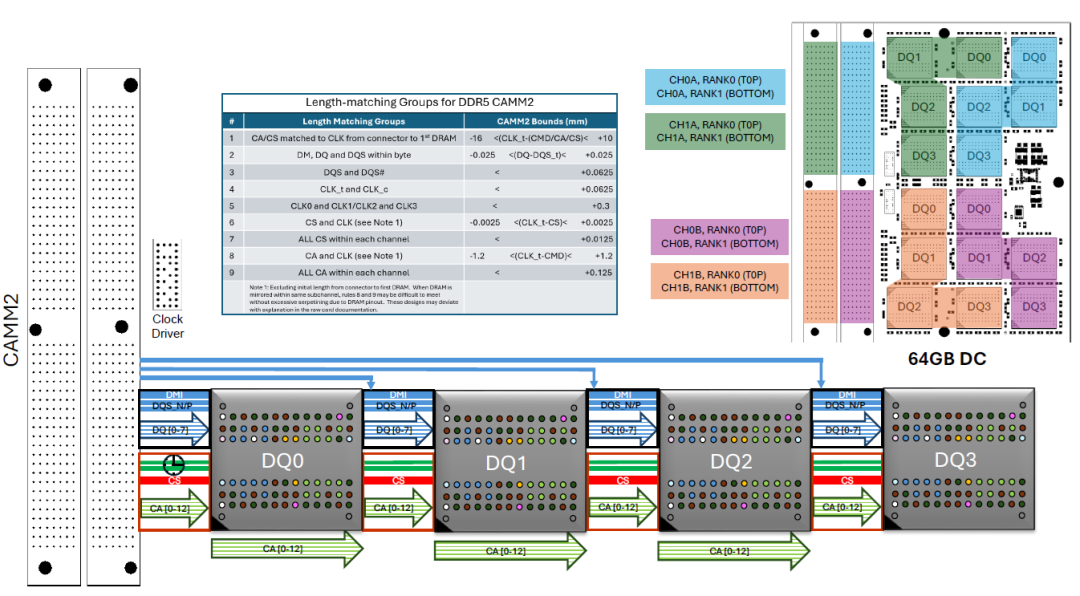

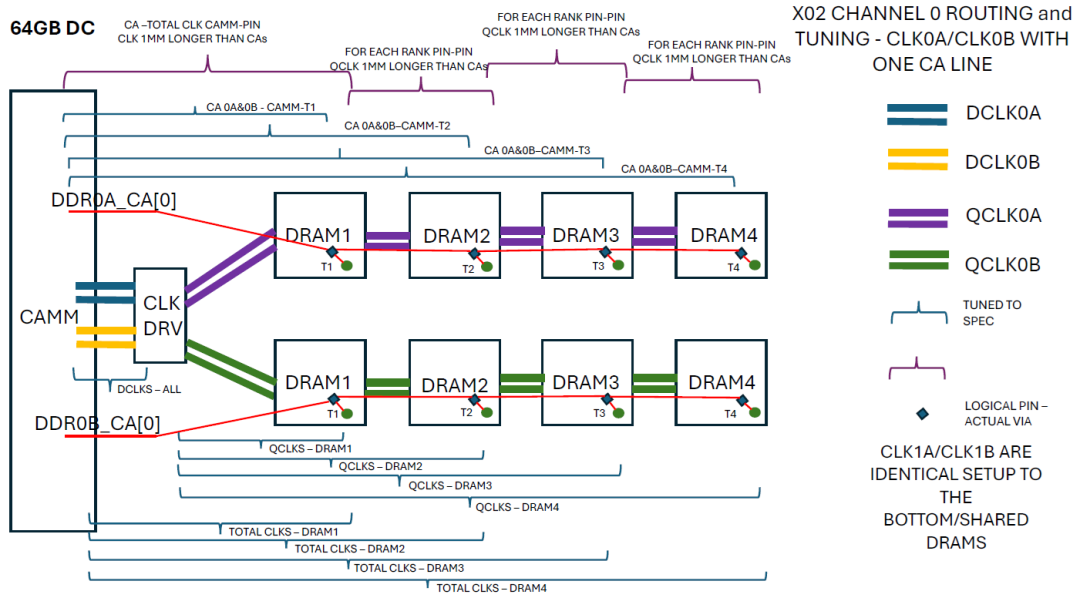

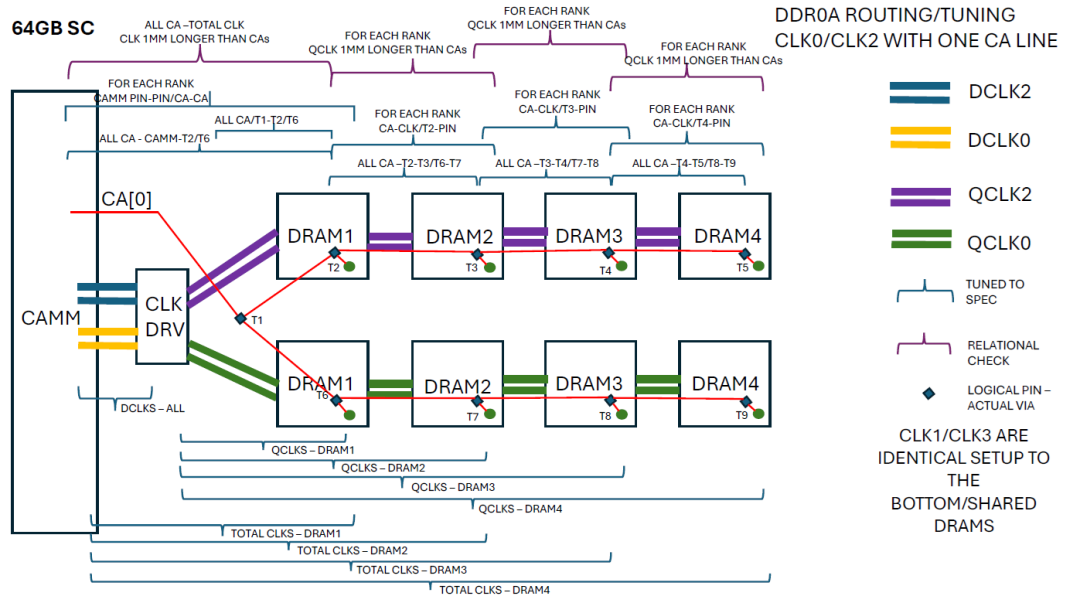

64GB 双通道及 64GB 单通道

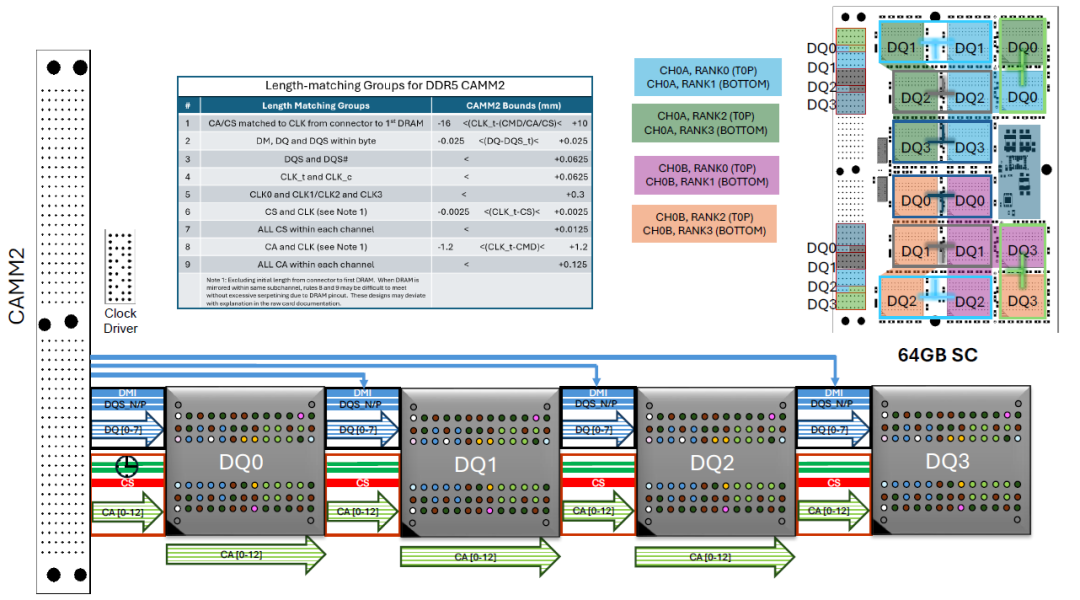

线长匹配(Length Matching)

CAMM2 DDR5 线长匹配规范:16GB 双通道: 32GB 双通道:

32GB 双通道: 64GB 双通道:

64GB 双通道:

64GB 单通道:

64GB 单通道:

LPDDR5:

LPDDR5: 偏移(Offset)

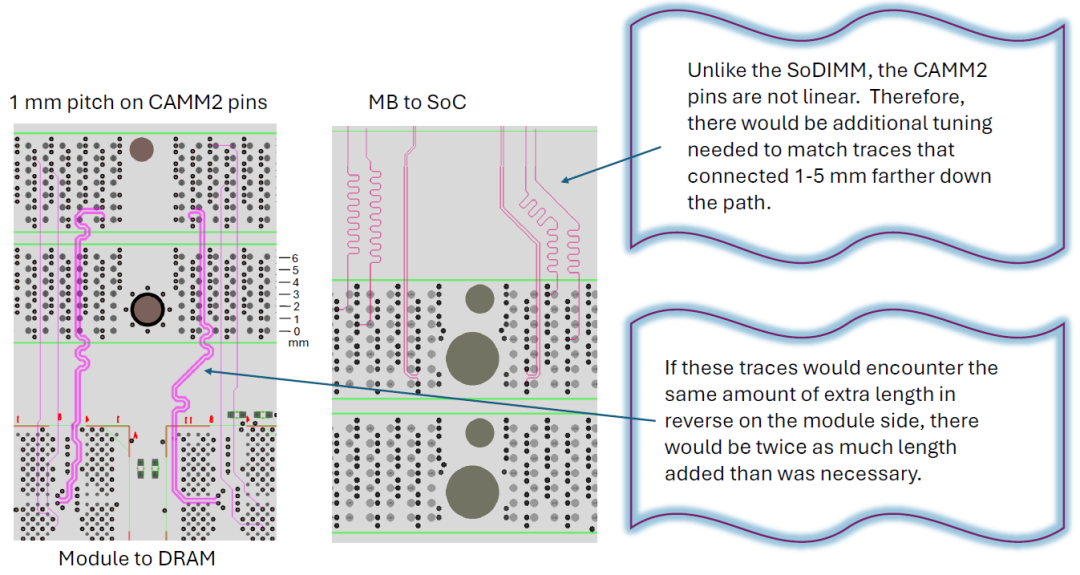

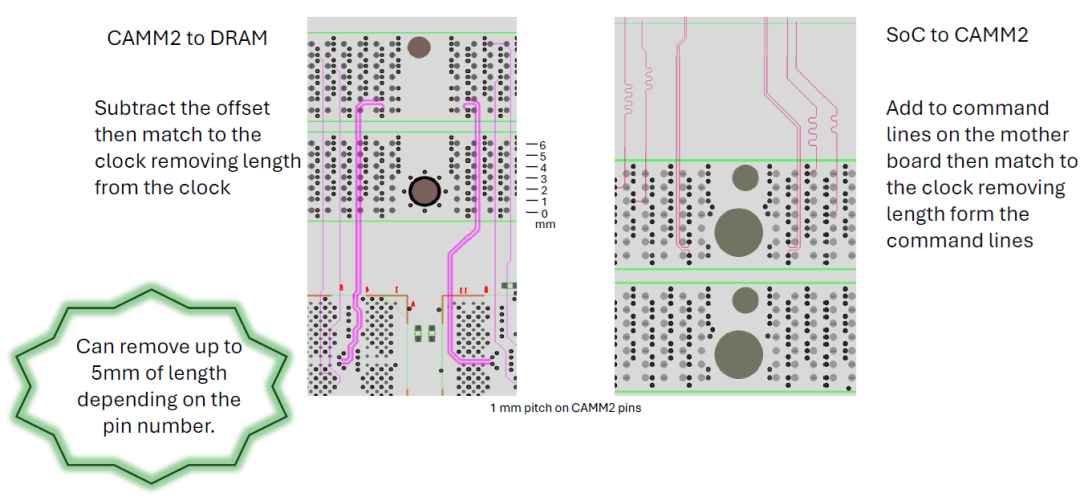

偏移(Offset)与 SoDIMM 不同,CAMM2 引脚不是线性的。因此,需要额外的调谐来匹配连接到路径下游 1-5 毫米的走线。

如果这些走线在模块侧反向遇到相同数量的额外长度,那么增加的长度将是必要的两倍。

解决方案:实现一个在长度匹配时应用的偏移量。在 CPU 一侧,将 CA[0] 增加5mm,然后与时钟匹配。在模块一侧,从 CA[0] 减去5mm,然后与它的时钟匹配。这样可以使整体长度匹配,但实际增加的长度较少。

解决方案:实现一个在长度匹配时应用的偏移量。在 CPU 一侧,将 CA[0] 增加5mm,然后与时钟匹配。在模块一侧,从 CA[0] 减去5mm,然后与它的时钟匹配。这样可以使整体长度匹配,但实际增加的长度较少。

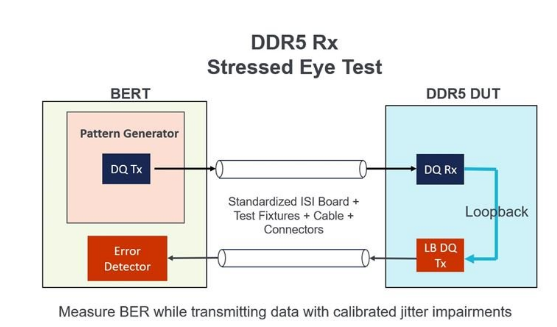

信号完整性

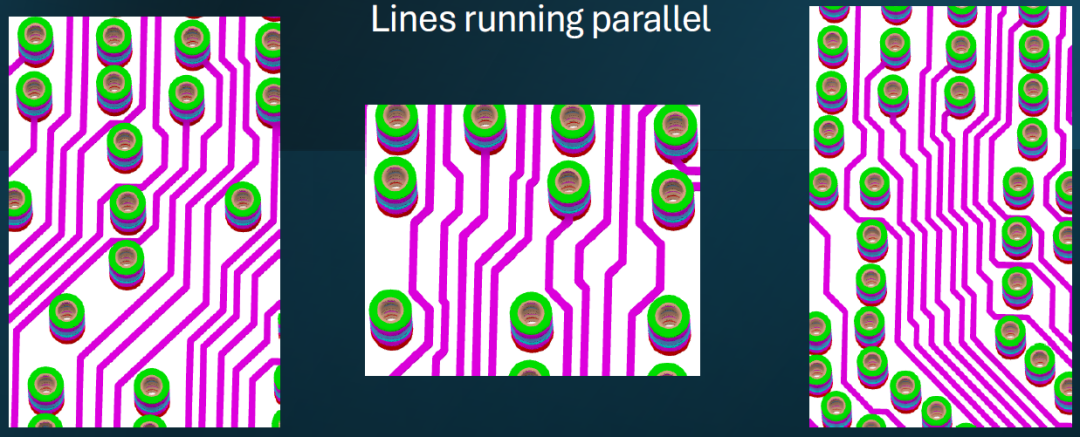

串扰(Crosstalk)仿真是消除串扰的最终检查。现在 PCB 设计软件包开始提供价格合理的仿真选项,以便在设计时进行仿真。以下是为消除串扰的DDR5 仿真规则:- 间距

- 线长匹配

- 走线宽度

- 接地屏蔽

- 接地过孔

- 沟槽(MOATS)

消除串扰的关键部分。这些 DDR5 规则未作为标准记录。

走线最小间距建议:

• 时钟-时钟=> .25 mm

• 时钟到 CA => .3 mm• CA 到 CA => .15 mm

• DQ 到 DQS => .18 mm• DQ 到 DQ => .18 mm

-

字节到字节 => .3 mm

-

WCK 到 DQ => .375 mm

-

WCK 到 DQS => .375 mm

-

子通道到子通道 => .5 mm

间距越大越好!

最小化走线平行的区域。即使是很小的中断也有助于减少串扰。

线长匹配(Length Matching)

线长匹配(Length Matching)-

主板上或带有板载内存的长度匹配取决于 SoC。

-

如果在模组上,必须符合 JEDEC CAMM2 通用标准。

-

线长匹配的详情已在上文中介绍。

走线宽度对于匹配目标阻抗非常重要。实际宽度取决于电路板层叠结构。

DDR5 目标是:

-

DQ/CA/CS => 40 Ohm

-

DQS => 75 Ohm

-

时钟 =>

-

主板上 75 Ohm

-

模块上从 CAMM 到时钟驱动器 75 Ohm

-

模块上从时钟驱动器到 DRAM 45 Ohm

-

LPDDR5:

-

DQ/CA/CS => 40 Ohm

-

DQS/CLK => 75 Ohm

-

WCK => 65 Ohm

-

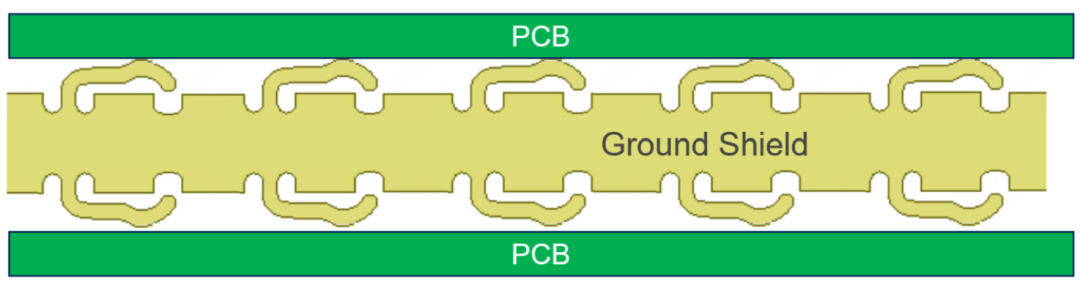

接地屏蔽对高速线路非常重要。

-

每条高速线路的上方和下方都应有接地平面。

-

相邻接地平面应至少覆盖高速线路一个走线宽度。

-

在紧密走线之间有少量接地平面可以显著减少串扰。

-

尽可能将接地过孔放置在所有信号缝合过孔附近,尽可能一对一。

-

策略性放置的接地过孔可以将信号的串扰降低多达 15 mV

-

所有差分对周围以及层变化处都需要接地过孔。

-

沟槽是围绕高速线路的参考平面中的任何断裂。

-

打开所有参考平面以突出显示可能的沟槽非常重要。

-

走线绝不能进入过孔周围的间隙,特别是当它们合并到一个空隙中时。

-

需要在高速线路周围的上下层设置接地参考平面,确保包围每个走线段。

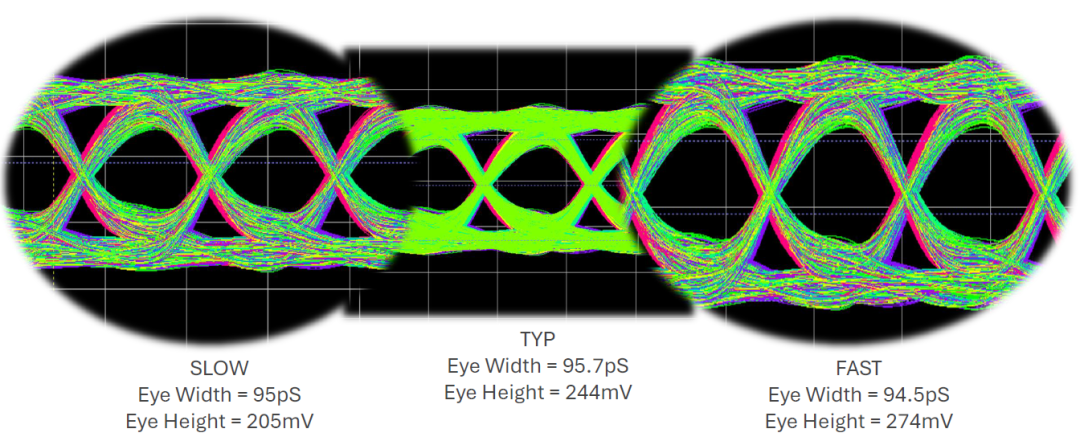

一个字节的仿真结果

一个字节的仿真结果

总结(Lessons Learned)

-

对不同设计阶段中的不断变化持开放态度。

-

没有什么是固定不变的,始终考虑所有的布局和连接选项。

-

在开始布线之前输入您的层叠约束,即使是初步的。

-

在调线长之前,利用可用的 DRAM 交换引脚选项来缩短走线长度。

-

记住永远不要在 nibble(半字节) 之外交换 DDR5 引脚。

-

使您的连接尽可能短。

-

在调线长之前,始终添加 SoC 封装长度并打开 Z 轴。

-

首先调时钟的长度。

-

不要忘记您的接地过孔,因为它们以后很难添加。

-

在表层高速走线之间添加接地参考平面和屏蔽。

-

远离沟槽,以避免串扰。

-

质疑规范和规则是可以的。

-

最重要的是永不放弃!

文中的部分图片和内容引用自 Charlene McCauly 以及 Terrie Duffy 的 “设计者眼中的 DDR5” 报告

-

DDR5

+关注

关注

1文章

483浏览量

25809

发布评论请先 登录

DDR5内存接口芯片组如何利用DDR5 for DIMM的优势?

DDR5 设计指南(一):DDR5 VS LPDDR5

新一代DDR5内存模组密集发布,支持DDR5 CPU随后就到!

涨价!部分DDR4与DDR5价差已达一倍!

Introspect DDR5/LPDDR5总线协议分析仪

DDR3/4都还没玩够,DDR5已经来啦

ddr5的主板可以用ddr4内存吗 几代CPU才能上DDR5

DDR5内存的工作原理详解 DDR5和DDR4的主要区别

Amphenol DDR5/LPDDR5 CAMM2连接器:高性能内存连接新选择

DDR5设计指南(二):什么是CAMM2?

DDR5设计指南(二):什么是CAMM2?

评论