随着芯片不断微缩,或是应用于诸如AI或机器学习系统的传感器等新器件。材料已经成为整个半导体供应链的一项日益严峻的挑战。

在高级节点上,工程材料不再可选。现在它们是一种需求,芯片中的新材料含量随着密度和功能的增加而不断增加。这在5nm及以上是显而易见的,但解决材料问题的趋势出现在并非所有产品都处于最新工艺节点的市场中。在安全性至关重要的市场对于器件寿命有着强烈需求,例如汽车、医疗和航空电子器件,以及工业应用领域,这些领域已将材料科学带到了半导体行业的前沿。

Brewer Science业务发展经理Dominic Miranda表示:“人们对AI的一个误解是认为它全是关于训练和推理的算法。但输入到这些系统的数据同样重要。在网络、工厂和城市中有很多传感器,并且有大量数据。所以数据的速度很重要,传感器对各种数据的反应速度也很重要。材料对于传感器对刺激作出反应的速度有很大影响。”

这个领域的研究目前正在进行,例如,用碳纳米管或石墨烯作为活性层的碳基技术。

Miranda表示:“用材料对这些器件进行功能化的方式会影响传感器的特性和感应方式。器件越复杂,你就越需要处理噪音。可能是环境噪音,例如机器运转或振动产生的噪音。我们发现市场正在朝着两个方向发展。你可以将传感器从货架上取下并应用到系统中,也可以使用定制设计来获得更清晰的信号。”

噪声是一个日益严重的问题,特别是在高级节点上,与老节点相比,高级节点的公差要小得多。虽然这曾经主要是对数字开关附近的模拟电路的挑战,但是在10 / 7nm及更低的栅极氧化层和更高的密度使电源、电磁干扰和热量产生的噪声成为日益棘手的问题,即使在数字电路中也是如此。

进军2D

在缩小器件方面面临的挑战之一是,像大多数材料一样,硅本身是三维的。即使硅层只有一个原子的厚度,它仍然包含从表面延伸出来的悬空键。这些键需要进行钝化,以避免不良的相互作用,并引入导致载流子散射和降低迁移性(carrier scattering and degrades mobility)的表面粗糙度。

相比之下,二维半导体中没有平面外键(out-of-plane bonds)。单原子层在结构上是“完整的”、自钝化的,从而减少或消除短沟道效应。

尽管如此,在可制造器件中开发这些有前途的结构特性仍然是个挑战。石墨烯是首个发现的二维半导体,没有带隙。在典型的操作温度下,黑磷不稳定。相反,目前的研究主要集中在如MoS2、WS2和WSe2等过渡金属二硫化物上。在4月份的材料研究协会春季会议和去年12月的IEEE电子器件会议上,有几篇论文对这些化合物的物理学和材料学问题进行了研究。

图1:2D二硫化钼(来源:MIT)

商业应用的第一个挑战是如何简单地制作二维材料。通过剥离可以获得大量的研究样品——通过使用胶带将石墨烯分离出来,以从块状石墨中拉出层——但制造的精度和质量要求需要更可控的方法。

虽然CVD是薄层沉积的显而易见的选择,但二维材料的CVD比乍看起来更复杂。例如,2D材料可以放在基板上,但不会与其键合。因此,生长2D半导体通常涉及从半导体单层下面蚀刻或烧蚀成核层,以分离它。加州大学洛杉矶分校化学和生物化学教授Xiangfeng Duan在一次演讲中解释说,器件所需的多层堆叠需要仔细注意与基板之间、堆叠组件之间以及工艺气体之间的化学兼容性。适用于单层的工艺条件会导致下一层发生化学降解或热降解。

但是,当二维半导体异质结构成功沉积时,结果会非常显着。Duan的小组制作了原子级厚度的横向WSe2/WS2 p-n二极管,这两种材料沿着一条量子线相互作用。对于垂直堆叠,他们正在研究在现有堆叠中插入电无源材料(electrically passive materials)。这种方法可能会将单分子层彼此分离,而不会增加基地去除的复杂性。

然而,仅仅分离单个层是不够的。在二维材料中,缺陷可以完全阻止载体的运动:它们不能离开平面去寻找另一条路径。加州大学伯克利分校的电子工程和计算机科学教授Ali Javey在他的光电器件研究报告中指出,缺陷是非辐射重组中心(non-radiative recombination centers)。因此,量子产率给出了一个合理的缺陷水平的度量。

一旦获得高质量的半导体材料,低阻接触(, low-resistance contacts)就成为下一个挑战。具有良好的电子移动能力的接触(A contact with good electron mobility)可能会阻碍空穴,反之亦然。Javey的团队展示了光电发射装置,他们使用交流电来提供第一个空穴,然后是电子,这些电子在脱落的MoS2层中重新组合,从而发出光。相比于分离材料,在生长材料中,基底的热膨胀系数可用于控制沉积膜中应变的大小,改变带隙和发射特性。

在IEDM上发表的研究中,博士生Xuejun Xie和加州大学圣巴巴拉分校的同事描述了光敏MoS2 FET在人工视网膜器件中的应用。这种器件对于神经形态学图像识别有潜在的应用价值。虽然忆阻交叉条阵列经常被提议用作人造突触,但它们不能直接“看到”图像。

捕获图像信息并将其写入交叉开关阵列是潜在的重大瓶颈,可能通过将图像感应和分析结合在单个器件中来缓解这一瓶颈。为此,圣巴巴拉小组在半导体MoS2通道上使用电子束模式创建了金属MoS2量子点阵列。量子点从半导体的传导带吸引大量电子,将费米能级移动到价电子带。孔洞受到限制,增加了电阻。随着电流的流动,移动电子与空穴重新结合,导致电阻随时间衰减。在光源开启的地方有更多的载流子,所以器件“检测”并“记住”图像的明亮部分。

即使在石墨烯被发现14年后,基于2D半导体的器件仍处于起步阶段。

柔性材料

目前材料工程的挑战之一是超越标准的芯片格式。有一波全新的柔性混合电子产品,包括薄膜温度传感器、电子墨水等,每一种都有其独特的特性和挑战。而且他们正在使这些材料在一系列新的,有时甚至是意想不到的操作条件下按计划运行变得困难得多。

ANSYS公司半导体事业部首席技术专家Norman Chang表示:“有一系列传感器可以检测葡萄糖、pH、湿度和温度。问题是,我们正在使用不同的热梯度解决方案的组件,这可能会对性能产生影响。你实际上是在研究3D几何输入,这需要对柔性基地和封装进行协同仿真,因为它们会影响这些器件的电气性能。这一切都必须一起模拟。如果你研究印刷RF,毫米波的表现在不同的区域可能是不同的。”

正在开发的新方法之一被称为几何缠绕(geometry wrapping),通过这种方法,电路可以缠绕在任何设备上,甚至跨越建筑物延伸(even stretched across buildings.)。例如,美国空军研究实验室今年早些时候宣布,它正在与NextFlex共同开发一种用于军事和商业应用的物联网传感器应用的柔性电路系统。目标是实现可伸缩电子器件,能够承受高G载荷和温度。

柔性传感器也被用于水和环境测试等应用。Brewer Science公司的 Miranda表示:“在水测试中,挑战在于设计一个传感器来忽略一切,只考虑你想要测试的东西。这不适用于固态材料,但它确实适用于灵活的传感器。你可能听过YouTube上的视频,有些人听到Yanni,有些人听到Laurel,这取决于他们听到的波长。但材料可以用来确保你听到的是你应该听到的东西,并且可以使用它们来检测您想要检测的内容。”

结论

电子工业对材料工程的重视程度越来越高,并将继续变得更加普遍。虽然器件微缩对于新材料来说是一个显而易见的领域,例如自动驾驶、人工智能、5G以及工业和医疗应用,在这些领域中,电子器件在过去扮演的角色更为有限。

并非所有这些都会使用传统芯片,并且许多芯片对灵活性、噪声灵敏度和信号吞吐量都有特定的要求。

-

芯片材料

+关注

关注

0文章

10浏览量

9042

原文标题:芯片材料的新选择

文章出处:【微信号:cas-ciomp,微信公众号:中科院长春光机所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

一文告诉你最全的芯片封装技术

如何创建ServiceAbility,一文告诉你

一文告诉你单片机的功耗怎么算的

一文告诉你如何用好AD797

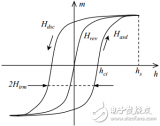

一文告诉你!Maxwell如何对磁滞材料进行建模

一文告诉你!如何选择合适的嵌入多操作系统

一文告诉你智能制造的基石是什么

服务器ups运行时间,图文告诉你关于UPS电源的一些基础知识

一文告诉你绕线电感线圈在使用中为什么会有噪音

一文告诉你,大电流防水连接器怎么选

一文告诉你芯片材料的新选择

一文告诉你芯片材料的新选择

评论