随着无线系统的持续演进,其能够支持更多的连接设备和更高的数据需求,同时无线信号链的效率和精度也变得至关重要。信号链中的基本要素之一是信道估计,即系统实时推断无线通信路径特性的过程。信道估计不准确会导致吞吐量下降、时延增加并降低系统可靠性等多重问题。

多年来,行业一直采用最小二乘法 (LS) 和最小均方误差 (MMSE) 等传统技术,但这些技术在低信噪比 (SNR) 环境或高移动性场景中已显不足。随着网络复杂度的不断提升,行业对更智能的自适应算法的需求也与日俱增。

将 AI 引入信号链

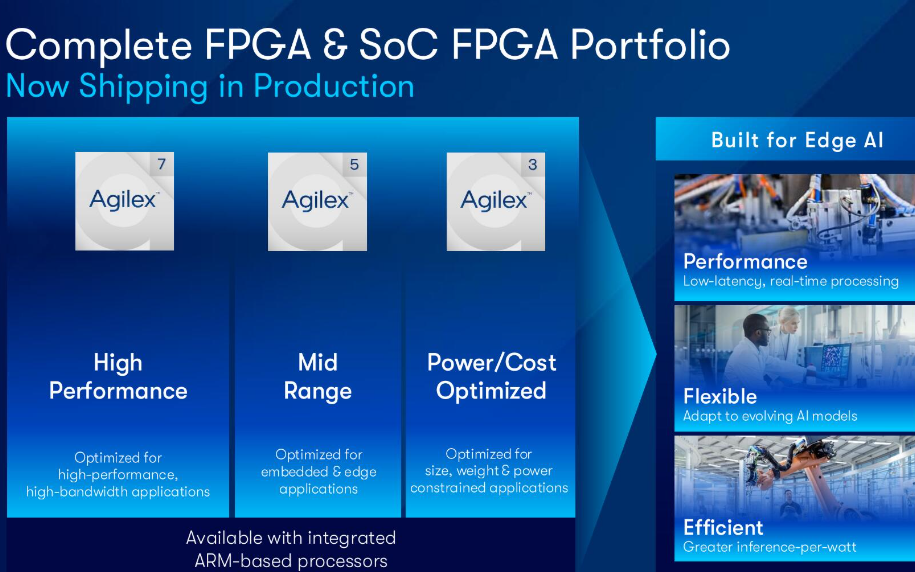

Altera 利用 FPGA AI 套件,在Agilex SoC FPGA上部署基于 AI 的信道估计,不断突破技术边界。与传统方法相比,将卷积神经网络 (CNN) 集成至信道估计流程,可助力工程师在具有挑战性的情况下,依旧实现显著性能提升。 本次测试使用 MATLAB 进行了初始信号处理实验,然后利用工具链将训练好的 CNN 模型部署至 FPGA。结果令人瞩目:

在 -10 dB 至 0 dB 信噪比区间,吞吐量较 MMSE 方法提升约 20%;

在信噪比更高的情况下,实现了同等或更优性能表现;

通过高效硬件映射,降低了时延与资源占用。

这些优势不仅仅停留在理论层面,更能转化为更优的用户体验、更稳定的网络表现以及全方位的频谱效率提升。

对 RAN 未来发展的重要意义

现代无线接入网 (RAN) 系统,特别是大规模多输入多输出 (mMIMO) 和开放 RAN 架构,需要具备实时响应能力,并能以更小的开销适应信道变化。FPGAi 通过将可编程逻辑的并行性和灵活性,与擅长识别复杂模式且经训练的 AI 模型相结合,使这一目标成为可能。 借助 Agilex SoC FPGA,设计人员可将 AI 驱动的信道估计无缝集成至物理层 (PHY),而无需片外加速器或进行繁琐的后处理流程。

智能估计赋能智能网络

在无线网络管线中,信道估计仅是受益于 AI 原生架构的环节之一。作为 Altera“利用 FPGAi 重塑无线接入网”战略的重要组成部分,这一解决方案展现了通过将特定领域 AI 与可编程逻辑相结合,可在性能、灵活性和效率方面实现立竿见影的显著提升。

-

FPGA

+关注

关注

1655文章

22287浏览量

630331 -

soc

+关注

关注

38文章

4514浏览量

227635 -

Altera

+关注

关注

37文章

818浏览量

158164 -

AI

+关注

关注

89文章

38121浏览量

296693 -

信号链

+关注

关注

0文章

233浏览量

30448

原文标题:Altera SoC FPGA 如何助力实现 AI 信道估计?

文章出处:【微信号:英特尔FPGA,微信公众号:英特尔FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Altera Agilex 5系列FPGA与SoC产品荣膺2025全球电子成就奖

Altera Agilex 5 D系列FPGA和SoC家族全面升级

Altera FPGAi解决方案助力mMIMO系统性能提升

Altera Agilex 3 FPGA和SoC产品家族的性能分析

Altera进一步扩展 Agilex™ FPGA 产品组合,全面提升开发体验

Altera Agilex 3/5 FPGA和SoC的功能特性

使用Altera SoC FPGA提升AI信道估计效率

Altera Agilex 3 FPGA和SoC产品介绍

Altera SoC FPGA如何助力实现AI信道估计

Altera SoC FPGA如何助力实现AI信道估计

评论