测量对于确定 IC 的 EMC 特性是必要的。只有准确了解 IC 的 EMC 特性,才能在生产前采取有效的预防措施,提高产品的抗 ESD 能力和 EMC 性能,避免后期因 ESD 干扰导致的产品故障和成本增加等问题 。

三、集成电路ESD 测试与分析

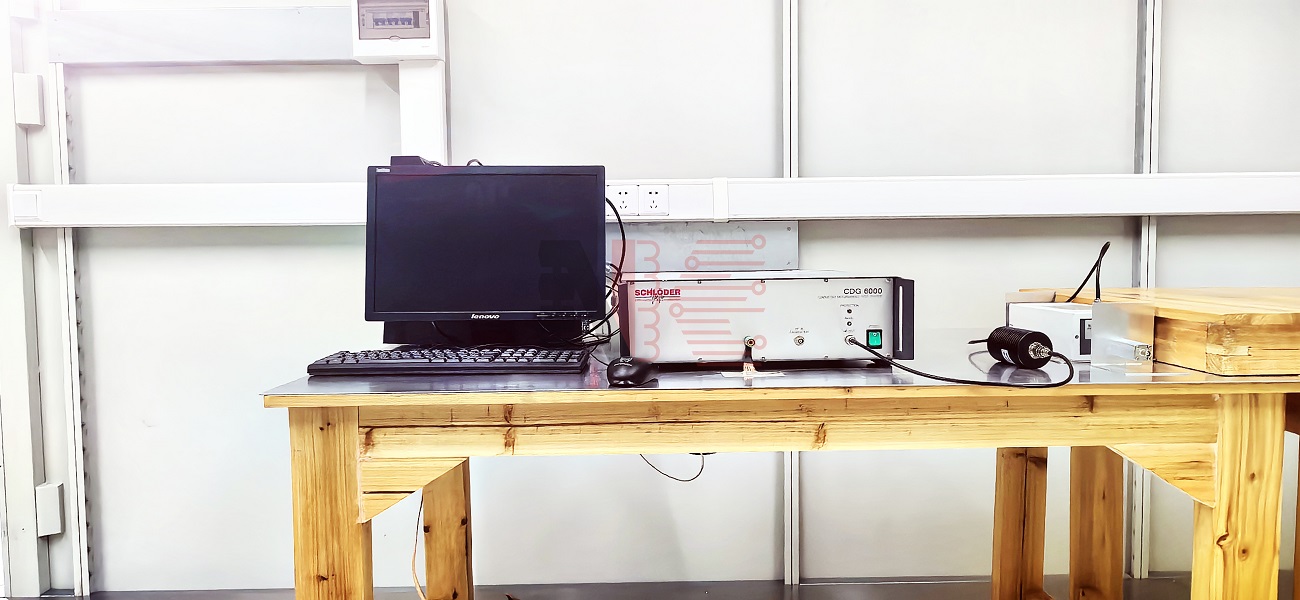

1、测试环境与电场产生

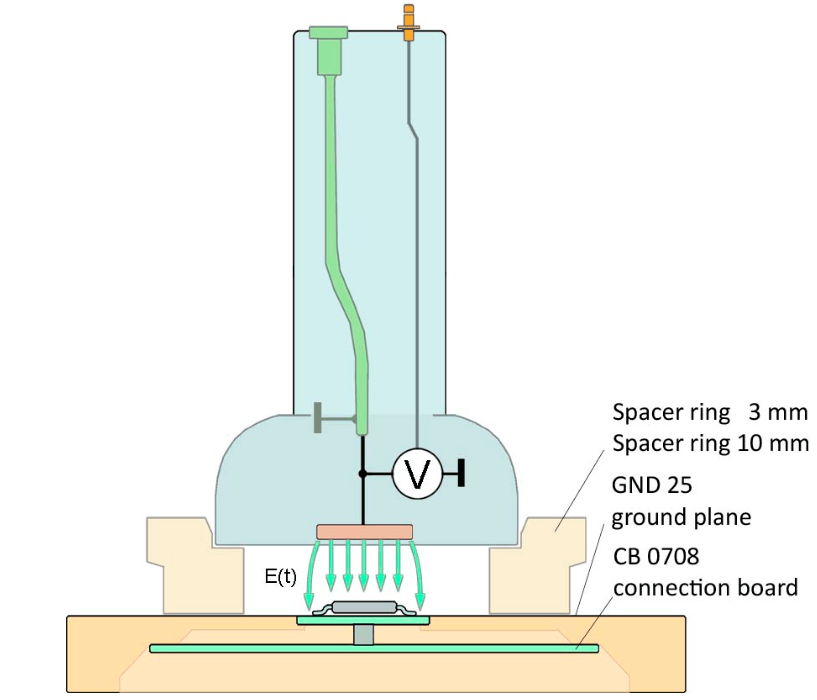

图5 使用 ESD 发生器的测量设置l 测试环境,集成电路(IC)被放置在一个由接地平面、隔离垫圈环和场源形

成的屏蔽空间内。接地平面:可起到接地保护和屏蔽电磁干扰的作用;隔离垫圈:用于确定场源与IC之间的距离;场源:则是产生电场的关键部件;通过隔离垫圈,场源被设置在集成电路上方特定高度处。场源包含一个电极,测试电压脉冲会被施加到该电极上,电极进而产生一个确定的电场,集成电路就处于这个电场之中。这种设置能够为集成电路提供一个可控制且相对稳定的电场环境,以便进行相关测试.

l 场源可以产生多种在实际中可能出现的测试脉冲。例如,在实际使用中,脉

冲的上升时间可能会出现 200 皮秒、1 纳秒和 5 纳秒等不同情况,这使得

测试能够更贴近真实的工作场景,更准确地评估集成电路在各种实际电场条件下的性能。

l 测试过程中,电极电压会逐渐增加,直至达到集成电路的抗扰度水平。通过

这种方式,可以确定集成电路在不同电场强度下的耐受能力,为评估其可靠性和稳定性提供重要依据。

2、静电放电事件中的磁场影响

l 在静电放电(ESD)事件期间,结构部件可能会产生额外的磁场. 例如,当

ESD发生时,放电电流会在结构部件周围形成磁场,这些磁场可能会与集成电路(IC)相互作用,从而干扰IC的正常运行。

l 利用相同的测量设置和一个磁场源确定IC的磁场抗扰度水平,这种方法能够

在相对统一的条件下,对 IC 抵抗磁场干扰的能力进行量化评估,以便更好地了解 IC 在不同磁场强度和频率下的性能表现。

l 故障模式分析:在进行上述测量时,需要对集成电路的故障模式进行分析。

在不同测试条件下出现的故障情况,如逻辑错误、输出异常、死机等,可以深入了解其在电场和磁场干扰下的薄弱环节,为改进设计和提高可靠性提供有价值的信息。

表 1 列出了针对一个微控制器的静电放电抗扰度测量结果,通常情况下,干扰脉冲上升时间越短,其频谱越宽,对 IC 的干扰能力可能越强。表 1 中的数据可以帮助工程师更直观地了解微控制器在不同 ESD 脉冲上升时间下的抗扰度性能,进而为系统级的 ESD 防护设计提供依据。

测量装置确定 EMC 参数,这些参数对于评估 IC 在电磁环境中的性能和兼容性至关重要,包括抗扰度、发射水平等指标。

3、关于集成电路受外部电磁场干扰的问题

如果电场或磁场从外部干扰集成电路,改变布局作为对策是不合适的。在这

种情况下,唯一有用的补救措施是改变机械设计。

l 屏蔽作用:通过改变机械设计,可以为 IC 增加有效的电磁屏蔽措施。例如,

使用金属外壳或屏蔽罩将 IC 包裹起来,这样可以阻挡外部电磁场的进入,从而保护 IC 免受干扰。

l 距离和方向调整:合理地调整 IC 与外部电磁场源之间的距离和相对方向,

也属于机械设计的范畴。增加距离可以降低电磁场的强度,而改变相对方向则可能使 IC 处于电磁场较弱的区域。如大型变压器周围的电磁场分布不均匀,通过调整 IC 的位置和方向,使其远离强磁场区域或与磁场方向平行,可以减少磁场对其的影响。

4、针对散热器强电场的具体应对措施

对于图 1 中的具体示例,可以采取以下对策,其中 IC 上方的散热器会产生强电场:

l 增加电子模块和散热器之间的接触弹簧数量,可以改善两者之间的热传导。

l 在集成电路(IC)上方布置局部屏蔽罩,如图 3 所示。这主要是为了减少外

部电磁场对 IC 的干扰,保护其内部的敏感信号和电路。如果可能的话,用屏蔽罩将模块全方位封闭起来,并可能配备穿心滤波器。这样做可以提供更全面的电磁屏蔽效果,防止外部电磁场进入模块内部,同时也能阻止模块内部产生的电磁辐射泄漏到外部。

l 将 IC 移动到无电磁场的一侧,但这样做会导致冷却无法进行。这是一种在

电磁兼容性和散热之间进行权衡的措施。当 IC 受到电磁场干扰问题较为严重,且其他电磁屏蔽措施难以实施或效果不佳时,可以考虑将其移动到远离电磁场源的位置。需要注意的是,该位置可能不利于散热,因此需要综合考虑 IC 的工作温度范围、散热要求以及电磁环境等因素。

l 增加 IC 和散热器之间的间隙:这样做可能会对散热产生一定的影响,但在

某些情况下,如需要避免两者之间的电气耦合或机械干涉时,是一种可行的方法。然而,这可能会导致散热效率下降,因此需要根据具体情况进行评估和优化,例如通过增加其他散热措施来弥补间隙增大带来的散热损失。

综上所总之,可以说,就开发抗干扰组件的时间和成本节约而言,提前了解微控制器的 ESD 参数是非常有益的。这意味着必须测量微控制器的 ESD 参数。该信息将允许在组件开发期间尽早规划必要的对策,以确保整个组件具有抗干扰性。

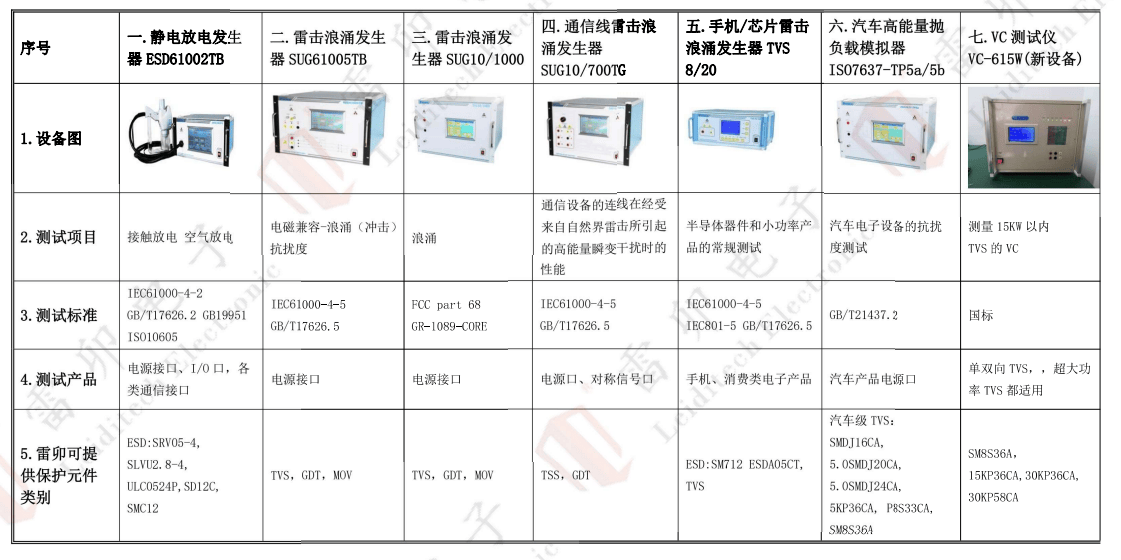

上海雷卯电磁兼容实验室,可以测试 IEC61000 系列标准:30KV 静电、1.2/50μS 和 8/20μS 浪涌、10/700μS 浪涌、10/1000μS 浪涌、ISO7637-2/5a/5b 抛负载、群脉冲 4KV EFT,半导体器件的性能 V-I 电感,电容测试,EMI 摸底等等。

检测设备/检测项目明细如下:

Leiditech雷卯电子致力于成为电磁兼容解决方案和元器件供应领导品牌,供应ESD,TVS,TSS,GDT,MOV,MOSFET,Zener,电感等产品。雷卯拥有一支经验丰富的研发团队,能够根据客户需求提供个性化定制服务,为客户提供最优质的解决方案。

审核编辑 黄宇

-

集成电路

+关注

关注

5464文章

12681浏览量

375672 -

ESD

+关注

关注

50文章

2422浏览量

180400 -

电磁兼容性

+关注

关注

7文章

505浏览量

34751

发布评论请先 登录

TH2839阻抗分析仪在LED驱动集成电路寄生参数测试分析中的应用

车载OBC电磁兼容性测试必要性分析报告

机器人电磁兼容性测试必要性分析

有源医疗器械电磁兼容性(EMC)测试必要性分析报告

单片机系统的电磁兼容性(EMC)设计

电磁兼容与电磁干扰在电磁兼容性大数据分析中的智能管理系统

PLC 系统的接地和电磁兼容性

Keithley静电计6514在电磁兼容性测试中的应用与优势

集成电路电磁兼容性及应对措施相关分析(三)—集成电路ESD 测试与分析

集成电路电磁兼容性及应对措施相关分析(三)—集成电路ESD 测试与分析

评论