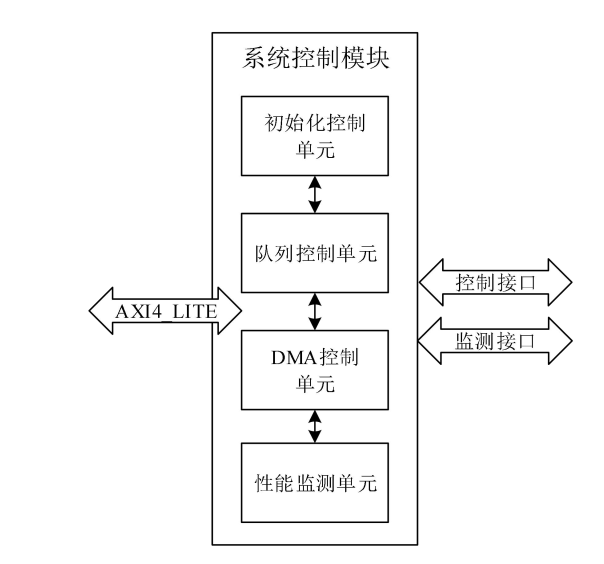

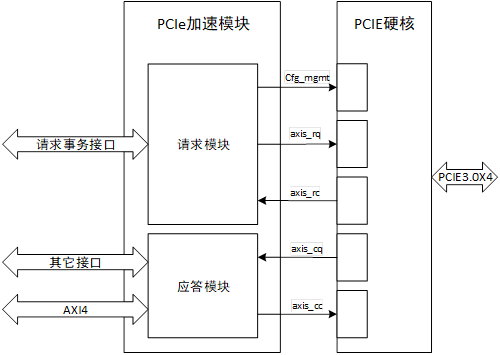

系统控制模块负责实现 NVMe over PCI 逻辑加速引擎的控制功能, 其结构如图 1 所示。 用户通过系统控制模块实现对初始化功能、 队列管理功能、 DMA 功能等主要功能的控制, 同时逻辑加速引擎的工作状态也通过此模块反馈给用户。 系统控制模块包含了初始化控制单元、 队列控制单元、 DMA 控制单元和性能监测单元。 在各控制单元和监测单元中包含了多个寄存器组, 用户可通过访问寄存器组的方式实现功能的控制和状态的监测。 为方便用户访问这些寄存器组, 系统控制模块采用 AXI4-Lite 总线作为接口, AXI4-Lite 接口具有低带宽、 低延时、 低复杂度的特点, 采用该接口可以简化设计逻辑和功耗, 同时作为标准协议接口可以更方便的集成到用户环境。

图1 NVMe over PCI 控制模块结构图

更多博文链接:https://blog.csdn.net/tiantianuser/article/details/148995285

审核编辑 黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

PCI

+关注

关注

5文章

689浏览量

134505 -

控制模块

+关注

关注

2文章

148浏览量

19872 -

nvme

+关注

关注

0文章

300浏览量

23914

发布评论请先 登录

相关推荐

热点推荐

NVMe高速传输之摆脱XDMA设计43:如何上板验证?

1 所示。 外部接口主要有访问系统控制模块的ctrl_axi 接口, 进行数据传输的 data_axi 接口, 与 PCIe 引脚连接的 PCIe 接口, 以及时钟、 复位接口。 可选参数包括

发表于 10-30 18:10

NVMe高速传输之摆脱XDMA设计24: UVM 验证包设计

。

Axi4_lite_agent 负责对接 AXI4-Lite 接口。 在 DUT 使用的三个接口中, AXI4-Lite接口用于连接系统控制模块, 实现系统控制功能, 所以激励的添加主要通过 AXI4-Lite接口。 在

发表于 08-29 14:33

NVMe IP高速传输却不依赖XDMA设计之九:队列管理模块(上)

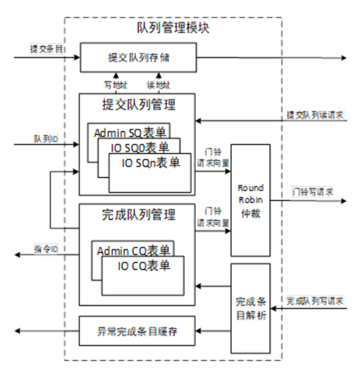

这是采用PCIe设计NVMe,并非调用XDMA方式,后者在PCIe4.0时不大方便,故团队直接采用PCIe设计,结合UVM验证加快设计速度。 队列管理模块采用队列的存储与控制分

NVMe IP高速传输却不依赖XDMA设计之八:系统初始化

采用XDMA是许多人常用xilinx库实现NVMe或其他传输的方法。但是,XDMA介绍较少,在高速存储设计时,尤其是PCIe4.0模式下,较

NVMe高速传输之摆脱XDMA设计之七:系统初始化

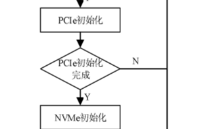

完成后, 可以进入 NVMe 初始化状态, NVMe 初始化也由用户通过系统控制模块启动。 当 NVMe 初始化正常完成后,

发表于 07-04 09:14

NVMe IP高速传输却不依赖XDMA设计之六:性能监测单元设计

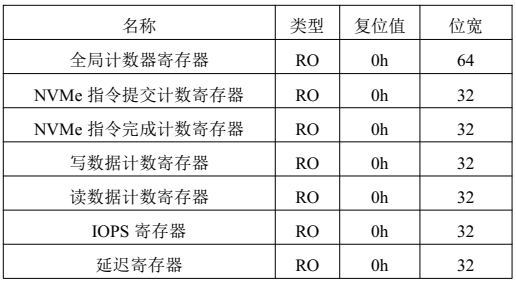

性能监测单元负责监测 NVMe over PCIe 逻辑加速引擎的运行状态和统计信息, 包括复位后

运行时间信息、 NVMe 指令数量统计信息、 数据操作数量统计信息、 IOPS 性能统计

信息、 指令延迟统计信息等。

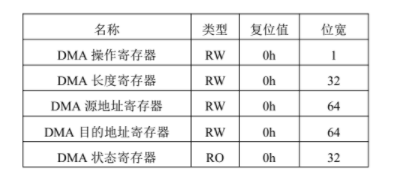

NVMe IP高速传输却不依赖XDMA设计之五:DMA 控制单元设计

DMA 控制单元负责控制 DMA 传输事务, 该单元承担了 DMA 事务到 NVMe 事务的转换任务, 使用户对数据传输事务的

发表于 07-02 19:45

NVMe IP高速传输摆脱XDMA设计之四:系统控制模块设计

系统控制模块负责实现 NVMe over PCI 逻辑加速引擎的控制功能, 其结构如图 1 所示。 用户通过系统控制

发表于 06-29 18:07

NVMe IP高速传输却不依赖XDMA设计之三:系统架构

所设计的新系统架构中,Nvme over PCIe IP通过 PCIe 3.0x4 接口连接 NVMe固态硬盘, 并提供 AXI4-Lite 接口用于

NVMe IP高速传输却不依赖便利的XDMA设计之三:系统架构

NVMe

固态硬盘, 并提供 AXI4-Lite 接口用于系统控制, 以及 AXI4 接口用于数据传输。 在该IP内部, 根据功能划分为系统控制

发表于 06-29 17:42

NVMe IP高速传输却不依赖XDMA设计之二:PCIe读写逻辑

应答模块的具体任务是接收来自PCIe链路上的设备的TLP请求,并响应请求。由于基于PCIe协议的NVMe数据传输只使用PCIe协议的存储器读请求TLP和存储器写请求TLP,应答模块分别

NVMe IP高速传输却不依赖XDMA设计之四:系统控制模块

NVMe IP高速传输却不依赖XDMA设计之四:系统控制模块

评论