文章来源:学习那些事

原文作者:小陈婆婆

本文介绍了SOI的器件类型、工作原理和制备技术。

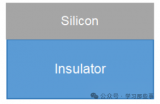

绝缘体上硅(SOI)技术作为硅基集成电路领域的重要分支,其核心特征在于通过埋氧层(BOX)实现有源层与衬底的电学隔离,从而赋予场效应晶体管独特的电学特性。

本文分述如下

SOI器件类型和工作原理

SOI器件与电路特性优势

SOI衬底材制备技术

SOI器件类型和工作原理

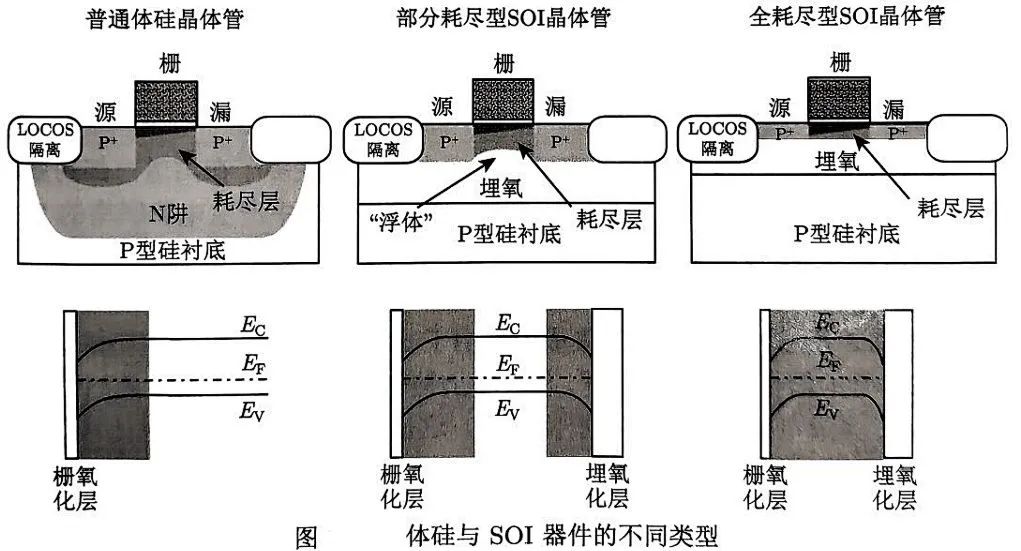

从器件维度分析,SOI技术可划分为部分耗尽(PD-SOI)与全耗尽(FD-SOI)两大类别,二者在结构设计与工作机理上呈现显著差异。

PD-SOI器件的有源层厚度较大,通常超过两倍最大耗尽层宽度(Tsi> 2Xdmax),其电势分布特性与体硅器件高度近似,背栅调制效应较弱,阈值电压的物理模型可沿用传统体硅器件的表达式,主要依赖顶栅电压对前沟道的控制。相比之下,FD-SOI器件的有源层厚度极薄(Tsi< 2Xdmax),在正向偏置下可实现全耗尽状态,形成前后双栅协同调控的独特机制,此时电势分布呈现前沟道与背沟道的强耦合效应,阈值定义需区分耗尽型与积累型两种工作模式。

当前SOI技术发展呈现两大趋势:其一,材料端突破持续深化,超薄硅膜(<10nm)与高k埋氧层的组合方案成为研究热点,法国CEA-Leti近期报道的12nm FD-SOI技术已实现0.7V低压下1.8GHz/mW的能效表现;其二,应用场景加速拓展,FD-SOI在射频前端、低功耗物联网及汽车电子领域展现显著优势。

SOI器件与电路特性优势

绝缘体上硅(SOI)技术凭借其独特的器件结构与工作模式,在电学性能、集成可靠性及环境适应性方面展现出显著优势。

从核心电学特性来看,SOI晶体管的埋氧层(BOX)将有源区与衬底完全隔离,这一结构带来双重效益:其一,源漏结深与结面积得到有效控制,显著降低短沟道效应及源漏寄生电容,从而提升电路工作频率与动态响应速度;其二,背栅电极的引入使阈值电压(VTH)具备动态调控能力,为低功耗电路设计提供了更高的灵活度,该特性在移动计算与物联网领域已得到广泛应用,例如AMD基于SOI工艺的CPU便通过背栅偏置技术实现了功耗与性能的优化平衡。

聚焦全耗尽型(FD-SOI)器件,其超薄有源层(Tsi< 2Xdmax)使沟道工作于全耗尽状态,静电势完整因子(EI)较体硅器件提升30%以上,有效抑制了阈值电压滚降(Roll-off)与漏致势垒降低(DIBL)效应,在亚10nm工艺节点下仍能维持优异的短沟道控制能力。

相比之下,部分耗尽型(PD-SOI)器件因有源层厚度较大,虽接近体硅器件的电学特性,但易引发浮体效应——多子在沟道区域的积累导致输出特性出现Kink现象,需通过体接触或掺杂优化进行抑制,该特性限制了其在高精度模拟电路中的应用。

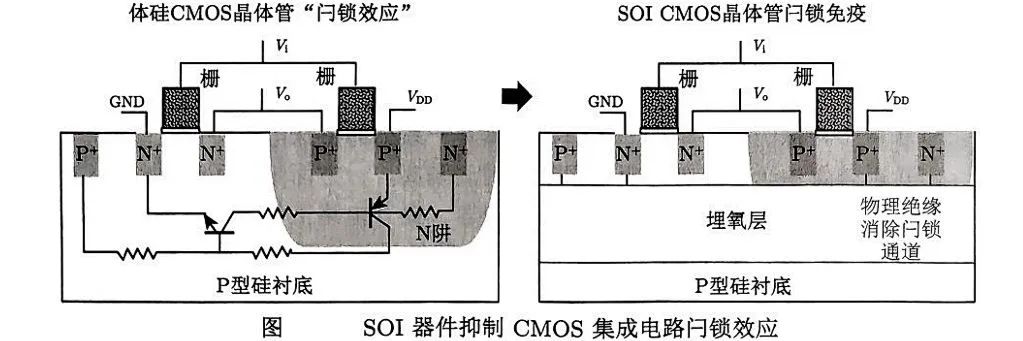

在CMOS集成层面,SOI技术的埋氧层阻断了寄生PNPN晶体管的形成路径,从根本上消除了体硅电路中常见的闩锁效应,显著提升了电路可靠性。

GlobalFoundries的22FDX工艺平台通过背栅偏置技术,实现了动态功耗调整功能,在2.5GHz工作频率下功耗较传统方案降低30%,该技术已成功应用于汽车电子与5G通信领域。

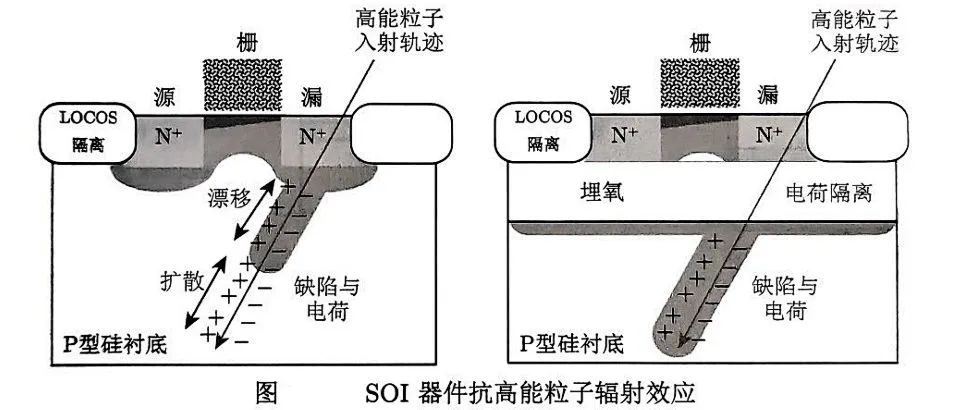

此外,SOI在抗辐射加固方面的优势尤为突出,埋氧层有效阻隔了高能粒子在衬底中产生的损伤电荷对表面沟道的影响,实验数据显示,SOI器件的单粒子翻转(SEU)敏感度较体硅器件降低两个数量级,该特性使其成为宇航级集成电路的首选方案,NASA最新一代星载处理器便采用SOI工艺实现了辐射环境下的高可靠性运行。

SOI衬底材制备技术

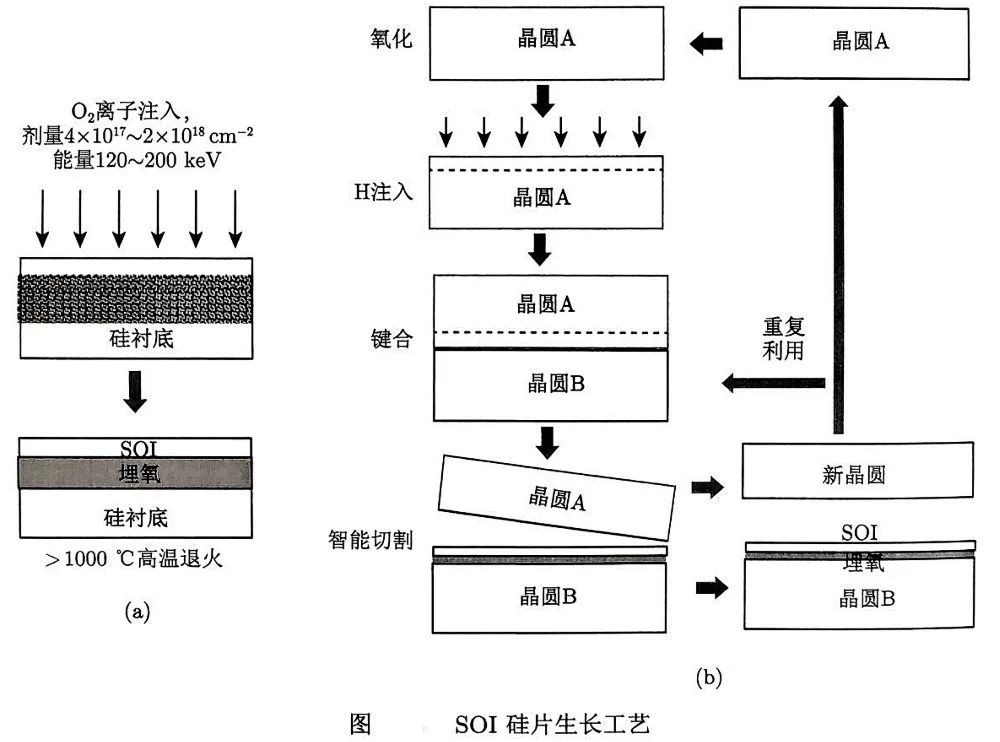

绝缘体上硅(SOI)衬底材料的制备技术因其独特的层状结构需求,需采用特殊工艺实现有源层与埋氧层(BOX)的精准构建,其技术复杂度与成本显著高于传统体硅晶圆。当前主流制备方案聚焦于注入埋氧(SIMOX)与智能键合转移(Smart-cut)两大技术路径,二者在工艺原理、材料特性及量产适用性上呈现差异化特征。

SIMOX技术由日本东芝公司于20世纪80年代率先开发,是首个实现规模化量产的SOI衬底制备方案。其核心工艺流程如下图(a),在普通硅衬底中高剂量注入氧离子(剂量需达5×10¹⁷ cm⁻²以上),随后通过高温退火促使注入氧原子与硅基体反应,形成连续的埋氧层。然而,该技术存在固有局限——氧离子注入的浓度分布呈高斯曲线特性,导致表面硅层与埋氧层之间形成较宽的过渡区(通常超过50nm),难以满足超薄全耗尽型(FD-SOI)器件对陡峭界面及精准厚度控制的需求。此外,高剂量氧注入易引发晶格损伤,虽可通过退火修复部分缺陷,但仍可能对材料电学性能产生微妙影响,限制了其在先进制程节点下的应用拓展。

相较之下,法国Soitec公司开发的Smart-cut技术通过氢离子注入与键合剥离机制,实现了SOI衬底的高质量制备。其工艺流程如上图(b):首先在供体硅片A表面生长氧化层作为隔离层,随后通过低剂量氢离子注入(剂量通常为5×10¹⁶~1×10¹⁷ cm⁻²)在硅基体内形成断裂层;将硅片A倒置与受体硅片B键合后,经热处理使氢注入层产生微裂纹,实现硅膜的精准剥离;最终通过化学机械抛光(CMP)对剥离后的硅膜进行平坦化处理,获得表面质量优异的SOI衬底。该技术的核心优势在于:氢注入剂量显著低于SIMOX的氧注入,大幅减少了晶格损伤;断裂层控制精准,表面硅层与埋氧层界面陡峭度可达纳米级(<10nm过渡区),特别适用于超薄FD-SOI晶圆的制备;此外,供体硅片A在剥离后可重复利用,显著降低了材料成本。目前,Smart-cut技术已成为全球SOI衬底量产的主流方案,支撑了从28nm到12nm节点的FD-SOI工艺开发。

-

集成电路

+关注

关注

5464文章

12695浏览量

375808 -

汽车电子

+关注

关注

3047文章

9129浏览量

173174 -

晶体管

+关注

关注

78文章

10443浏览量

148687

原文标题:SOI集成电路技术

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

绝缘体上硅有什么优点?

科学家在拓扑激子绝缘体相研究取得突破性进展

为什么在绝缘体中,光子会受到“拓扑保护”

首次在零磁场下实现了量子反常霍尔绝缘体的陈数调控

什么是拓扑绝缘体,它有没有可能替代硅

拓扑绝缘体材料有望成为硅替代品?

可再生能源触发可持续电绝缘体发展

探讨一下2D和3D拓扑绝缘体

微带线兼容的新型拓扑绝缘体结构:助力拓扑器件工程化

一文详解绝缘体上硅技术

一文详解绝缘体上硅技术

评论