根据Semico Research数据显示,2024年全球RISC-V芯片出货量突破100亿颗,中国出货量占比超过50%,预测到2025年,采用RISC-V架构芯片的出货量将增至624亿颗。2025年3月,国家发展和改革委员会发布的《国民经济和社会发展计划草案》中明确提出,要持续培育壮大新兴产业,促进开源指令集架构等新兴领域抢先突破。

当下,RISC-V 架构正朝着更加灵活多样和可定制化的方向发展,以适应不同应用场景。对于 EDA 而言,一方面,用于实现高性能计算的模块化扩展使得单元布局的拓扑关系复杂度呈指数级上升,这要求 EDA 工具能够快速适配异构架构特征;另一方面,为满足低功耗、高性能等场景下的差异化需求,EDA 工具需要在多重目标约束下实现 PPA(性能、功耗、面积)的协同优化。

结合了人工智能特性的新一代智能 EDA 工具正在成为突破 RISC-V PPA 瓶颈的有效手段。芯行纪智能布局规划工具 AmazeFP 基于机器学习引擎,为 RISC-V 芯片设计提供高度智能的拥塞感知、便捷的数据流分析和宏单元自动整理对齐功能,有效解决因寄生效应导致的时序违例,控制高活动率模块的局部功耗,动态调整单元密度,最终实现更优化的 PPA。

案例1

在高利用率面积约束下实现频率突破

案例一为约两百万标准单元规模的RISC-V设计,在该案例中,客户的难点在于后端设计如何才能在高利用率的面积约束下,实现频率的突破,充分发挥出核的性能。

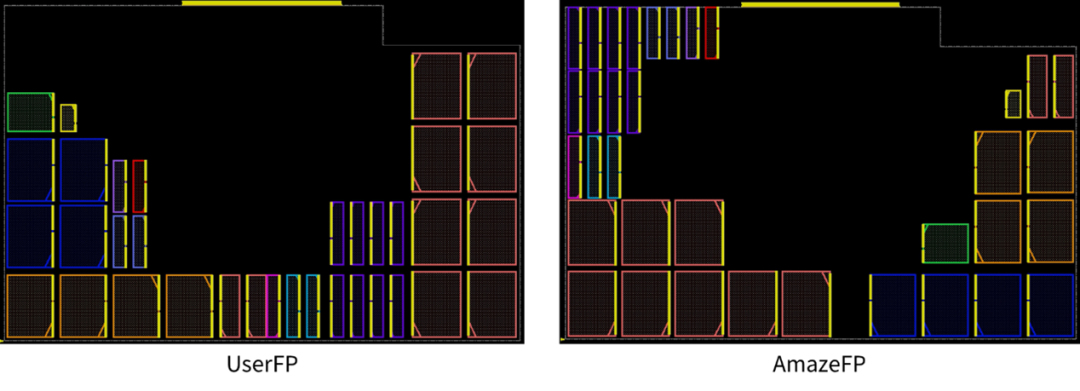

图一:User手工摆放的布局方案vs AmazeFP全自动的布局方案

如图一显示,AmazeFP在不到2个小时的时间里,为客户提供了全新的布局策略。经过重新布局,原来用户布局方案下的关键路径违例降低了46.2%,整体违例降低了81.9%,频率提升4.3%(见表一)。

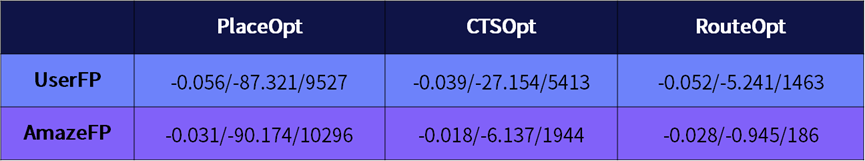

表一:UserFP和AmazeFP在P&R各阶段的QoR数据对比

在整个后端实现的流程中,AmazeFP的布局方案优势逐步提升,最终受益巨大。

案例2

工作频率、面积、功耗的优化提升

案例二是客户用于重点评估RISC-V在当前工艺节点下PPA优化效果的模块,希望能够借助AmazeFP的数据流驱动和AutoPack(自动对齐)带来面积、功耗、特别是工作频率的提升。AmazeFP仅用了半小时左右的时间完成了Macro的摆放和自动对齐。

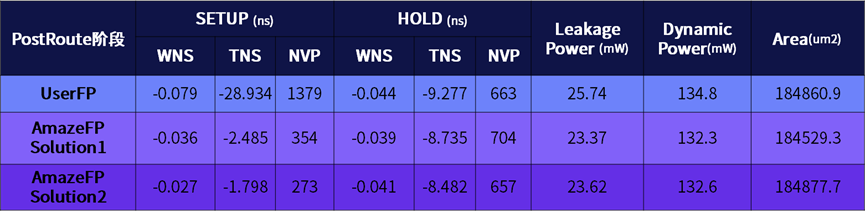

表二:UserFP和AmazeFP在PostRoute阶段的PPA数据对比

从表二可以看出,相较于用户花费数周、经过多轮 P&R(布局布线)迭代调整的布局规划方案,AmazeFP 的两个模式——Mixed(混合)和 Peripheral(外设)下提供的方案在关键路径的时序上平均有 60.1% 的提升,有效帮助用户克服了该模块最关注的频率“瓶颈”。更合理的 Macro 分布驱动下的 Module(模块)分布,同样带来了 92.6% 的 Setup TNS 优化。与此同时,在整体功耗和面积方面,也分别实现了 2.9% 和 0.1% 的改善。

通过以上 AmazeFP 的案例可见,将机器学习算法深度嵌入布局规划工具或其他数字实现 EDA 工具,可大幅提升 RISC-V 芯片的 PPA 协同优化效率,从而显著缩短芯片开发周期,真正实现芯片质量和设计效率的跨越式提升。随着 RISC-V 的多样化需求不断增加,RISC-V 与电子设计自动化工具(EDA)的协同发展变得愈加重要。芯行纪致力于自主研发数字实现 EDA 软件,为加快 RISC-V 的生态发展贡献力量。

关于芯行纪

芯行纪科技有限公司(简称“芯行纪”)成立于2020年,是一家专注于数字实现EDA方案的高新技术创新企业。公司汇聚电子设计自动化与芯片设计领域顶尖人才,在国内率先将机器学习和分布式计算技术深度应用于数字实现EDA领域,凭借卓越的研发实力构建起持续进化的自主数字实现EDA工具平台。

芯行纪数字实现EDA产品矩阵涵盖多款创新工具,包括国内首款全自研数字布局布线工具AmazeSys、智能布局规划工具AmazeFP、智能布局规划机器学习方案AmazeFP-ME、一站式工程修复优化工具AmazeECO、快速DRC & DFM收敛工具AmazeDRCLite,以及工业软件许可文件管理系统Industriallm。

目前,芯行纪自主研发的EDA产品已广泛应用于国内头部芯片设计和制造企业,累计服务近40家客户,覆盖人工智能、智慧汽车、5G、云计算等众多新一代信息技术产业,赋能集成电路产业高速发展。

-

芯片

+关注

关注

463文章

54463浏览量

469562 -

eda

+关注

关注

72文章

3148浏览量

183818 -

时序

+关注

关注

5文章

411浏览量

39015 -

RISC-V

+关注

关注

49文章

2954浏览量

53572

原文标题:AmazeFP:赋能RISC-V芯片迈向卓越PPA表现

文章出处:【微信号:gh_2894c3fc5359,微信公众号:芯行纪】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

中移芯昇与新讯集团强强联合 共筑RISC-V芯片产业全球新生态

智芯公司RISC-V强实时CPU芯片通过赛西实验室权威检测

新思科技全栈工具链助力RISC-V设计高效进阶

智芯公司荣膺2025“中国芯”RISC-V生态推广示范案例

芯昇科技获第二十届“中国芯”RISC-V生态推广示范案例奖

喜讯|昊芯RISC-V DSP荣获“中国芯”RISC-V生态推广奖

直播预约 |开源芯片系列讲座第30期:“一生一芯”计划——从零开始设计自己的RISC-V处理器芯片

芯新闻|昊芯亮相第五届RISC-V中国峰会,共绘开源芯片新纪元

普华基础软件亮相2025 RISC-V中国峰会

灿芯半导体亮相2025 RISC-V中国峰会

思尔芯邀您共赴2025 RISC-V中国峰会!

芯行纪智能布局规划工具AmazeFP助力RISC-V芯片设计

芯行纪智能布局规划工具AmazeFP助力RISC-V芯片设计

评论