引言

随着半导体工艺不断向深纳米节点迈进,混合信号集成电路的重要性愈发显著。从低功耗移动设备到高性能计算系统,众多关键模块如双倍数据速率存储器(DDR)、物理层接口(PHY)、通用串行总线(USB)、锁相环(PLL)、低压差稳压器(LDO)、数模转换器(ADC)等IP,已经被广泛应用于各类系统中。这些IP的性能随着工艺波动影响显著,在先进工艺及多电压、温度(PVT)条件下更为明显。如何实现高效且精准地IP特征化(IP Characterization),已成为确保芯片整体性能的关键挑战。

然而,传统蒙特卡洛(Monte Carlo)仿真方法因其依赖海量SPICE仿真样本进行统计分析,面临计算资源消耗巨大和收敛速度慢的瓶颈,已无法满足这一需求。随着工艺节点的演进,在人工智能芯片、高性能计算、无人驾驶等应用场景中,芯片设计对时序模型精度的要求日益严苛。如何实现“高精度”与“高效率”的平衡,并快速完成时序建模,成为亟待突破的核心问题。华大九天新一代混合信号电路IP模块特征化提取工具——Empyrean Liberal IP,支持快速生成符合LVF(Liberty Variation Format)格式的标准库文件,为混合信号IP模块特征化提供高效、精准的解决方案。

Liberal IP的LVF K库创新

LVF是集成电路单元库特征化提取中的关键标准模型,用于描述制造工艺偏差对电路时序性能的影响。其核心包含两部分:

OCV sigma模型:基于偏斜高斯分布,通过前后两个正态分布的标准差(early/late)刻画时序偏差。

Moment-based模型:支持非对称、偏置或非高斯分布,精准捕获超低电压场景下时序变化的复杂形态。

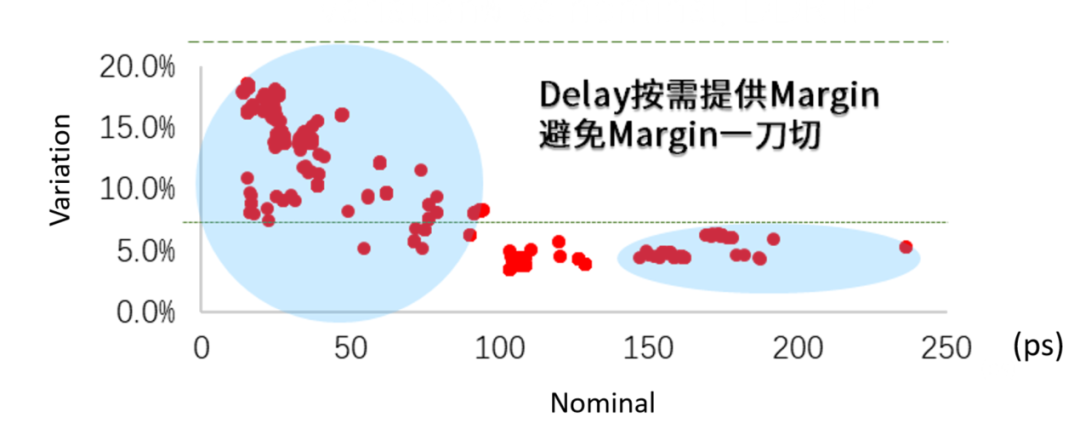

传统的Margin 设置采用“一刀切”模式,难以兼顾不同场景的差异化需求。而 LVF方案能够根据不同需求精准提供Margin,如下图所示:正常Nominal延迟在50ps以内,控制误差在正常变化(Nominal Variation)的10%~20%以内;当正常Nominal延迟超过100ps以后,误差设置为Nominal Variation的5%以内。这种LVF模型方案能够有效规避添加统一Margin而导致的时序约束过松(乐观)或过紧(悲观)的问题,实现精细化的时序管理,助力芯片设计在性能与可靠性之间达到平衡。

Liberal IP LVF K库基于华大九天自主研发的Accurate LVF快速精准建库技术,通过三大核心技术突破,重塑LVF建模流程:

灵敏度分析法:直接定位影响时序的关键参数,仿真次数降低 90% 以上。

智能参数过滤:基于相关性分析筛选器件的关键统计参数,避免冗余计算。

模块划分技术: 通过模块划分,把LVF的仿真缩小为一个个微型仿真,提高仿真效率,进一步压缩建库时间。

通过上述Liberal IP LVF K库方法,K库的构建效率得到了极大提升。以具体案例说明,如果目标是在3天内完成含有50个PVT的单元K库构建,采用华大九天的创新技术,其效率相比采用传统的蒙特卡洛方法可实现100倍效率提升!这意味原本可能需要数周甚至数月的复杂仿真任务,现在可以被压缩到极短周期内高质量完成。同时,该技术显著降低了资源消耗,大幅提高了工作效率。

Liberal IP的LVF K库核心优势

1高效建模

相较于传统的蒙特卡洛法,需要数万次的仿真次数,Liberal IP LVF K库可以减少90%以上仿真量,性能提升高达100倍。这一突破性进展使在同等时间和资源条件下,可完成的特征化建库任务量实现数量级提升,从而显著加速设计周期,为设计企业带来效率与成本的双重优化。

2精准覆盖

即使在复杂的非高斯分布场景和时序要求严苛的超低电压环境下,Liberal IP仍能保持卓越性能。相较于依赖海量样本的传统蒙特卡洛方法,该工具能直接捕捉 ±3σ 边界性能,并支持自定义 Sigma Level,其时序预测精度误差率可控制在 1% 以内。这种高精度建模能力为芯片设计提供了强有力的支撑,确保其在各种极端条件下的稳定表现,显著提升了芯片的可靠性与市场竞争力。

| 项目 | 传统蒙特卡洛方法(MC) |

Liberal IPLVF K库 |

| 仿真次数 | 数万次/单元 | 减少90%以上 |

| 建模精度 |

依赖大量样本 来保障建模精度 |

直接捕捉±3σ边界性能,可自定义不同的sigma level |

| 样本量 |

样本量跟仿真次数成正比 非常难达成10万次+仿真 |

支持10万次+样本量 |

3广泛兼容

在实际应用中,Liberal IP LVF K库显示出极高的工具链兼容性,可轻松适配主流EDA环境。用户仅需通过一条简单命令,即可一键生成LVF库文件,广泛兼容现有设计流程,能够被数字后端(包括时序分析,逻辑综合,布局布线等)工具直接使用。这一特性显著降低了技术整合成本,让高效设计触手可及。

客户案例分享

某国际知名领先企业在其先进工艺节点的研发过程中遭遇严峻的时序收敛挑战。在传统模型下,芯片高频运行时频繁出现时序违规,过度的Margin设计会导致显著的芯片性能折损。在引入 Liberal IP LVF K 库之后,时序情况得到了显著改善。

| Slackwith Margin |

Slack with LVF |

Slack Gain | |

|

建立时间 (Setup Time) |

-320ps | -261ps | 59ps |

|

保持时间 (Hold Time) |

-77ps | -61ps | 16ps |

建立时间(Setup Time):原始添加统一Margin方法,传统模型方法的时序裕度Slack是 -320ps,而采用 LVF 后Slack提升至 -261ps,建立时间收益达到 59ps,这意味着时序建立过程更加稳定,为芯片高频运行奠定了坚实基础。

保持时间(Hold Time):传统方法统一添加Margin,时序裕度为 -77ps,而采用 LVF 后Slack变为 -61ps,保持时间收益为 16ps,有效优化了时序保持特性,降低了数据保持阶段的潜在风险。

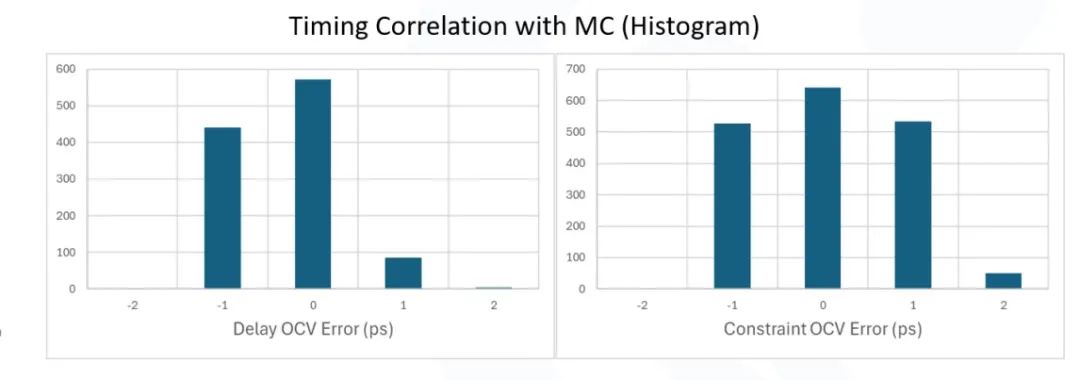

综上两个方面,其在保证芯片安全的前提下,LVF方法在建立时间和保持时间方面均获得了时序收益,为芯片的整体竞争力奠定了坚实基础。 进一步将Liberal IP LVF K库结果与传统蒙特卡洛方法所得结果的精度进行对比,LVF时序精度和蒙特卡洛结果高度契合。在延时片上偏差(Delay OCV)和约束片上偏差(Constraint OCV)方面,LVF和蒙卡的精度差异大部分集中分布在 ±1ps 区间内(对应柱状图峰值区域),整体时序精度偏差严格控制在2ps以内,充分验证了LVF模型的高精准度。Liberal IP在大幅提升建库效率的同时,仍能达到蒙特卡洛方法的精度水平,为芯片设计提供了高效精准的时序支撑。

基于Liberal IP在时序精度与性能方面的显著提升,客户已决定将其全面导入设计流程。这一决策不仅是对该工具技术实力的高度认可,更标志着客户在芯片设计流程革新上迈出了关键一步。目前,客户已成功推出高性能芯片产品,凭借该工具带来的时序优势,在市场竞争中抢占了性能与上市时间先机。

结语

作为中国EDA行业的领军企业,华大九天致力于成为全流程、全领域、全球领先的EDA提供商。Empyrean Liberal IP特征化提取LVF K库工具凭借“高效、精准”等核心特点,再次彰显了华大九天在EDA领域的深厚技术积累和创新能力。未来,华大九天期待与更多集成电路设计企业携手合作,共同应对混合信号电路特征化的挑战,推动整个行业的持续进步与发展,携手开创更加美好的未来。

北京华大九天科技股份有限公司(简称“华大九天”)成立于2009年,一直聚焦于EDA工具的开发、销售及相关服务业务,致力于成为全流程、全领域、全球领先的EDA提供商。

华大九天主要产品包括全定制设计平台EDA工具系统、数字电路设计EDA工具、晶圆制造EDA工具、先进封装设计EDA工具和3DIC设计EDA工具等软件及相关技术服务。其中,全定制设计平台EDA工具系统包括模拟电路设计全流程EDA工具系统、存储电路设计全流程EDA工具系统、射频电路设计全流程EDA工具系统和平板显示电路设计全流程EDA工具系统;技术服务主要包括基础IP、晶圆制造工程服务及其他相关服务。产品和服务主要应用于集成电路设计、制造及封装领域。

华大九天总部位于北京,在南京、成都、深圳、上海、香港、广州、北京亦庄、西安和天津等地设有全资子公司,在武汉、厦门、苏州等地设有分支机构。

-

锁相环

+关注

关注

36文章

637浏览量

91300 -

混合信号

+关注

关注

0文章

542浏览量

65935 -

芯片设计

+关注

关注

15文章

1172浏览量

56780 -

eda

+关注

关注

72文章

3143浏览量

183768 -

华大九天

+关注

关注

5文章

120浏览量

13954

原文标题:混合信号芯片设计革命:Liberal IP通过LVF精准K库实现性能全面跃升

文章出处:【微信号:华大九天,微信公众号:华大九天】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

华大九天Liberal IO精准K库解决方案介绍

华大九天PyAether智能体工具Aether Coder正式上线

华大九天与西安电子科技大学签署战略合作协议

首期基于华大九天EDA工具的Mini MPW流片专项学习交流会圆满落幕

华大九天与海光信息达成战略合作

华力创通助力“九天”无人机完成首飞

获大湾区基金和华大九天投资,思尔芯迈入国产EDA发展新征程

获大湾区基金和华大九天投资,思尔芯迈入国产EDA发展新征程

华大九天:AI、并购、反内卷,国内EDA工具全流程更进一步

2025华大九天生态伙伴及用户大会圆满举行

华大九天新一代全定制IC设计平台Empyrean Aether介绍

华大九天“芯聚九天”系列活动助力集成电路产业蓬勃发展

华大九天Empyrean Liberal工具助力数字集成电路设计

华大九天Empyrean Liberal IP驱动混合信号芯片设计革命

华大九天Empyrean Liberal IP驱动混合信号芯片设计革命

评论